## QC8051 Soft Core

# Real-Time Development Kit For **ALTERA Cyclone** \* FPGAs

#### Features and Benefits

- □ Implement custom 8051 designs in an ALTERA Cyclone FPGA (EP1C6T144C8) using FREE Quartus\* II Web Edition Software and QuickCores QC8051 Real-Time Development Kit

- □ Compatible with Keil Software μVision2\*\* debugger and C compiler

- Includes QuickCores small memory model (2K program reach) synthesizable QC8051 netlist library (compatible with Quartus II)

- □ Includes BoxView\*\*\* real-time "C" language debugger for QuickCores QC8051

- □ Includes target board with Cyclone EP1C6 installed

- On-board USB 1.1 controller does the following:

- Programs the Cyclone configuration ROM

- JTAG boundary scan controller (SAMPLE/PRELOAD monitoring)

- JTAG real-time monitor/debugger interface

- □ 128KB (150ns) external flash memory for program/data storage

- □ Dual 12-bit Digital-to-Analog converters (Burr-Brown DAC7512)

- □ Dual-channel 8-bit Analog-to-Digital Converter (MAX1108)

- □ 2-line X 16 character LCD

- □ 4 user buttons & 8 user LEDs

- RS-232 interface for user applications

- QuickCores QC8051 features:

- Pipeline architecture allows most instructions execute in a single clock cycle

- o Customizable user SFR block

- Real-time monitor architecture allows monitoring of internal operations without the use of embedded software routines via JTAG connection

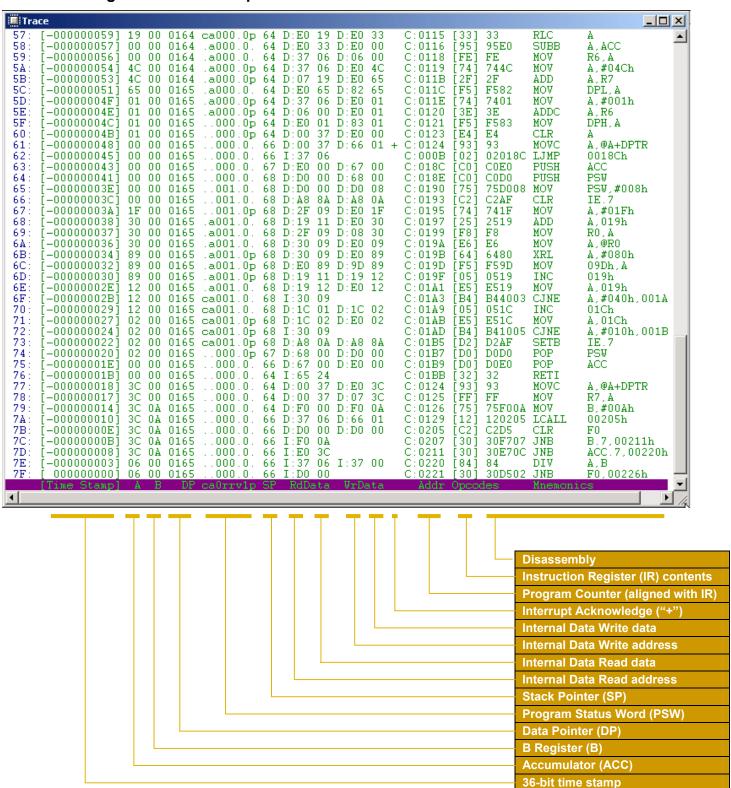

- Debug logic includes 128-sample deep X 144-channel real-time trace buffer

- Traces 36-bit time stamp, PC, Instruction Register, PSW, SP, ACC, B, DP, Data RD address/data, Data WR address/data, interrupt acknowledge

- Unlimited software breakpoints

- Up to three hardware breakpoints

## **General Description**

When used with ALTERA's free Quartus II Web Edition software, QuickCores Q8051 Real-Time Development Kit allows you to quickly create and debug custom 8051 designs in an ALTERA Cyclone FPGA. The kit includes QuickCores small memory model QC8051 softcore, BoxView C language debugger which is compatible Keil Software 8051 C compiler and  $\mu Vision2$  IDE, target board and power supply. Example top level 8051 references design programming files are also included. Large memory model QC8051 netlist library is available under a separate license.

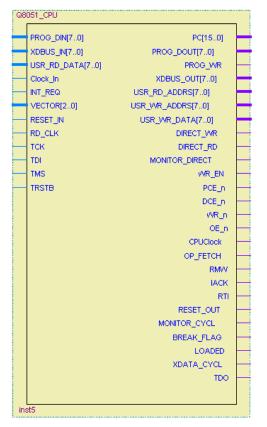

## QC8051 CPU Module Signal Descriptions (instantiated at top level of your design)

| Name              | Dir | Description                                                                                    |

|-------------------|-----|------------------------------------------------------------------------------------------------|

| PROG_DIN[7:0]     | I   | QC8051 program instruction bus input                                                           |

| PROG_DOUT[7:0]    | 0   | QC8051 program write bus used by real-time monitor program write cycles                        |

| PROG_WR           | 0   | Indicates program write during real-time monitor program write cycles                          |

| XDBUS_IN[7:0]     | I   | QC8051 external data bus input                                                                 |

| XDBUS_OUT[7:0]    | 0   | QC8051 external data bus output                                                                |

| PCE_n             | 0   | Active low external program memory chip enable                                                 |

| DCE_n             | 0   | Active low external data memory chip enable                                                    |

| OE_n              | 0   | Active low external program/data output enable                                                 |

| WR_n              | 0   | Active low external program/data write enable                                                  |

| USR_RD_ADDRS[7:0] | 0   | User SFR read address                                                                          |

| USR_WR_ADDRS[7:0] | 0   | User SFR write address                                                                         |

| USR_RD_DATA[7:0]  | I   | User SFR read data bus                                                                         |

| USR_WR_DATA[7:0]  | 0   | User SFR write data bus                                                                        |

| DIRECT_WR         | 0   | 1 = internal data memory "direct" write cycle                                                  |

| DIRECT_RD         | 0   | 1 = internal data memory "direct" read cycle                                                   |

| MONITOR_DIRECT    | 0   | 1 = internal monitor data memory direct read cycle                                             |

| WR_EN             | 0   | 1 = internal data memory write enable                                                          |

| Clock_In          | I   | External clock input                                                                           |

| CPUClock          | 0   | CPU clock output                                                                               |

| MODE              | I   | 1 = CPU clock = Clock_In / 1; 0 = CPU clock = Clock_In / 4 (use this for external interfacing) |

| OP_FETCH          | 0   | 1 = opcode fetch cycle                                                                         |

| RMW               | 0   | 1 = read-modify-write cycle                                                                    |

| IACK              | 0   | 1 = intrerrupt acknowledge cycle                                                               |

| INT_REQ           | I   | 1 = interrupt request                                                                          |

| VECTOR[2:0]       | I   | Bits [5:3] of the interrupt vector loaded into the program counter                             |

| RESET_IN          | I   | 1 = reset                                                                                      |

| RESET_OUT         | 0   | 1 = reset; this signal internally gated by JTAG debug module                                   |

| MONITOR_CYCL      | 0   | 1 = monitor cycle                                                                              |

| XDATA_CYCL        | 0   | 1 = MOVX instruction; used by memory expansion circuit                                         |

| TCK               | I   | JTAG TCK input                                                                                 |

| TDI               | I   | JTAG TDI input                                                                                 |

| TMS               | I   | JTAG TMS input                                                                                 |

| TRST_n            | I   | JTAG TRST_n input                                                                              |

| TDO               | 0   | JTAG TDO output                                                                                |

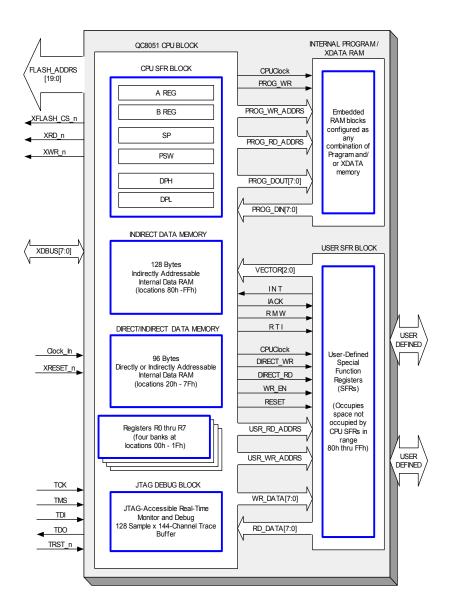

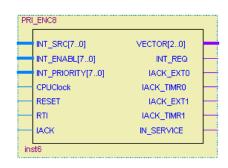

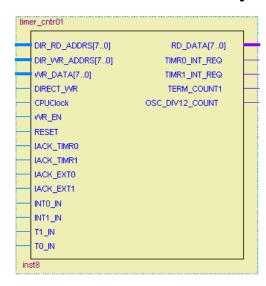

## QC8051 Real-Time Development Kit Netlist Library Top-Level Instantiation Symbols

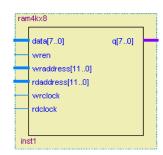

Various Size RAM Blocks for Program / Data Storage

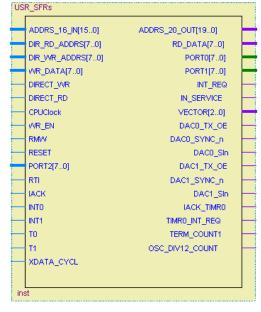

User-Definable SFR Block

Q8051 CPU (2K Memory Model)

## User-Definable Special Function Register Block Symbols Included in QC8051 Netlist Library

DAC7512 Serial Controller Port

Interrupt Controller Block

Note: Other modules not shown include general purpose parallel port and external program / data memory extended address banking module. Large Memory Model Q8051 CPU and serial port available under separate license.

**Dual 16-Bit Counter/ Timer Module**

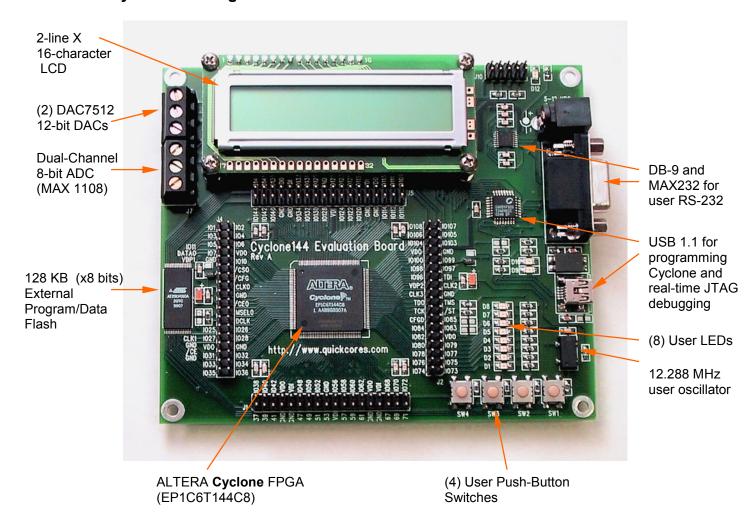

#### QuickCores Cyclone144 Target Board

#### **Cyclone144 Target Board Description**

The QuickCores QC8051 Real-Time Development Kit includes the Cyclone144 Target Board pictured above. Programming the Cyclone configuration ROM is through the on-board USB 1.1 ("mini-B") interface. Once the configuration ROM is programmed with the desired QC8051 design, the implemented QC8051 design user application software can be programmed and debugged using the same USB interface. JTAG boundary scan (SAMPLE/PRELOAD) monitoring of the Cyclone device pins is also by way of the USB interface.

Provided on the Cyclone144 Target Board for your use are 128 Kbytes (x8 bits) external flash memory, RS-232 interface, 2-line X 16-character LCD, four user buttons, two Burr-Brown 12-bit digital-to-analog converters (DAC7512s), one dual-channel Maxim IC 8-bit analog-to-digital converter (MAX1108), eight LEDs, and 12.288 MHz oscillator.

Although the QuickCores QC8051 Real-Time Development Kit includes the small (2k-reach) memory model QC8051 netlist library which you can use to create your own designs, the Cyclone144 Target Board is shipped with a large memory model QC8051 programmed into the Cyclone configuration ROM and on CD.

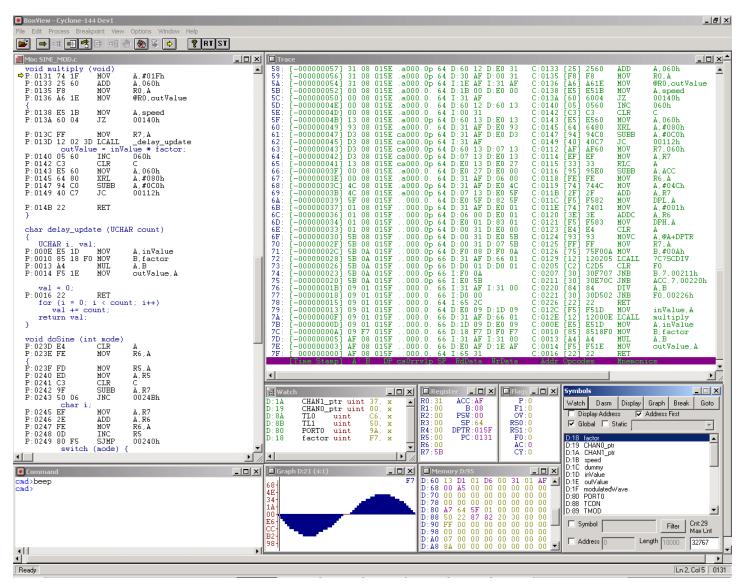

## **BoxView C Language Real-Time Debugger**

#### BoxView Real-Time C Language Debugger Key Features

- Built-in "SRunner" driver for programming Cyclone configuration ROM via on-board USB

- Real-time trace buffer displays 36-bit time stamp, ACC, B, DP, PSW, SP, Data RD address and data, Data WR address and data, PC and Instruction Register contents

- Supports concurrent and remote monitoring and debugging of multiple CPUs

- Code window with source, mixed or assembly display mode

- "Symbols" widow allows you to quickly set breakpoints, disassemble, or watch

- Multiple memory windows for data, code, indirect, or external locations

- Graphic display of any memory region allows animation in real-time mode

- On-the-fly monitoring and editing of registers and memory

- Robust JTAG command and scripting language with data logging for automated testing

#### QC8051 Debug Module 128 Sample X 144-Channel Real-Time Trace Buffer

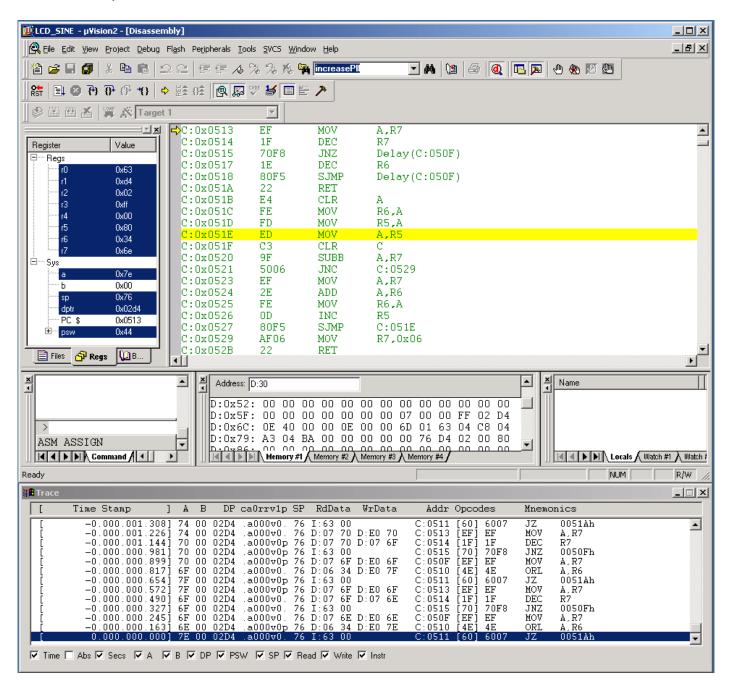

## Keil Software μVision2 IDE Supports QuickCores QC8051 Soft Core

#### Keil Software μVision2 IDE Key Points

- Provided with the QC8051 Real-Time Development Kit are the appropriate .dlls which will allow seamless operation with Keil Software μVision2 IDE and C51 compiler

- Concurrent real-time monitoring and debug of multiple CPUs is supported when μVision2 IDE is used in combination with Domain Technologies BoxServer and BoxView Debugger

- The QC8051 real-time trace buffer is supported under μVision2 "Peripherals" menu item

### QC8051 Real-Time Development Kit Contents

The QC8051 Real-Time Development Kit comes with the following items:

- Cyclone 144 target board with Cyclone EP1C6-T144C8 installed and configuration ROM preprogrammed with large memory model QC8051 microcontroller

- BoxView real-time C language debugger with integral SRunner configuration device programmer/driver

- QuickCores small (2k program reach) memory model netlist library targeted to Cyclone FPGAs and restricted for use with Quartus II

- 9-volt power supply and "mini-B" USB cable

- Target board schematics

- User Guide

- Example large memory model QC8051 top-level and user SFR designs in Verilog and compiled .rpd file format

- Required dlls for use with Keil Software μVision2 IDE

#### **QuickCores Design Services**

Along with its microcontroller IP, QuickCores also offers non-recurring engineering (NRE) design services to assist customers with integrating QuickCores microcontroller IP into their designs. This service is available on a quotation basis. Other services include development of custom application software, both on the host PC side and on the target embedded application side.

#### **Ordering Information**

QC8051 Real-Time Development Kit part number (small memory model): QC8051-RTDK-CYCL-S

#### **Contact Information:**

QuickCores IP 811 E. Plano Parkway, Suite 115

Plano, Texas 75074 Tel: (972) 578 1121 Fax: (972) 578 1086

Email: sales@quickcores.com

## **Discount Coupon**

Purchase a QuickCores QC8051 Real-time Development Kit (small memory model) before December 1, 2003 and receive 25% off the list price of \$595.

© 2003 QuickCores IP, all rights reserved. \*ALTERA, Cyclone and Quartus are registered trademarks of Altera Corperation. \*\*Keil C51 and  $\mu$ Vision is a trademarks of Keil Elektronik GmbH. \*\*\*BoxView and BoxServer are trademarks of Domain Technologies, Inc. QuickCores is a trademark of QuickCores IP.