# Verilog® HDL

# **Quick Reference Guide**

based on the Verilog-2001 standard (IEEE Std 1364-2001)

by

Stuart Sutherland

# SUTHERLAND H<sub>DL</sub>

www.sutherland-hdl.com

Copyright © 2001, Sutherland HDL, Inc., all rights reserved.

Permission is granted by Sutherlaand HDL to download and/or print the PDF document containing this reference guide from www.sutherland-hdl.com for personal use only. The reference guide may not be used for commercial purposes or distributed in any form or by any means without obtaining express permission from Sutherland HDL.

# Verilog<sup>®</sup> HDL Quick Reference Guide

based on the Verilog-2001 standard (IEEE Std 1364-2001)

by Stuart Sutherland

published by

# SUTHERLAND H<sub>D</sub>L

Sutherland HDL, Inc. 22805 SW 92<sup>nd</sup> Place Tualatin, OR 97062 (503) 692-0898

www.sutherland-hdl.com

Copyright © 1992, 1996, 2001 by Sutherland HDL, Inc. All rights reserved. No part of this book may be reproduced in any form or by any means without the express written permission of Sutherland HDL, Inc.

Sutherland HDL, Inc. 22805 SW 92nd Place Tualatin, OR 97062-7225

Phone: (503) 692-0898

URL: www.sutherland-hdl.com

ISBN: 1-930368-03-8

$\mathsf{Verilog}^{\circledR}$  is a registered trademark of Cadence Design Systems, San Jose, CA.

# VERILOG HDL QUICK REFERENCE GUIDE

| Table | of | Contents |  |

|-------|----|----------|--|

|-------|----|----------|--|

| 1.0  | New Features In Verilog-2001            | . 1 |

|------|-----------------------------------------|-----|

| 2.0  | Reserved Keywords                       | . 2 |

|      | Concurrency                             |     |

|      | Lexical Conventions                     |     |

|      | 4.1 Case Sensitivity                    |     |

|      | 4.2 White Space Characters              |     |

|      | 4.3 Comments                            |     |

|      | 4.4 Attributes                          |     |

|      | 4.5 Identifiers (names)                 |     |

|      | 4.6 Hierarchical Path Names             |     |

|      | 4.7 Hierarchy Scopes and Name Spaces    |     |

|      | 4.8 Logic Values                        |     |

|      | 4.9 Logic Strengths                     |     |

|      | 4.10 Literal Real Numbers               |     |

|      | 4.11 Literal Integer Numbers            |     |

| 5.0  | Module Definitions                      |     |

| 5.0  | 5.1 Module Items                        |     |

|      | 5.2 Port Declarations                   |     |

| 6.0  | Data Type Declarations                  |     |

| 0.0  | 6.1 Net Data Types                      |     |

|      | 6.2 Variable Data Types                 |     |

|      | 6.3 Other Data Types                    |     |

|      | 6.4 Vector Bit Selects and Part Selects |     |

|      | 6.5 Array Selects                       |     |

|      | 6.6 Reading and Writing Arrays          |     |

| 7.0  | Module Instances                        |     |

|      | Primitive Instances                     |     |

|      | Generate Blocks                         |     |

|      | Procedural Blocks                       |     |

| 10.0 | 10.1 Procedural Time Controls           |     |

|      | 10.2 Sensitivity Lists                  |     |

|      | 10.3 Procedural Assignment Statements   |     |

|      | 10.4 Procedural Programming Statements  |     |

| 11.0 | Continuous Assignments                  | 27  |

|      | Operators                               |     |

|      | Task Definitions                        |     |

|      | Function Definitions                    |     |

|      | Specify Blocks                          |     |

| 15.0 | 15.1 Pin-to-pin Path Delays             |     |

|      | 15.2 Path Pulse (Glitch) Detection      |     |

|      | 15.3 Timing Constraint Checks           |     |

| 16.0 | User Defined Primitives (UDPs)          |     |

|      | Common System Tasks and Functions       |     |

|      | Common Compiler Directives              |     |

|      | Configurations                          |     |

| 20.0 | Synthesis Supported Constructs          | 44  |

| _0.0 | Symmetry Supported Compared             |     |

# 1.0 New Features In Verilog-2001

Verilog-2001, officially the "IEEE 1364-2001 Verilog Hardware Description Language", adds several significant enhancements to the Verilog-1995 standard.

- Attribute properties (page 4)

- Generate blocks (page 21)

- Configurations (page 43)

- Combined port and data type declarations (page 8)

- ANSI C style port definitions (page 8)

- Arrays of net data types (page 11)

- Multidimensional arrays (page 11, 13)

- Variable initialization with declaration (page 13)

- Bit and part selects of array words (page 16)

- Indexed vector part selects (page 16)

- Explicit in-line parameter passing (page 17)

- Comma separated sensitive lists (page 24)

- Combinational logic sensitivity wild card (page 24)

- Inferred nets with any continuous assignment (page 28)

- Power operator (page 29)

- Signed arithmetic extensions (page 7, 9, 11, 13, 29, 32, 38)

- ANSI C style task/function I/O definitions (page 31, 32)

- Re-entrant tasks (page 31)

- Recursive functions (page 32)

- Constant functions (page 32)

- On-detect pulse detection (page 34)

- Negative pulse detection (page 34)

- Negative timing constraints (page 35)

- New timing constraint checks (page 35)

- Enhanced file I/O (page 39)

- Enhanced testing of invocation options (page 39)

- Enhanced conditional compilation (page 41)

- Disabling of implicit net declarations (page 41)

#### 2.0 Reserved Keywords

always ifnone and assign initial automatic<sup>†</sup> instance<sup>†</sup> begin inout buf input bufif0 integer bufif1 join case large liblist<sup>†</sup> casex localparam† casez cell macromodule cmos medium config<sup>†</sup> module deassign nand default negedge defparam nmos design† nor disable not noshowcancelled edge else notif0 end notif1

endcase orendconfiq<sup>†</sup> output endfunction parameter endgenerate<sup>†</sup> pmos endmodule posedge primitive endprimitive endspecify pull0 endtable pull1 endtask pulldown event pullup for pulsestyle\_onevent<sup>†</sup> pulsestyle\_ondetect force

force pulsesty forever rcmos fork real function generate genvar release highz0 repeat highz1 rnmos

rpmos rtran rtranif0 rtranif1 scalared signed

signed showcancelled† small specify specparam strength strong0 strong1 supply0

supply1 table task time tran tranif0 tranif1 tri tri0 tri1 triand trior trireg unsigned use vectored wait wand weak0 weak1 while wire wor

xnor

xor

#### 3.0 Concurrency

The following Verilog HDL constructs are independent processes that are evaluated concurrently in simulation time:

- module instances

- primitive instances

- continuous assignments

- · procedural blocks

#### 4.0 Lexical Conventions

#### 4.1 Case Sensitivity

Verilog is case sensitive.

#### 4.2 White Space Characters

blanks, tabs, newlines (carriage return), and formfeeds.

#### 4.3 Comments

// begins a single line comment, terminated by a newline.

/\* begins a multi-line block comment, terminated by a \*/.

#### 4.4 Attributes

- (\* begins an attribute, terminated by a \*).

- An attribute specifies special properties of a Verilog object or statement, for use by specific software tools, such as synthesis. Attributes were added in Verilog-2001.

- An attribute can appear as a prefix to a declaration, module items, statements, or port connections.

- An attribute can appear as a suffix to an operator or a call to a function.

- An attribute may be assigned a value. If no value is specified, the default value is 1.

- Multiple attributes can be specified as a comma-separated list.

- There are no standard attributes in the Verilog-2001 standard; Software tools

or other standards will define attributes as needed.

# Attribute Example (\* full\_case, parallel\_case \*) case (state) ... endcase assign sum = a + (\* CLA=1 \*) b;

<sup>†</sup> indicates new reserved words that were added in the Verilog-2001 standard.

#### 4.5 Identifiers (names)

- Must begin with alphabetic or underscore characters a-z A-Z \_

- May contain the characters a-z A-Z 0-9 \_ and \$

- May use any character by escaping with a backslash ( \ ) at the beginning of the identifier, and terminating with a white space.

- Identifiers created by an array of instances or a generate block may also contain the characters [ and ].

| Examples | Notes                                                     |  |

|----------|-----------------------------------------------------------|--|

| adder    | legal identifier name                                     |  |

| XOR      | uppercase identifier is unique from <b>xor</b> keyword    |  |

| \reset-  | an escaped identifier (must be followed by a white space) |  |

#### 4.6 Hierarchical Path Names

A net, variable, task or function can be referenced anywhere in the design hierarchy using either a full or relative hierarchy path.

- A full path consists of the top-level module, followed by any number of module instance names down to the object being reference. A period is used to separate each name in the hierarchy path.

- A relative path consists of a module instance name in the current module, followed by any number of module instance names down to the object being referenced. A period is used to separate each name in the hierarchy path.

#### 4.7 Hierarchy Scopes and Name Spaces

There are four primary types of name spaces.

- Global names are visible in all names spaces:

- Module, primitive and configuration definition names

- Text macro names (created by `define). Macro names are only visible from the point of definition on; source code compiled prior to the definition cannot see the macro names.

- Scope names create a new level of hierarchy:

- · module definitions

- · function definitions

- · task definitions

- named blocks (begin—end or fork—join)

- · Other name spaces:

- · specify blocks

- · attributes

An identifier name defined within a name space is unique to that space and cannot be defined again within the same space. In general, references to an identifier name within a scope will search first in the local scope, and then search upward through the scope hierarchy up to a module boundary.

## 4.8 Logic Values

Verilog uses a 4 value logic system for modeling. There are two additional unknown logic values that may occur internal to the simulation, but which cannot be used for modeling.

| Logic Value | Description                                                                  |  |

|-------------|------------------------------------------------------------------------------|--|

| 0           | zero, low, or false                                                          |  |

| 1           | one, high, or true                                                           |  |

| z or Z      | high impedance (tri-stated or floating)                                      |  |

| x or X      | unknown or uninitialized                                                     |  |

| L           | partially unknown; either 0 or Z, but not 1 (internal simulation value only) |  |

| н           | partially unknown; either 1 or Z, but not 0 (internal simulation value only) |  |

# 4.9 Logic Strengths

Logic values can have 8 strength levels: 4 driving, 3 capacitive, and high impedance (no strength). A net with multiple drivers can have a combination of strengths, represented as a pair of octal numbers, plus the value (e.g. 65X).

| Strength<br>Level | Strength<br>Name  | Specification<br>Keyword N |         |      | Display<br>Mnemonic |  |

|-------------------|-------------------|----------------------------|---------|------|---------------------|--|

| 7                 | supply drive      | supply0                    | supply1 | Su0  | Su1                 |  |

| 6                 | strong drive      | strong0                    | strong1 | st0  | st1                 |  |

| 5                 | pull drive        | pull0                      | pull1   | Pu0  | Pu1                 |  |

| 4                 | large capacitive  | large                      |         | La0  | La1                 |  |

| 3                 | weak drive        | weak0                      | weak1   | We0  | We1                 |  |

| 2                 | medium capacitive | medium                     |         | Me0  | Me1                 |  |

| 1                 | small capacitive  | small                      |         | Sm0  | Sm1                 |  |

| 0                 | high impedance    | highz0                     | highz1  | HiZ0 | HiZ1                |  |

# 4.10 Literal Real Numbers

| value.value            | decimal notation                                     |

|------------------------|------------------------------------------------------|

| base e exponent        | scientific notation; there should be no space before |

| base <b>E</b> exponent | and after the e or E token                           |

- Real numbers are represented in double-precision floating point form.

- There must be a value on either side of the decimal point.

- The value may only contain the characters **0-9** and underscore.

| Examples | Notes                                          |

|----------|------------------------------------------------|

| 0.5      | must have value on both sides of decimal point |

| 3e4      | 3 times 10 <sup>4</sup> (30000)                |

| 5.8E-3   | 5.8 times 10 <sup>-3</sup> (0.0058)            |

## **4.11 Literal Integer Numbers**

| value            | unsized decimal integer                  |

|------------------|------------------------------------------|

| size' base value | sized integer in a specific radix (base) |

- *size* (optional) is the number of bits in the number. Unsized integers default to at least 32-bits.

- 'base represents the radix and sign property of the value. The base and sign characters are *not* case sensitive (e.g. 'b and 'B are equivalent).

| Radix                | Symbol | Legal Values                    |

|----------------------|--------|---------------------------------|

| unsigned binary      | 'b     | 0, 1, x, X, z, Z, ?, _          |

| unsigned octal       | ′0     | 0-7, x, X, z, Z, ?, _           |

| unsigned decimal     | 'd     | 0-9,_                           |

| unsigned hexadecimal | 'h     | 0-9, a-f, A-F, x, X, z, Z, ?, _ |

| signed binary        | 'sb    | 0, 1, x, X, z, Z, ?, _          |

| signed octal         | 'so    | 0-7, x, X, z, Z, ?, _           |

| signed decimal       | 'sd    | 0-9, _                          |

| signed hexadecimal   | 'sh    | 0-9, a-f, A-F, x, X, z, Z, ?, _ |

- The ? is another way of representing the z logic value.

- An underscore is ignored (used to enhance readability). The underscore cannot be used as the first character of the value.

- Values are expanded from right to left (lsb to msb).

- When size is fewer bits than value, the upper bits are truncated.

- When size is more bits than value, and the left-most bit of value is 0 or 1, zeros are left-extended to fill the size.

- When size is more bits than value, and the left-most bit of value is z or x, the z or x is left-extended to fill the size.

- Signed numbers are interpreted as 2's complement values.

- Specifying a literal number as signed affects operations on the number; it does not affect expanding a value to the specified size of the number.

| Examples | Size    | Sign     | Radix   | Binary Equivalent    |  |

|----------|---------|----------|---------|----------------------|--|

| 10       | unsized | signed   | decimal | 001010 (32-bits)     |  |

| '07      | unsized | unsigned | octal   | 000111 (32-bits)     |  |

| 1'b1     | 1 bit   | unsigned | binary  | 1                    |  |

| 8'sHc5   | 8 bits  | signed   | hex     | 11000101             |  |

| 6'hF0    | 6 bits  | unsigned | hex     | 110000 (truncated)   |  |

| 6'hA     | 6 bits  | unsigned | hex     | 001010 (zero filled) |  |

| 6'shA    | 6 bits  | signed   | hex     | 001010 (zero filled) |  |

| 6 ' bZ   | 6 bits  | unsigned | binary  | ZZZZZZ (Z filled)    |  |

#### 5.0 Module Definitions

Verilog HDL models are represented as modules.

```

ANSI-C Style Port List (added in Verilog-2001)

module module_name

#(parameter_declaration, parameter_declaration,...)

(port_declaration port_name, port_name,...,

port_declaration port_name, port_name,...);

module items

endmodule

Old Style Port List

module module_name (port_name, port_name, ...);

port_declaration port_name, port_name,...;

port_declaration port_name, port_name,...;

module items

endmodule

```

(refer to the next page for the syntax of port declarations)

port\_name can be either:

- A simple name, which implicitly connects the port to an internal signal with the same name.

- A name with an explicit internal connection, in the form of .port\_name(signal), which connects the port to an internal signal with a different name, or a bit select, part select, or concatenation of internal signals.

Note: it is the internal signal name that is given a direction, not the port name.

The keyword macromodule is a synonym for module.

#### 5.1 Module Items

A module may contain any of the following items:

| data_type_declarations | (see section 6.0)  |

|------------------------|--------------------|

| parameter_declarations | (see section 6.3)  |

| module_instances       | (see section 7.0)  |

| primitive_instances    | (see section 8.0)  |

| generate_blocks        | (see section 9.0)  |

| procedural_blocks      | (see section 10.0) |

| continuous_assignments | (see section 11.0) |

| task_definitions       | (see section 13.0) |

| function_definitions   | (see section 14.0) |

| specify_blocks         | (see section 15.0) |

- Module items may appear in any order, but port, data\_type or parameter declarations must come before the declared name is referenced.

- Module functionality may be represented as:

- Behavioral or RTL modeled with procedural blocks or continuous assignment statements.

- Structural a netlist of module instances or primitive instances.

- · A mix of behavioral and structural.

#### 5.2 Port Declarations

Combined Declarations (added in Verilog-2001)

port\_direction data\_type signed range port\_name, port\_name, ...;

Old Style Declarations

port\_direction signed range port\_name, port\_name, ...;

data\_type\_declarations (see section 6.0)

- port\_direction is declared as:

- input for scalar or vector input ports.

- output for scalar or vector output ports.

- inout for scalar or vector bidirectional ports.

- *data\_type* (optional) is any of the types listed in section 6.0, except real. Combined port/data type declarations were added in Verilog-2001.

- signed (optional) indicates that values passed through the port are interpreted as 2's complement signed values. If either the port or the data type of the internal signal connected to the port are declared as signed, then both are signed. Signed ports were added in Verilog-2001.

- range (optional) is a range from [msb:/sb] (most-significant-bit to least-significant-bit).

- If no range is specified, ports are 1-bit wide.

- The msb and lsb must be a literal number, a constant, an expression, or a call to a constant function.

- Either little-endian convention (the *lsb* is the smallest bit number) or bigendian convention (the *lsb* is the largest bit number) may be used.

- The maximum port size may be limited, but will be at least 256 bits. Most software tools have a limit of 1 million bits.

- Port/data type connection rules:

|                                       | input ports                                           | output ports   | inout ports    |

|---------------------------------------|-------------------------------------------------------|----------------|----------------|

| Module Instance (outside the module)  | expression, net<br>or variable types<br>(except real) | net types only | net types only |

| Module Definition (inside the module) |                                                       |                | net types only |

- A real variable cannot be directly connected to a port. Real numbers can first be converted to or from 64-bit vectors using the \$realtobits and \$bitstoreal system tasks.

- The port range and data type range must be the same (if different, some software tools will use the data type size instead of reporting an error).

- The port direction must be declared before the data type is declared.

| Port Declaration Examples                                          | Notes                                                                            |

|--------------------------------------------------------------------|----------------------------------------------------------------------------------|

| input a,b,sel;                                                     | three scalar (1-bit) ports                                                       |

| input signed [15:0] a, b;                                          | two 16-bit ports that pass 2's complement values, little endian convention       |

| output signed [31:0] result;                                       | 32-bit port; values passed through the port are in 2's complement form           |

| output reg signed [32:1] sum;                                      | 32-bit port; the internal signal connected to the port is a signed reg data type |

| inout [0:15] data_bus;                                             | big endian convention                                                            |

| input [15:12] addr;                                                | msb:lsb may be any integer                                                       |

| <pre>parameter WORD = 32;<br/>input [WORD-1:0] addr;</pre>         | constant expressions may be used in the declaration                              |

| <pre>parameter SIZE = 4096;<br/>input [log2(SIZE)-1:0] addr;</pre> | constant functions may be called in the declaration                              |

# **6.0 Data Type Declarations**

Verilog has two major data type classes:

- Net data types are used to make connections between parts of a design.

- Nets reflect the value and strength level of the drivers of the net or the capacitance of the net, and do not have a value of their own.

- Nets have a resolution function, which resolves a final value when there are multiple drivers on the net.

- Variable data types are used as temporary storage of programming data.

- Variables can only be assigned a value from within an initial procedure, an always procedure, a task or a function.

- Variables can only store logic values; they cannot store logic strength.

- Variables are un-initialized at the start of simulation, and will contain a logic X until a value is assigned.

| General Rules For Choosing The Correct Data Type Class                                     |                            |

|--------------------------------------------------------------------------------------------|----------------------------|

| when a signal is driven by a module output, a primitive output, or a continuous assignment | use a <i>net</i> type      |

| when a signal is assigned a value in a Verilog procedure                                   | use a <i>variable</i> type |

# 6.1 Net Data Types

```

net_type signed [range] #(delay) net_name [array], ...;

net_type (drive_strength) signed [range] #(delay) net_name =

continuous_assignment;

trireg (capacitance_strength) signed [range] #(delay, decay_time)

net_name [array], ...;

```

Nets are used connect structural components together.

- A net data type must be used when a signal is:

- Driven by the output of a module instance or primitive instance.

- Connected to an input or input of the module in which it is declared.

- On the left-hand side of a continuous assignment.

- *net\_type* is one of the following keywords:

| wire    | interconnecting wire; CMOS resolution                   |  |

|---------|---------------------------------------------------------|--|

| wor     | wired outputs OR together; ECL resolution               |  |

| wand    | wired outputs AND together; open-collector resolution   |  |

| supply0 | constant logic 0 (supply strength)                      |  |

| supply1 | constant logic 1 (supply strength)                      |  |

| tri0    | pulls down when tri-stated                              |  |

| tri1    | pulls up when tri-stated                                |  |

| tri     | same as wire                                            |  |

| trior   | same as wor                                             |  |

| triand  | same as wand                                            |  |

| trireg  | holds last value when tri-stated (capacitance strength) |  |

- signed (optional) indicates that values are interpreted as 2's complement signed values. If either a port or the net connected to the port is declared as signed, then both are signed. Signed nets were added in Verilog-2001.

- [range] (optional) is a range from [msb:lsb] (most-significant-bit to least-significant-bit).

- If no range is specified, the nets are 1-bit wide.

- The *msb* and *lsb* must be a literal number, a constant, an expression, or a call to a constant function.

- Either little-endian convention (the *lsb* is the smallest bit number) or bigendian convention (the *lsb* is the largest bit number) may be used.

- The maximum net size may be limited, but will be at least 65,536 bits (2<sup>16</sup>) bits. Most software tools have a limit of 1 million bits.

- *delay* (optional) may only be specified on net data types. The syntax is the same as primitive delays (refer to section 8.0).

- [array] is [first\_address: last\_address][first\_address: last\_address]...

- Any number of array dimensions may be declared. Arrays of nets were added in Verilog-2001.

- first\_address and last\_address must be a literal number, a constant, an

expression, or a call to a constant function.

- · Either ascending or descending address order may be used.

- The maximum array size for each dimension may be limited, but is at least 16,777,216 ( $2^{24}$ ). Most software tools have unlimited array sizes.

- (strength) (optional) is specified as (strength1, strength0) or (strength0, strength1). See section 4.9 for the strength keywords.

- decay\_time (optional) specifies the amount of time a trireg net will store a

charge after all drivers turn-off, before decaying to logic X. The syntax is

(rise\_delay, fall\_delay, decay\_time). The default decay is infinite.

- The keywords vectored or scalared may be used immediately following the net\_type keyword. Software tools and/or the Verilog PLI may restrict access to individual bits within a vector that is declared as vectored.

| Net Declaration Examples                              | Notes                                                        |

|-------------------------------------------------------|--------------------------------------------------------------|

| wire a, b, c;                                         | 3 scalar (1-bit) nets                                        |

| tri1 [7:0] data_bus;                                  | 8-bit net, pulls-up when tri-stated                          |

| wire signed [1:8] result;                             | an 8-bit signed net                                          |

| wire [7:0] Q [0:15][0:256];                           | a 2-dimensional array of 8-bit wires                         |

| wire #(2.4,1.8) carry;                                | a net with rise, fall delays                                 |

| <pre>wire [0:15] (strong1,pull0)   sum = a + b;</pre> | a 16-bit net with drive strength and a continuous assignment |

| <pre>trireg (small)   #(0,0,35) ram_bit;</pre>        | net with small capacitance and 35 time unit decay time       |

#### 6.2 Variable Data Types

```

variable_type signed [range] variable_name, variable_name, ...;

variable_type signed [range] variable_name = initial_value, ...;

variable_type signed [range] variable_name [array], ...;

```

Variable data types are used for programming storage in procedural blocks.

- Variables store logic values only, they do not store logic strength.

- A variable data type must be used when the signal is on the left-hand side of a procedural assignment.

- Variables were called "registers" in older versions of the Verilog standard.

- variable\_type is one of the following:

| reg      | a variable of any bit size; unsigned unless explicitly declared as signed |  |

|----------|---------------------------------------------------------------------------|--|

| integer  | a signed 32-bit variable                                                  |  |

| time     | an unsigned 64-bit variable                                               |  |

| real     | a double-precision floating point variable                                |  |

| realtime | same as real                                                              |  |

- signed (optional) may only be used with reg variables, and indicates that values are interpreted as 2's complement signed values. If either a port or the reg connected to the port is declared as signed, then both are signed. Signed reg variables were added in Verilog-2001.

- [range] (optional) may only be used with reg variables, and is a range from [msb:lsb] (most-significant-bit to least-significant-bit).

- If no range is specified, then reg variables are 1-bit wide.

- The msb and lsb must be a literal number, a constant, an expression, or a call to a constant function.

- Either little-endian convention (the Isb is the smallest bit number) or bigendian convention (the Isb is the largest bit number) may be used.

- The maximum reg size may be limited, but will be at least 65,536 (2<sup>16</sup>) bits. Most software tools have a limit of 1 million bits.

- [array] is [first\_address: last\_address][first\_address: last\_address]...

- Any number of array dimensions may be declared. Variable arrays of more than one dimension were added in Verilog-2001.

- first\_address and last\_address must be a literal number, a constant, an

expression, or a call to a constant function.

- Either ascending or descending address order may be used.

- The maximum array size for each dimension may be limited, but is at least 16,777,216 ( $2^{24}$ ). Most software tools have unlimited array sizes.

- A one-dimensional array of reg variables with is referred to as a *memory*.

- initial\_value (optional) sets the initial value of the variable.

- The value is set in simulation time 0, the same as if the variable had been assigned a value in an initial procedure.

- If not initialized, the default value for reg, integer and time variables is X, and the initial value for real and realtime variables is 0.0.

- Specifying the initial value as part of the variable declaration was added in Verilog-2000

# 14 VERILOG HDL QUICK REFERENCE GUIDE

• The keywords **vectored** or **scalared** may be used immediately following the **reg** keyword. Software tools and/or the Verilog PLI may restrict access to individual bits within a vector that is declared as vectored.

| Variable Declaration Examples | Notes                                    |

|-------------------------------|------------------------------------------|

| reg a, b, c;                  | three scalar (1-bit) variables           |

| reg signed [7:0] d1, d2;      | two 8-bit signed variables               |

| reg [7:0] Q [0:3][0:15];      | a 2-dimensional array of 8-bit variables |

| integer i, j;                 | two signed integer variables             |

| real r1, r2;                  | two double-precision variables           |

| reg clock = 0, reset = 1;     | two reg variables with initial values    |

# 6.3 Other Data Types

| parameter  | a run-time constant for storing integers, real numbers, time, delays, or ASCII strings; may be redefined for each instance of a module (see section 7.0).                                                  |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| localparam | a local constant for storing integers, real numbers, time, delays, or ASCII strings; may not be directly redefined, but may be indirectly redefined by assigning the localparam the value of a parameter   |

| specparam  | a specify block constant for storing integers, real numbers, time, delays or ASCII strings; may be declared in the module scope or the specify block scope; may be redefined through SDF files or the PLI. |

| genvar     | a temporary variable used only within a generate loop; cannot be used anywhere else, and cannot be read during simulation.                                                                                 |

| event      | a momentary flag with no logic value or data storage; can be used for synchronizing concurrent activities within a module.                                                                                 |

#### Declaration syntax:

```

parameter signed [range] constant_name = value, ...;

parameter constant_type constant_name = value, ...;

localparam signed [range] constant_name = value, ...;

localparam constant_type constant_name = value, ...;

specparam constant_name = value, ...;

event event_name, ...;

```

- signed (optional) indicates that values are interpreted as 2's complement signed values. Signed constants were added in Verilog-2001.

- [range] (optional) is a range from [msb:/sb] (most-significant-bit to least-significant-bit).

- If no range is specified, the constant will default to the size of the last value initially assigned to it after any parameter redefinitions.

- The *msb* and *lsb* must be a literal number, a constant, an expression, or a call to a constant function.

- Either little-endian convention (the *lsb* is the smallest bit number) or bigendian convention (the *lsb* is the largest bit number) may be used.

- The maximum range may be limited, but will be at least 65,536 (2<sup>16</sup>) bits. Most software tools have a limit of 1 million bits.

- constant\_type (optional) can be integer, time, real or realtime. A constant declared with a type will have the same properties as a variable of that type. If no type is specified, the constant will default to the data type of the last value assigned to it, after any parameter redefinitions.

| Data Type Examples                                           | Notes                                                      |

|--------------------------------------------------------------|------------------------------------------------------------|

| parameter [2:0] s1 = 3'b001,<br>s2 = 3'b010,<br>s3 = 3'b100; | three 3-bit constants                                      |

| <pre>parameter integer period = 10;</pre>                    | an integer constant                                        |

| localparam signed offset = -5;                               | unsized signed constant defaults to width of initial value |

| event data_ready, data_sent;                                 | two event data types                                       |

#### 6.4 Vector Bit Selects and Part Selects

| 0.4 Vector Bit Selects and I art Selects                        |  |  |

|-----------------------------------------------------------------|--|--|

| Bit Select                                                      |  |  |

| vector_name[bit_number]                                         |  |  |

| Constant Part Select                                            |  |  |

| <pre>vector_name[ bit_number : bit_number]</pre>                |  |  |

| Variable Part Select (added in Verilog-2001)                    |  |  |

| <pre>vector_name[starting_bit_number+: part_select_width]</pre> |  |  |

| vector_name[ starting_bit_number -: part_select_width]          |  |  |

- A bit select can be an integer, a constant, a net, a variable or an expression.

- A constant part select is a group of bits from within the vector

- The part select must be contiguous bits.

- The bit numbers must be a literal number or a constant.

- The order of the part select must be consistent with the declaration of the vector (e.g. if the lsb is the lowest bit number in the declaration, then the lsb of the part select must also be the lowest bit number).

- Variable part selects can vary the starting point of the part select, but the width of the part select must be a literal number, a constant or a call to a constant function. Variable part selects were added in Verilog-2001.

- +: indicates the part select increases from the starting point.

- -: indicates the part select decreases from the starting point.

# 6.5 Array Selects

| array_name[index][index]              |  |

|---------------------------------------|--|

| array_name[index][index][bit_number]  |  |

| array_name[index][index][part_select] |  |

- An array select can be an integer, a net, a variable, or an expression.

- Multiple indices, bit selects and part selects from an array were added in Verilog-2001.

# 6.6 Reading and Writing Arrays

- Only one element at a time within an array can be read from or written to.

- A memory array (a one-dimensional array of reg variables) can be loaded using the \$readmemb, \$readmemh, \$sreadmemb, or \$sreadmemh system tasks.

#### 7.0 Module Instances

```

Port Order Connections

module_name instance_name instance_array_range (signal, signal, ...);

Port Name Connections

module_name instance_name instance_array_range

(.port_name(signal), .port_name(signal), ...);

Explicit Parameter Redefinition

defparam heirarchy_path.parameter_name = value;

In-line Implicit Parameter Redefinition

module_name #(value, value, ...) instance_name (signal, ...);

In-line Explicit Parameter Redefinition (added in Verilog-2001)

module_name #(.parameter_name(value),

.parameter_name(value), ...) instance_name (signal, ...);

```

- *Port order* connections list the signals in the same order as the port list in the module definition. Unconnected ports are designated by two commas with no signal listed.

- Port name connections list both the port name and signal connected to it, in any order.

- instance\_name (required) is used to make multiple instances of the same module unique from one another.

- instance\_array\_range (optional) instantiates multiple modules, each instance is connected to different bits of a vector.

- The range is specified as [left hand index: right hand index].

- If the bit width of a module port in the array is the same as the width of the signal connected to it, the full signal is connected to each instance of the module.

- If the bit width of a module port is different than the width of the signal connected to it, each module port instance is connected to a part select of the signal, with the right-most instance index connected to the right-most part of the vector, and progressing towards the left.

- There must be the correct number of bits in each signal to connect to all instances (the signal size and port size must be multiples).

- Instance arrays were added in Verilog-1995, but many software tools did not support them until Verilog-2001.

- Multiple instances of a module can also be created using a generate block (see section 9.0).

- parameter values within a module may be redefined for each instance of the module. Only parameter declarations may be redefined; localparam and specparam constants cannot be redefined.

- Explicit redefinition uses a **defparam** statement with the parameter's hierarchical name.

- In-line implicit redefinition uses the # token as part of the module instantiation. Parameter values are redefined in the same order in which they are declared within the module.

- In-line explicit redefinition uses the # token as part of the module instantiation. Parameter values may be redefined in any order. In-line explicit parameter redefinition was added in Verilog-2001.

# **Module Instance Examples** module reg4 (output wire [3:0] q, input wire [3:0] d, input wire clk); //port order connection, no connection to 2nd port position dff u1 (q[0], , d[0], clk); //port name connection, qb not connected dff u2 (.clk(clk),.q(q[1]),.data(d[1])); //explicit parameter redefinition dff u3 (q[2], ,d[2], clk); defparam u3.delay = 3.2; //in-line implicit parameter redefinition dff #(2) u4 (q[3], , d[3], clk); //in-line explicit parameter redefinition dff #(.delay(3)) u5 (q[3], , d[3], clk); endmodule module dff (output q, output qb, input data, input clk); parameter delay = 1; //default delay parameter dff\_udp #(delay) (q, data, clk); not (qb, q); endmodule

# **Array of Instances Example** module tribuf64bit (output wire [63:0] out, input wire [63:0] in, input wire enable); //array of 8 8-bit tri-state buffers; each instance is connected //to 8-bit part selects of the 64-bit vectors; The scalar enable line //is connected to all instances tribuf8bit i[7:0] (out, in, enable); endmodule module tribuf8bit (output wire [7:0] y, input wire [7:0] a, input wire en); //array of 8 Verilog tri-state primitives; each bit of the //vectors is connected to a different primitive instance bufif1 u[7:0] (y, a, en); endmodule

#### 8.0 Primitive Instances

```

gate_type (drive_strength) #(delay) instance_name

[instance_array_range] (terminal, terminal, ...);

switch_type #(delay) instance_name

[instance_array_range] (terminal, terminal, ...);

```

| Gate                   | Primitives          | Terminal Order and Quantity    |

|------------------------|---------------------|--------------------------------|

| and<br>or<br>xor       | nand<br>nor<br>xnor | (1-output, 1-or-more-inputs)   |

| buf                    | not                 | (1-or-more-outputs, 1-input)   |

| bufif0<br>bufif1       | notif0<br>notif1    | (1-output, 1-input, 1-control) |

| pullup                 | pulldown            | (1-output)                     |

| User Defined Primitive |                     | (1-output, 1-or-more-inputs)   |

| Switch Primitives   |                     | Terminal Order and Quantity               |

|---------------------|---------------------|-------------------------------------------|

| pmos<br>rpmos       | nmos<br>rnmos       | (1-output, 1-input, 1-control)            |

| cmos                | rcmos               | (1-output, 1-input, n-control, p-control) |

| tran                | rtran               | (2-bidirectional-inouts)                  |

| tranif0<br>rtranif0 | tranif1<br>rtranif1 | (2-bidirectional-inouts, 1-control)       |

- delay (optional) represents the propagation delay through a primitive. The

default delay is zero. Integers or real numbers may be used.

- Separate delays for 1, 2 or 3 transitions may be specified.

- Each transition may have a single delay or a min:typ:max delay range.

| Delays | Transitions represented (in order)                                                                                |  |

|--------|-------------------------------------------------------------------------------------------------------------------|--|

| 1      | all output transitions                                                                                            |  |

| 2      | rise, fall output transitions                                                                                     |  |

| 3      | rise, fall, turn-off output transitions (turn-off delay is the time for a tri-state primitive to transition to Z) |  |

- strength (optional) is specified as (strength1, strength0) or (strength0, strength1). The default is (strong1, strong0). Refer to section 4.9 for strength keywords.

- Only gate primitives may have the output drive strength specified. Switch primitives pass the input strength level to the output. Resistive switches reduce the strength level as it passes through.

- *instance\_name* (optional) may used to reference specific primitives in configurations, debugging tools, schematic diagrams, etc.

- *instance\_array\_range* (optional) instantiates multiple primitives, each instance is connected to different bits of a vector.

- The range is specified as [left-hand-index: right-hand-index].

- Primitive instances are connected with the right-most instance index connected to the right-most bit of each vector, and progressing to the left.

- Vector signals must be the same size as the array.

- Scalar signals are connected to all instances in the array.

- Instance arrays were added in Verilog-1995, but many software tools did not support them until Verilog-2001.

- Multiple instances of a primitive can also be created using a generate block (see section 9.0).

| Primitive Instance Examples                  | Notes                          |

|----------------------------------------------|--------------------------------|

| and i1 (out,in1,in2);                        | zero delay gate primitive      |

| and #5 (o,i1,i2,i3,i4);                      | same delay for all transitions |

| not #(2,3) u7 (out,in);                      | separate rise & fall delays    |

| <pre>buf (pull0,strong1)(y,a);</pre>         | output drive strengths         |

| wire [31:0] y, a;<br>buf #2.7 i[31:0] (y,a); | array of 32 buffers            |

#### 9.0 Generate Blocks

```

genvar genvar_name, ...;

generate

genvar genvar_name, ...;

generate_items

endgenerate

```

Generate blocks provide control over the creation of many types of module items. A generate block must be defined within a module, and is used to generate code within that module. Generate blocks were added in Verilog-2001.

- genvar is an integer variable which must be a positive value. They may only be used within a generate block. Genvar variables only have a value during elaboration, and do not exist during simulation. Genvar variables must be declared within the module where the genvar is used. They may be declared either inside or outside of a generate block.

- generate\_items are:

```

genvar_name = constant_expression;

net_declaration

variable_declaration

module_instance

primitive_instance

continuous_assignment

procedural_block

task_definition

function_definition

if (constant_expression)

generate_item or generate_item_group

if (constant_expression)

generate_item or generate_item_group

else

generate_item or generate_item_group

case (constant_expression)

genvar_value : generate_item or generate_item_group

genvar_value: generate_item or generate_item_group

default: generate_item or generate_item_group

endcase

for (genvar_name = constant_expression; constant_expression;

genvar_name = constant_expression)

generate_item or generate_item_group

• generate_item_group is:

begin: generate_block_name

generate_item

generate_item

end

```

- A generate for loop permits one or more generate items to be instantiated multiple times. The index loop variable must be a genvar.

- A generate if—else or case permits generate items to be conditionally instantiated based on an expression that is deterministic at the time the design is elaborated.

- generate\_block\_name (optional) is used to create a unique instance name for each generated item.

- Task and function definitions are permitted within the generate scope, but not in a generate for-loop. That is, only one definition of the task or function can be generated.

#### **Generate Block Examples**

/\* If the input bus widths are 8-bits or less, generate an instance of a carry-look-ahead multiplier. If the input bus widths are greater than 8-bits, generate an instance of a wallace-tree multiplier \*/

```

module multiplier (a, b, product);

parameter a_width = 8, b_width = 8;

localparam product_width = a_width + b_width;

input

[a_width-1:0]

a;

input

[b_width-1:0]

b;

output [product_width-1:0] prod;

generate

if ((a_width < 8) | | (b_width < 8))</pre>

CLA_mult #(a_width, b_width) m (a, b, prod);

WALLACE_mult #(a_width, b_width) m (a, b, prod);

endgenerate

endmodule

```

/\* A parameterized gray-code to binary-code converter using a loop to generate a continuous assignment for each bit of the converter \*/

```

module gray2bin1 (bin, gray);

parameter SIZE = 8;

output [SIZE-1:0] bin;

input [SIZE-1:0] gray;

genvar i;

generate

for (i=0; i<SIZE; i=i+1)

begin: bit

assign bin[i] = ^gray[SIZE-1:i];

end

endgenerate

endmodule</pre>

```

#### 10.0 Procedural Blocks

```

type_of_block @(sensitivity_list)

statement_group:group_name

local_variable_declarations

time_control procedural_statements

end_of_statement_group

```

- type\_of\_block is either initial or always

- initial blocks process statements one time.

- always blocks are an infinite loop which process statements repeatedly.

- sensitivity\_list (optional) is an event time control that controls when all statements in the procedural block will be evaluated (refer to section 10.2).

- statement\_group end\_of\_statement\_group controls the execution order

of two or more procedural statements. A statement group is not required if

there is only one procedural statement.

- begin—end groups two or more statements together sequentially, so that statements are evaluated in the order they are listed. Each time control in the group is relative to previous time controls.

- fork—join groups two or more statements together in parallel, so that all

statements are evaluated concurrently. Each time control in the group is

absolute to the time the group started.

- group\_name (optional) creates a local hierarchy scope. Named groups may have local variables, and may be aborted with a disable statement.

- *local\_variable\_declarations* (optional) must be a variable data type (may only be declared in named statement groups).

- *time\_control* is used to control when the next statement in a procedural block is executed (refer to section 10.1).

- procedural\_statement is either an assignment statement or a programming statement (refer to sections 10.3 and 10.4).

| Procedural Block Examples                                                                                     | Notes                                                                                                                                                       |

|---------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>initial   begin: test_loop    integer i;    for (i=0; i&lt;=15; i=i+1;       #5 test_in = i;   end</pre> | initial procedure executes statements one time; the named group allows a local variable to be declared.                                                     |

| <pre>initial   fork    bus = 16'h0000;    #10 bus = 16'hC5A5;    #20 bus = 16'hFFAA;   join</pre>             | initial procedure executes statements one time; the fork—join group places statements in parallel (the delays before each statement are in absolute times). |

| <pre>always @(a or b or ci) begin   sum = a + b + ci; end</pre>                                               | always procedure executes statements repeatedly, controlled by the sensitivity list.                                                                        |

| <pre>always @(posedge clk)   q = data;</pre>                                                                  | a statement group is not required when there is only one statement.                                                                                         |

#### 10.1 Procedural Time Controls

#### #delay

Delays execution of the next statement for a specific amount of time. The delay may be a literal number, a variable, or an expression.

```

@(edge signal or edge signal or ...)

@(edge signal, edge signal, ...)

@(*)

```

Delays execution of the next statement until there is a transition on a signal.

- edge (optional) maybe either posedge or negedge. If no edge is specified, then any logic transition is used.

- Either a comma or the keyword **or** may be used to specify events on any of several signals. The use of commas was added in Verilog-2001.

- signal may be a net type or variable type, and may be any vector size.

- An asterisk in place of the list of signals indicates sensitivity to any edge of all signals that are read in the statement or statement group that follows.

w was added in Verilog-2001.

- Parenthesis are not required when there is only one signal in the list and no edge is specified.

#### wait (expression)

Delays execution of the next statement until the expression evaluates as true.

#### 10.2 Sensitivity Lists

The sensitivity list is used at the beginning of an always procedure to infer combinational logic or sequential logic behavior in simulation.

- always @(signal, signal, ...) infers combinational logic if the list of signals contains all signals read within the procedure.

- always @\* infers combinational logic. Simulation and synthesis will automatically be sensitive to all signals read within the procedure. @\* was added in Verilog-2001.

- always @(posedge signal, negedge signal, ...) infers sequential logic. Either the positive or negative edge can be specified for each signal in the list. A specific edge should be specified for each signal in the list.

NOTE: The Verilog language does not have a true "sensitivity list". Instead, the @ time control at the beginning of a procedure delays the execution of all statements within the procedure until an edge occurs on the signals listed. Thus, if the @ control is the first thing in the procedure, the entire procedure appears to be sensitive to changes in the signals listed. The @ token is a time control, however, and not a true sensitivity list. An edge-sensitive time control is only sensitive to changes when the procedure is suspended at that control. If the procedure is suspended at another time control inside the procedure, it will not be sensitive to changes at the time control in the pseudo sensitivity list.

#### 10.3 Procedural Assignment Statements

## variable = expression;

Blocking procedural assignment. Expression is evaluated and assigned when the statement is encountered. In a *begin—end* sequential statement group, execution of the next statement is blocked until the assignment is complete. In the sequence begin m=n; n=m; end, the first assignment changes m before the second assignment reads m.

#### variable <= expression;

Non-blocking procedural assignment. Expression is evaluated when the statement is encountered, and assignment is postponed until the end of the simulation time-step. In a *begin—end* sequential statement group, execution of the next statement is not blocked; and will be evaluated before the assignment is complete. In the sequence begin m<=n; n<=m; end, both assignments will be evaluated before m or n changes.

MODELING TIP: To avoid potential simulation race conditions in zero-delay models:

- Use blocking assignments ( = ) to model combinational logic.

- Use non-blocking assignments ( <= ) to model sequential logic.

#### timing\_control variable = expression;

# timing\_control variable <= expression;

Delayed procedural assignments. Evaluation of the expression on the right-hand side is delayed by the timing control.

#### variable = timing\_control expression;

Blocking intra-assignment delay. Expression is evaluated in the time-step in which the statement is encountered, and assigned in the time-step specified by the timing control. In a *begin—end* sequence, execution of the next statement in the sequence is blocked until the assignment is completed (which is when the delay time has elapsed).

# variable <= timing\_control expression;

Non-blocking intra-assignment delay. Expression is evaluated in the time-step in which the statement is encountered, and assigned at the end of the time-step specified by the timing control. In a *begin—end* sequence, execution of the next statement(s) in the sequence are not blocked, and can execute before the delay has elapsed. Models transport delay.

#### assign variable = expression;

Procedural continuous assignment. Overrides any other procedural assignments to a variable.

#### deassign variable:

De-activates a procedural continuous assignment.

#### force net or variable = expression;

Forces any data type to a value, overriding all other logic.

#### release net\_or\_variable;

Removes the effect of a force.

## 10.4 Procedural Programming Statements

#### if ( expression ) statement or statement\_group

Executes the next statement or statement group if the expression evaluates as true.

#### if ( expression ) statement or statement\_group

#### else statement or statement\_group

Executes the first statement or statement group if the expression evaluates as true. Executes the second statement or statement group if the expression evaluates as false or unknown.

# case ( expression )

case\_item: statement or statement\_group

case\_item, case\_item: statement or statement\_group

default: statement or statement\_group

#### endcase

Compares the value of the expression to each case item and executes the statement or statement group associated with the first matching case. Executes the default if none of the cases match (the default case is optional).

#### casez ( expression )

Special version of the case statement which uses a  $\, \mathbf{z} \,$  logic value to represent don't-care bits in either the case expression or a case item. (the  $\, \mathbf{z} \,$  can also be represented as a  $\, \mathbf{z} \,$ ).

#### casex ( expression )

Special version of the case statement which uses z or x logic values to represent don't-care bits in either the case expression or a case item. (the z can also be represented as a ? ).

# for ( initial\_assignment; expression; step\_assignment ) statement or statement group

- Executes *initial\_assignment* once, when the loop starts.

- Executes the statement or statement group as long as expression evaluates as true.

- Executes step\_assignment at the end of each pass through the loop.

# while ( expression ) statement or statement group

A loop that executes a statement or statement group as long as an expression evaluates as true. The expression is evaluated at the start of each pass of the loop.

# repeat ( number ) statement or statement\_group

A loop that executes the statement or statement group a set number of times. The number may be an expression (the expression is only evaluated when the loop is first entered).

#### forever statement or statement group

An infinite loop that continuously executes the statement or statement group.

#### disable group\_name;

Discontinues execution of a named group of statements. Simulation of that group jumps to the end of the group without executing any scheduled events.

# **Procedural Statement Examples** initial // A 50 ns clock oscillator that starts after 1000 time units begin clk = 0;#1000 forever #25 clk = ~clk; end // In this example, the sensitivity list infers sequential logic always @(posedge clk) begin // non-blocking assignments prevent race conditions in byte swap word[15:8]<= word[7:0]; word[7:0] <= word[15:8]; // In this example, the sensitivity list infers combinational logic always @(a, b, ci) sum = a + b + ci;// In this example, the sensitivity list infers combinational logic, // (the @\* token infers sensitivity to any signal read in the statement or // statement group which follows it, which are sel, a and b) always @\* begin if (sel==0) y = a + b;y = a \* b;end // This example using illustrates several programming statements always @(posedge clk) begin casez (opcode) //casez makes Z a don't care 3'b1??: alu\_out = accum; //? in literal integer is same as Z 3'b000: while (bloc\_xfer) //loop until false repeat (5) @(posedge clk) //loop 5 clock cycles begin RAM[address] = data\_bus; address = address + 1; end 3'b011: begin : load // named group // local variable integer i; for (i=0; i<=255; i=i+1)@(negedge clk) data\_bus = RAM[i]; end default:\$display("illegal opcode in module %m"); endcase end

# 11.0 Continuous Assignments

#### **Explicit Continuous Assignment**

net\_type [size] net\_name;

assign #(delay) net\_name = expression;

Implicit Continuous Assignment

net\_type (strength) [size] #(delay) net\_name = expression;

Continuous assignments drive net types with the result of an expression. The result is automatically updated anytime a value on the right-hand side changes.

- Explicit continuous assignments use the assign keyword to continuously assign a value to a net.

- The net can be explicitly declared in a separate statement (see section 6.1).

- A net will be inferred if an undeclared name appears on the left side of the assignment, and the name is declared as a port of the module containing the continuous assignment. The net vector size will be the size of the port.

- New in Verilog-2001: A 1-bit net will be inferred if an undeclared name appears on the left side of the assignment, and the name is not a port of the module containing the continuous assignment.

- Implicit continuous assignments combine the net declaration and continuous assignment into one statement, omitting the assign keyword.

- net\_type may be any of the net data types except trireg.

- strength (optional) may only be specified when the continuous assignment is combined with a net declaration. The default strength is (strong1, strong0).

- delay (optional) follows the same syntax as primitive delays (refer to section 8.0). The default delay is zero.

- expression may include any data type, any operator, and calls to functions.

- Continuous assignments model combinational logic. Each time a signal changes on the right-hand side, the right-hand side is re-evaluated, and the result is assigned to the net on the left-hand side.

- Continuous assignments are declared outside of procedural blocks. They

automatically become active at time zero, and are evaluated concurrently with

procedural blocks, module instances, and primitive instances.

# **Continuous Assignment Examples**

// Explicit continuous assignment

wire [31:0] mux\_out;

assign mux\_out = sel? a : b;

// Implicit continuous assignment; the net declaration

// and the continuous assignment are combined

tri [0:15] #2.8 buf\_out = en? in: 16'bz;

// Implicit continuous assignment with strengths

wire [63:0] (strong1,pull0) alu\_out =

alu\_function(opcode,a,b);

# 12.0 Operators

- For most operations, the operands may be nets, variables, constants or function calls. Some operations are not legal on real (floating-point) values.

- Operators which return a true/false result will return a 1-bit value where  ${\tt 1}$  represents true,  ${\tt 0}$  represents false, and  ${\tt x}$  represents indeterminate.

|                         | Bitwise Operators                                        |                                                               |  |  |  |

|-------------------------|----------------------------------------------------------|---------------------------------------------------------------|--|--|--|

| ~                       | ~m                                                       | invert each bit of m                                          |  |  |  |

| &                       | m & n                                                    | AND each bit of m with each bit of n                          |  |  |  |

| -                       | m   n                                                    | OR each bit of m with each bit of n                           |  |  |  |

| ٨                       | m ^ n                                                    | exclusive-OR each bit of m with n                             |  |  |  |

| ~^ or ^~                | m ~^ n                                                   | exclusive-NOR each bit of m with n                            |  |  |  |

| <<                      | m << n                                                   | shift m left n-times and fill with zeros                      |  |  |  |

| >>                      | m >> n                                                   | shift m right n-times and fill with zeros                     |  |  |  |

|                         | Unary Reduction Operators                                |                                                               |  |  |  |

| &                       | &m                                                       | AND all bits in m together (1-bit result)                     |  |  |  |

| ~&                      | ~&m                                                      | NAND all bits in m together (1-bit result)                    |  |  |  |

| - 1                     | m                                                        | OR all bits in m together (1-bit result)                      |  |  |  |

| ~                       | ~   m                                                    | NOR all bits in m together (1-bit result)                     |  |  |  |

| ٨                       | ^m                                                       | exclusive-OR all bits in m (1-bit result)                     |  |  |  |

| ~^ or ^~                | ~^m                                                      | exclusive-NOR all bits in m (1-bit result)                    |  |  |  |

|                         | Logical Operators                                        |                                                               |  |  |  |

| !                       | ! m                                                      | is m not true? (1-bit True/False result)                      |  |  |  |

| &&                      | m && n                                                   | are both m and n true? (1-bit True/False result)              |  |  |  |

|                         | m    n                                                   | are either m or n true? (1-bit True/False result)             |  |  |  |

| Equalit                 | y and Rela                                               | tional Operators (return X if an operand has X or Z)          |  |  |  |

| ==                      | m == n                                                   | is m equal to n? (1-bit True/False result)                    |  |  |  |

| !=                      | m != n                                                   | is m not equal to n? (1-bit True/False result)                |  |  |  |

| <                       | m < n                                                    | is m less than n? (1-bit True/False result)                   |  |  |  |

| >                       | m > n                                                    | is m greater than n? (1-bit True/False result)                |  |  |  |

| <=                      | m <= n                                                   | is m less than or equal to n? (1-bit True/False result)       |  |  |  |

| >=                      | m >= n                                                   | is m greater than or equal to n? (1-bit True/False result)    |  |  |  |

|                         | Identity Operators (compare logic values 0, 1, X, and Z) |                                                               |  |  |  |

| ===                     | m === n                                                  | is m identical to n? (1-bit True/False results)               |  |  |  |

| !==                     | m !== n                                                  | is m not identical to n? (1-bit True/False result)            |  |  |  |

| Miscellaneous Operators |                                                          |                                                               |  |  |  |

| ?:                      | sel?m:n                                                  | conditional operator; if sel is true, return m: else return n |  |  |  |

| {}                      | {m,n}                                                    | concatenate m to n, creating a larger vector                  |  |  |  |

| {{}}                    | {n{ }}                                                   | replicate inner concatenation n-times                         |  |  |  |

| ->                      | -> m                                                     | trigger an event on an event data type                        |  |  |  |

| Arithmetic Operators |         |                                                                                                                  |

|----------------------|---------|------------------------------------------------------------------------------------------------------------------|

| +                    | m + n   | add n to m                                                                                                       |

| _                    | m - n   | subtract n from m                                                                                                |

| _                    | -m      | negate m (2's complement)                                                                                        |

| *                    | m * n   | multiply m by n                                                                                                  |

| /                    | m / n   | divide m by n                                                                                                    |

| %                    | m % n   | modulus of m / n                                                                                                 |

| **                   | m ** n  | m to the power n (new in Verilog-2001)                                                                           |

| <<<                  | m <<< n | shift m left n-times, filling with 0 (new in Verilog-2001)                                                       |

| >>>                  | m >>> n | shift m right n-times; fill with value of sign bit if expression is signed, otherwise fill with 0 (Verilog-2001) |

#### 12.1 Operator Expansion Rules

As a general rule, all operands in an expression are first expanded to the size of the largest vector in the statement (including both sides of an assignment statement). Concatenate and replicate operations are evaluated before the expansion, and represent a new vector size.

- Unsigned operands are expanded by left-extending with zero.

- Signed operands are expanded by left-extending with the value of the mostsignificant bit (the sign bit).

#### 12.2 Arithmetic Operation Rules

For most operators (there are exceptions) all operands in the expression are used to determine how the operation is performed:

- If any operand is real, then floating-point arithmetic will be performed.

- If any operand is unsigned, then unsigned arithmetic will be performed.

- If all operands are signed, then signed arithmetic will be performed.

- An operand can be "cast" to signed or unsigned using the \$signed and \$unsigned system functions (added in Verilog-2001).

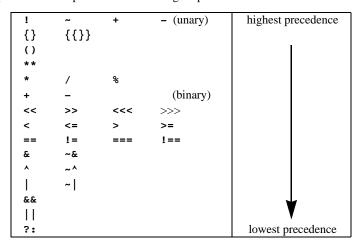

# 12.3 Operator Precedence

Compound expressions are evaluated in the order of operator precedence. Operators within parenthesis have a higher precedence and are evaluated first.

#### 13.0 Task Definitions

```

ANSI-C Style Task Declaration (added in Verilog-2001)

task automatic task_name (

port_declaration port_name, port_name, ... ,

port_declaration port_name, port_name, ... );

local variable declarations

procedural_statement or statement_group

endtask

Old Style Task Declaration

(port declarations determine the order signals are passed in/out of the task)

task automatic task_name;

port_declaration port_name, port_name, ...;

port_declaration port_name, port_name, ...;

local variable declarations

procedural_statement or statement_group

endtask

```

Tasks are analogous to subroutines in other languages.

- Must be declared within a module, and are local to that module.

- Must be called from an initial procedure, an always procedure or another task.

- May have any number of input, output or inout ports, including none.

- Tasks may contain time controls (#, @, or wait).

**automatic** (optional) allocates storage space each time the task is called, allowing the task to be re-entrant (the task can be called while previous calls to the task are still executing). Automatic tasks were added in Verilog-2001.

port declaration can be:

- port\_direction signed range

- port\_direction reg signed range

- port\_direction port\_type

port\_direction can be input, output or inout.

range (optional) is a range from [msb:lsb] (most-significant-bit to least-significant-bit). msb and lsb must be a literal number, a constant, an expression, or a call to a constant function. If no range is specified, the ports are 1-bit wide.

$port\_type$  can be integer, time, real or realtime.

signed (optional) indicates that values are interpreted as 2's complement signed values.

#### 14.0 Function Definitions

```

ANSI-C Style Function Declaration (added in Verilog-2001)

function automatic range_or_type function_name (

input range_or_type port_name, port_name, ... ,

input range_or_type port_name, port_name, ... );

local variable declarations

procedural_statement or statement_group

endfunction

Old Style Function Declaration

(port declarations determine the order signals are passed into the function)

function automatic [range_or_type] function_name;

input range_or_type port_name, port_name, ...;

input range_or_type port_name, port_name, ...;

local variable declarations

procedural_statement or statement_group

endfunction

```

#### **Functions:**

- Must be declared within a module, and are local to that module.

- Return the value assigned to the function name.

- May be called any place an expression value can be used.

- Must have at least one input; may not have outputs or inouts.

- May not contain time controls or non-blocking assignments.

**automatic** (optional) allocates storage space for each function call, allowing recursive function calls. Automatic functions were added in Verilog-2001.

<code>range\_or\_type</code> (optional) is the function return type or input type. The default is a 1-bit reg. <code>range\_or\_type</code> can be:

- signed [msb:/sb]

- reg signed [msb:lsb]

- integer, time, real or realtime

**signed** (optional) indicates that the return value or input values are interpreted as 2's complement signed values. Signed functions were added in Verilog-2001.

```

Example of a Function

function automatic [63:0] factorial (input reg [31:0] n);

if (n<=1) factorial = 1;

else     factorial = n * factorial(n-1); //recursive call

endfunction

if ( factorial(data) <= LIMIT ) //function call</pre>

```

#### 14.1 Constant Functions

Constant functions (new in Verilog-2001) are functions with restrictions so that the function can be evaluated at elaboration (before simulation starts running).

- Only locally declared variables can be referenced. Net types cannot be used.