# Freedom CPU Project

# F-CPU Design Team

traduction du Patch YG 2001.1.14

# FCPU MANUAL REV. 0.2.2 $\beta$

"Design and let design"

$Please\ venez\ nous\ voir\ sur\ \texttt{http://www.f-cpu.org}\ et\ envoyez\ vos\ commentaires\ sur\ la\ liste\ de\ diffusion\ F-CPU$

f-cpu@egroups.com.

# 0.1 Copyright et licence de distribution :

Ce manuel est distribué sous les termes de la GFDL ou "GNU Free Documentation License", dont le texte peut être trouvé sur le site web GNU (http://www.gnu.org). Une copie de cette licence est inclue dans ce paquetage. (fdl.htm).

Copyright (c) 1999-2000 The F-CPU Group Design Team.

Permission is granted to copy, distribute and/or modify this document under the terms of the GNU Free Documentation License, Version 1.1 or any later version published by the Free Software Foundation; with no Invariant Sections, no Front-Cover Texts, and no Back-Cover Texts. A copy of the license is included in the section entitled "GNU Free Documentation License".

# 0.2 Avant-propos:

Tout ce qui se trouve dans ce document est sérieusement préliminaire et peut changer sans préavis. Please restez en contact avec le groupe sur la liste de diffusion et contrôlez les dernières mises à jour sur le site web F-CPU officiel.

Ce document est (C) 1999-2001 The F-CPU Group Design Team et est un travail collaboratif. Tout le monde peut participer à l'effort F-CPU et devenir un membre du groupe en s'incrivant sur la liste de diffusion et en prenant par aux discussions. Vous pouvez même participer sans vous inscrire mais vous êtes fortement incités à soumettre vos idées et reporter les erreurs. Nous sommes conscients que ce document contient des erreurs mais nous travaillons dessus constamment.

Ce manuel a été transformé en plusieurs formats de fichiers mais il peut y manquer des parties ou contenir des erreurs. Il est très incomplet, même s'il commence à devenir énorme!

# 0.3 Historique des versions:

- \* Créé le 8 Juillet 1999 par whygee@f-cpu.org (Yann Guidon) á partir d'extraits des RFC de Mathias Brossard.

- \* 10 Juillet: quelques ajouts.

- \* 11: adapté pour la conversion vers PDF avec HTMLDOC.

- \* 2/8, 8/8, 9/8, 13/8: ajout supplémentaire.

- \* 25/8: retravaillé un peu (pourquoi-comment, TTA, endianness, mémoire paginée, jump station...)

- \* 5/11: mélange avec d'autre contenus autres qu'architecture.

- \* 16/11: retour au format HTML.

- \* 27/2: version majeure pour le codage d'instruction. Imm6 disparait et la plupart des anciennes erreurs et fautes de frappe.

- \* 15/3: Adapté pour le macro processing par CPP

- \* 18/12/2000: Olivier Jean a finalement publié la version Latex du manuel

- \* 24/12/2000: YG l'a patché. très incomplet!

- \* 30/12/2000: YG l'a repatché à Berlin.

- \* \*/01/2001: début de la traduction française, redessinage des illustrations, mise à jour majeure...

Un tas de commentaires sont aussi donnés par d'autres personnes, quelquefois anonymes, sur la liste de diffusion.

# 0.4 Manque:

- \* jeu d'instruction découpé en fichiers séparés dans un répertoire spécial.

- \* carte du jeu d'instruction dans l'ordre alphabétique

- \* table du jeu d'instruction, triée par valeur opcode en hexa.

- \* exemples dans les descriptions d'instructions

- \* IRQ/traps

- \* carte SR

- \* parties 8 et 9

- \* et plein d'autre choses!!!

# 0.5 Zone de sauts Hyperliens:

#### HTTP:

- \* Les principaux sites F-CPU: http://www.f-cpu.orget http://www.f-cpu.de

- \* La dernière mise à jour du Manuel F-CPU: http://www.f-cpu.seul.org

#### Les listes de diffusion:

- \* http://www.eGroups.com/list/f-cpu (liste principale)

- \* http://www.eGroups.com/list/f-cpu\_france (liste française)

- \* http://www.eGroups.com/list/fcpu-ger (liste allemande)

# Table des matières

|    | 0.1 Copyright et licence de distribution:                                            | 2               |

|----|--------------------------------------------------------------------------------------|-----------------|

|    | 0.2 Avant-propos:                                                                    | 2               |

|    | 0.3 Historique des versions:                                                         | 2               |

|    | 0.4 Manque:                                                                          | 3               |

|    | 0.5 Zone de sauts Hyperliens:                                                        | 3               |

| Ι  | Le Projet F-CPU, description et philosophie                                          | 8               |

| 1  | Description du projet F-CPU                                                          | 9               |

| 2  | FAQ                                                                                  | 12              |

| 4  | 2.1 Introduction                                                                     | $\frac{12}{12}$ |

|    | 2.2 Philosophie                                                                      | $\frac{12}{12}$ |

|    | 2.3 Outils                                                                           | 14              |

|    | 2.4 Architecture                                                                     | 15              |

|    | 2.5 Performance                                                                      | 15              |

|    | 2.6 Compatibilité                                                                    | 16              |

|    | 2.7 Coût/Prix/Achat                                                                  | 16              |

| 3  | La genèse du projet F-CPU                                                            | 18              |

| J  | 3.1 L'Architecture CPU Libre: Un microprocesseur 64 bits GNU/GPL à haute performance | 10              |

|    | développé dans un environnement ouvert et collaboratif au travers du Web             | 18              |

|    | 3.1.1 Histoire                                                                       | 18              |

|    | 3.1.2 L'architecture GNU/GPL Libre                                                   | 19              |

|    | 3.1.3 Développer l'architecture Libre: versions et challenges                        | 19              |

|    | 3.1.4 Outils                                                                         | 20              |

|    | 3.1.5 Conclusion                                                                     | 20              |

|    | 3.1.6 Annexe A                                                                       | 21              |

|    | 3.1.7 Annexe B                                                                       | 22              |

|    | 3.1.8 Annexe C                                                                       | 23              |

| 4  | Un morceau d'histoire du F-CPU                                                       | 24              |

|    | 4.1 M2M                                                                              | 24              |

|    | 4.2 TTA                                                                              | 24              |

|    | 4.3 RISC Traditionel                                                                 | 27              |

| 5  | Les contraintes de conception                                                        | 28              |

| 6  | Cheminement du projet                                                                | 30              |

|    |                                                                                      |                 |

| ΙΙ | General description of the F-CPU  2.1 The main characteristics                       | <b>32</b> 33    |

|    | 2.2 The instructions are 32-bit wide                                                 | აა<br>33        |

|    | 2.3 Register #0                                                                      | 33              |

|    | 2.4 The F-CPU has 64 registers                                                       | 34              |

|    | 2.5 The F-CPU is a variable-size processor                                           | 35              |

|    | 2.6 The F-CPU is SIMD-oriented                                                       | 37              |

|    | 2.7 The F-CPU has generalized registers                                              | 37              |

|    | 2.8 The F-CPU has special registers                                                  | 37              |

|    | 2.0 The F-CPII has no stack nointer                                                  | 37              |

|    | 2.10 | The F-CPU has no condition code register                           | 38        |

|----|------|--------------------------------------------------------------------|-----------|

|    | 2.11 | The F-CPU is "endianless"                                          | 38        |

|    |      | The F-CPU uses paged memory                                        | 38        |

|    |      | The F-CPU stores the state of a task in Context MemoryBlocks (CMB) | 39        |

|    |      | The F-CPU can use the CMBs to single-step tasks                    | 40        |

|    |      | The F-CPU uses a simple protection mechanism                       | 40        |

|    |      |                                                                    |           |

| II | Ι (  | General description of the FCPU Core #0                            | <b>41</b> |

| 1  | Abo  | out the FC0 core                                                   | 42        |

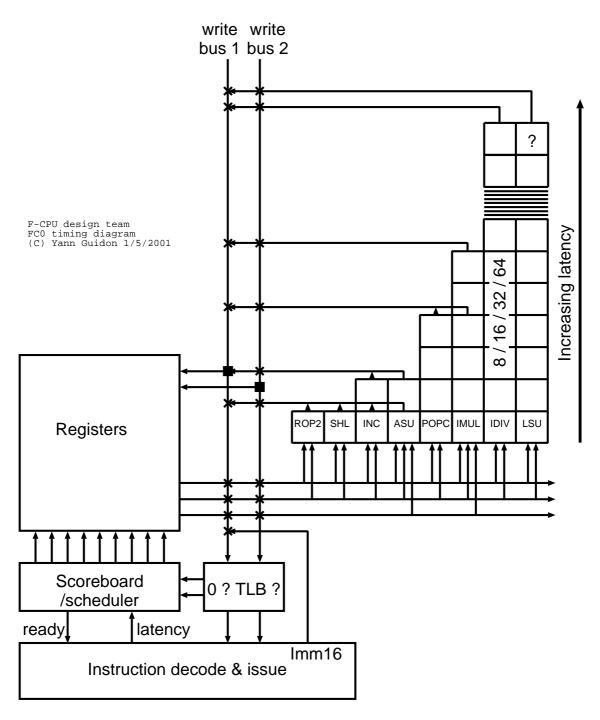

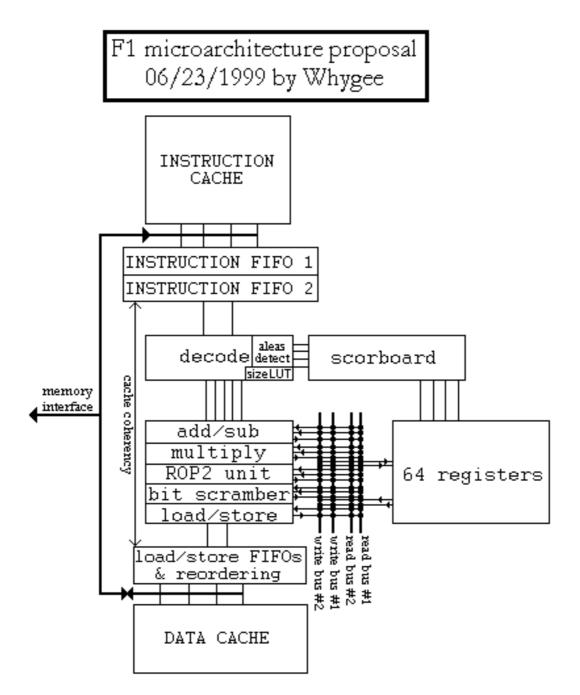

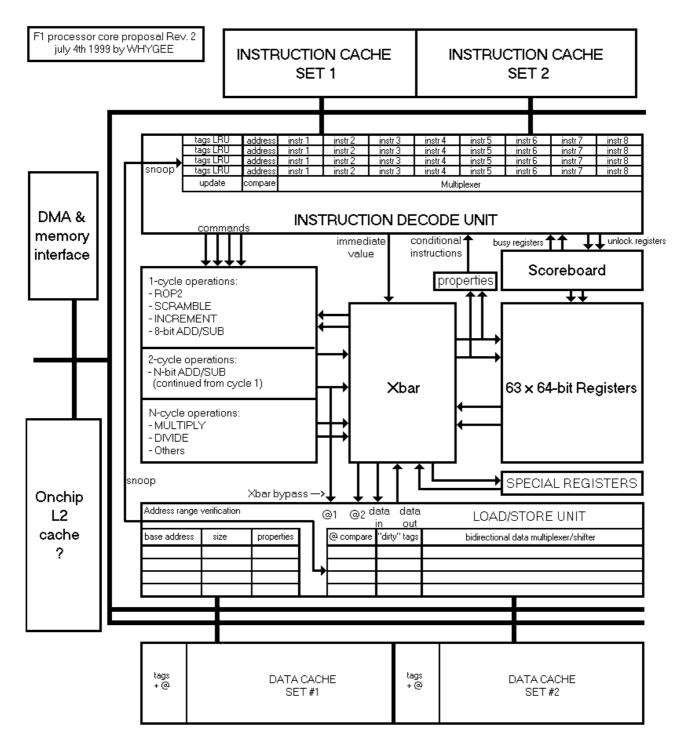

|    | 1.1  | The FC0 is superpipelined                                          | 42        |

|    | 1.2  | The FC0 core                                                       | 42        |

|    | 1.3  | The FC0 uses a scoreboard                                          | 43        |

|    | 1.4  | The crossbar                                                       | 44        |

| 2  | Evo  | lution of the FC0                                                  | 46        |

| 3  | The  | FC0 Execution Units                                                | 51        |

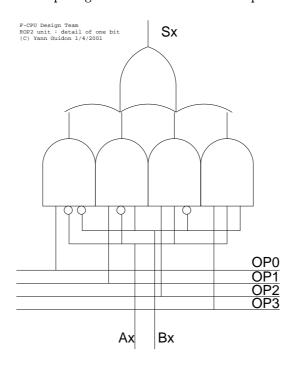

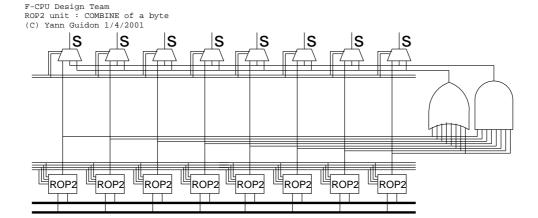

|    | 3.1  | The "logic" unit (ROP2)                                            | 51        |

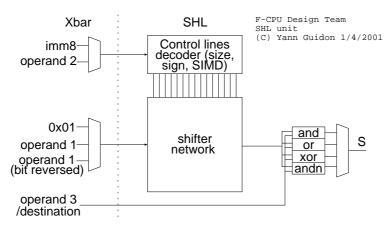

|    | 3.2  | The "bit scrambling" unit (SHL)                                    |           |

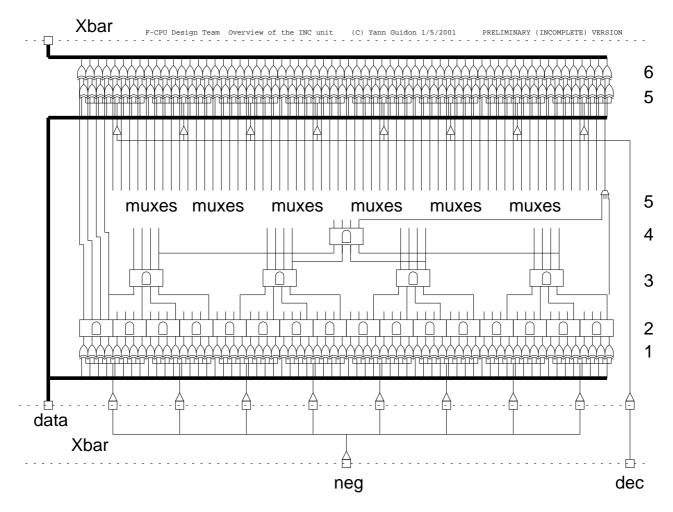

|    | 3.3  | The "increment" unit                                               | 53        |

|    | 3.4  | The add/sub unit                                                   | 55        |

|    | 3.5  | The integer multiply unit                                          | 55        |

|    | 3.6  | The integer divide unit                                            | 56        |

|    | 3.7  | The Load/Store unit                                                | 56        |

|    | 3.8  | Population count / Single Error Correction (POPC)                  | 56        |

|    | 3.9  | other units                                                        | 56        |

# Table des figures

| 1.1 | The pipeline is folded around the Xbar                                            |

|-----|-----------------------------------------------------------------------------------|

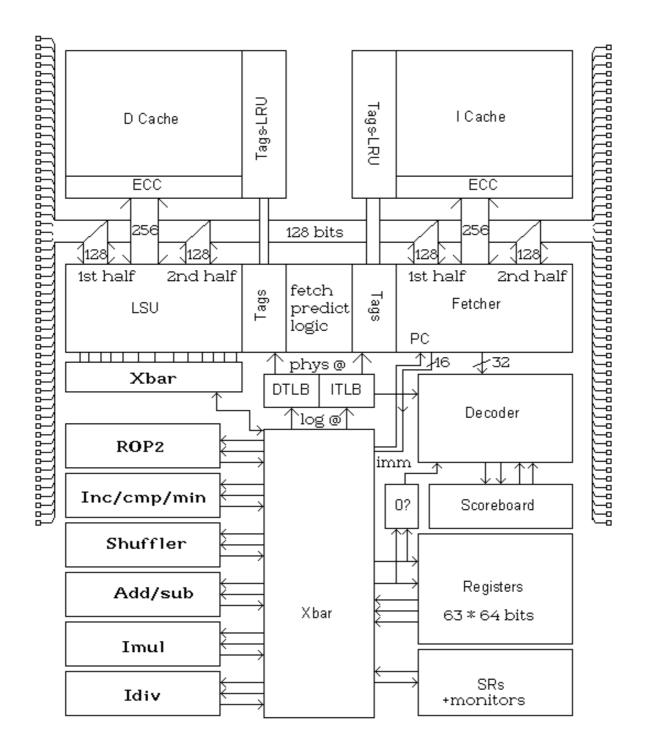

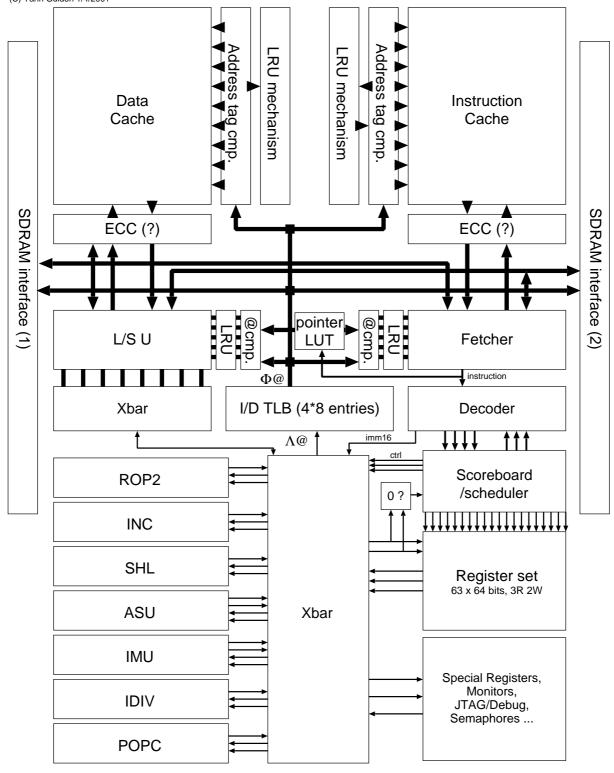

| 2.1 | The first F-CPU chip proposal                                                     |

| 2.2 | A more precise, first-attempt F-CPU description                                   |

| 2.3 | A third F-CPU description                                                         |

| 2.4 | The current F-CPU diagram                                                         |

| 3.1 | Detail of the ROP2 unit                                                           |

| 3.2 | Description of the COMBINE function on top of ROP2 for a byte-wide SIMD packet 53 |

| 3.3 | Overview of the Scrambling unit                                                   |

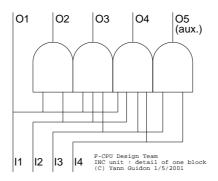

| 3.4 | Description of one block of the AND tree 54                                       |

| 3.5 | Overview of the Incrementer Unit (preliminary version)                            |

# Liste des tableaux

# Première partie

# Le Projet F-CPU, description et philosophie

# Chapitre 1

# Description du projet F-CPU

Il n'y a pas de description exacte du projet F-CPU. Cela n'est pas possible à cause de toutes les discussions des détails et de l'histoire du projet qui ont créé les spécificités de cette entreprise. Nous pouvons néanmoins souligner quelques points et faits importants.

L'architecture F-CPU définit un microprocesseur 64 bits SIMD, superpipeline. À aujourd'hui, c'est le seul CPU de ce type qui peut être complètement paramétré: il n'est pas limité aux implémentations 64 bits et il est prévu pour pouvoir s'étendre et grossir facilement. De plus, c'est le seul processeur de cette classe qui est diponible avec tous les sources (VHDL) et les manuels distribués avec la licence GNU (GPL et GFDL). Le but est de concevoir un processeur qui ne soit pas "encombré" par des brevets et qui puisse s'adapter au plus large choix de technologies possibles.

Le projet F-CPU est aussi formé par beaucoup de personnes dialoguant sur la liste de diffusion des les cotés organisationnels et techniques de la conception. Les listes de diffusion sont des endroits où le processeur est conçu de manière transparente à partir de réflexions contradictoires. Tout le monde peut y participer et influencer les spécifications si les modifications respectent les buts généraux du projet.

Le groupe F-CPU est un des nombreux projets qui tentent de suivre la voie montrée par GNU/Linux qui a prouvé que des produits non commerciaux peuvent surpasser les productions chères et propriétaires. Le groupe F-CPU tente d'appliquer les "recettes du Free Software" au monde de la conception électronique et surtout des ordinateurs en commençant avec le "saint gral" de toute architecture d'ordinateur: le microprocesseur.

Ce projet utopique était seulement un rêve au début mais après la séparation de deux groupes et beaucoup d'efforts, nous sommes parvenus à une assise assez stable pour une architecture developpable et propre sans sacrifier la performance. Nous espérons que la troisième sera la bonne et qu'un prototype sera créé bientôt.

Le projet F-CPU peut être séparé en plusieurs parties (aproximatives et non exhaustives) ou couches qui fournissent la compatibilité et l'interopérabiblité pendant la vie du projet (du Matériel vers le Logiciel) :

- \* bus, chipset, ponts F-CPU Périphériques et d'Interfaces...

- \* Implémentations individuelles des circuits Core F-CPU ou révisions (par exemple, F1, F2, F3...)

- \* Génération ou familles de Coeurs F-CPU (par exemple, FC0, FC1, etc.)

- \* Jeu d'instruction F-CPU et ressources diponibles pour l'utilisateur

- \* Interface Binaire F-CPU pour les Applications

- \* Système d'Exploitation (destiné aux clones Linux)

- \* Pilotes

- \* Applications utilisateurs

Toute couche dépend plus ou moins directement des autres. La partie capitale est l'architecture du Jeu d'Instructions car il ne peut pas être changé à volonté et ne fait pas partie du matériel qui peut évoluer lors des changements de ratios technologie/coût. D'un autre coté, le matériel peut fournir une compatibilité binaire mais les contraintes sont moins importantes. C'est la raison pour laquelle les instructions doivent tourner sur un grand panel de micro-architectures de processeurs où les "coeurs CPU" peuvent être changés ou swappés lors des changements de budgets.

Toutes les familles de coeur peuvent être compatibles binairement les unes avec les autres et exécuter les mêmes applications, faire tourner les même systèmes d'exploitations et délivrer les mêmes résultats avec différentes règles d'ordonnancement d'instructions, de registres spéciaux, de prix et de performances différentes. Chaque famille de coeur peut être implémentée avec des "ingrédients" différents comme le

nombre d'instructions exécuté par cycle, des tailles de mémoires, des tailles de mots mais le logiciel doit bénéficier de ces particularités sans (beaucoup) de changements. Ce document est une base d'étude et de travail pour la définition de l'architecture F-CPU, destiné au prototypage et la commercialisation de la première génération de circuits (nom de code "F1"). Ce document traite des bases techniques et de l'architecture menant à l'état actuel du coeur "FC0". Cela permet de réduire les discussions sur la base dans la liste de diffusion et informe les nouveaux (ou ceux qui reviennent de vacances) sur les concepts les plus récement traités. Ce manuel décrit la famille F-CPU au travers de son premier coeur et son implémentation. Le coeur FC0 n'est pas exclusif pour le projet F-CPU, qui pourra et devra utiliser d'autres coeurs lors de sa croissance et sa mutation. Le coeur FC0 peut aussi être utilisé pour à peu près toutes les architectures RISC similaires avec quelques adaptations.

Le document évoluera rapidement (nous l'espérons) et incorporera de plus en plus de discussions et de techniques avancées. Ce n'est pas un manuel définitif et il est ouvert à toutes les modifications que la liste de diffusion valide. Il n'est pas non plus exhaustif et peut être très en retard sur l'état du projet, en fonction des fluctuations de temps libre des contributeurs. Vous êtes fortement encouragés de contribuer au débat car personne ne le fera à votre place.

Quelques règles de developpement :

- \* Ce Projet est une expérience pour démontrer qu'il est possible de développer un processeur par Internet et dans un espace public. Les décisions sont faites par argumentations et consensus sur la liste de diffusion.

- \* Il n'y a pas de meneur ou de tour d'ivoire (ce n'est pas une "cathédrale"). En fait c'est une "Tour de Cristal" car tout est aussi transparent que possible. Tout le monde peut rejoindre l'équipe et contribuer ou même contribuer sans officiellement "rejoindre" l'équipe d'une quelconque manière. Même ceux dont la connaissance du développement d'un CPU est limitée ou nulle peuvent contribuer à leur manière (NdT: heureusement sinon vous ne liriez pas cette traduction).

- \* Le but du jeu est la Liberté; le processeur est développé de manière ouverte et sera distribué selon les termes de la GNU Public License (GPL), pour que toute personne ait la possibilité (si elle en a au moins les finances) d'utiliser cette création, de la fabriquer et de vendre ses propres F-CPU et ses dérivés pourvu que les modifications restent libres. Lisez la GNU Public Licence et la charte F-CPU pour plus de détails.

- \* Nous sommes conscients de l'ambition extrême de ce Projet mais nous pensons qu'il est la nécessaire extension du mouvement du Logiciel Libre dans un monde de matériel propriétaire omniprésent. Nous perséverons donc jusqu'à la réussite.

- \* Nous somme aussi fatigué d'utiliser du matériel propriétaire dont nous ne pouvons pas influencer la plateforme. En tant qu'utilisateurs, nous comprenons que le Logiciel Libre ne peut s'épanouir sans Plateforme réellement Libre.

- \* Rappelez-vous qu'au Freedom CPU Project nous ne somme ni anti-Intel, ni anti-Microsoft, ni, en fait, anti-quelquechose. Nous ne sommes que pro-liberté!

- \* Dans le groupe de développement, ne massacrez pas, ne répondez pas à une tentative de massacre mais priviégiez et tenez compte des critiques constructives!

- \* "Design and let design" (concevez et laissez concevoir) pourrait résumer la plupart des comportements adoptés dans le groupe. Quelques désaccords puissants sont apparus et apparaîtrons pendant les échanges mais que le sujet soit à propos de F-CPU ou non, tout le monde a le droit d'exprimer ses idées. Ne forcez pas l'accord des autres mais dialoguez de manière constructive et explorez le sujet, plutôt que dénigrer les idées des autres. Une bonne architecture peut aboutir d'un respect mutuel, pas de guerres de dénigrements.

# Chapitre 2

# **FAQ**

Collecté à partir de différentes sources. Dernière modification effectuée par Whygee, le 14 janvier 2000

# 2.1 Introduction

# Q1: Qu'est-ce que F-CPU?

A : F-CPU est essentiellement un microprocesseur SIMD, 64 bits, superpipeline; disponible avec le code source VHDL'93 et distribué sous les termes de la GNU Public Licence. Il est developpé par une communauté de hobbyistes, étudiants et professionnels sur Internet.

$\underline{\rm Q2}$ : Pourquoi un CPU RISC 64 bits? Je veux faire un clone x86 / une carte son / un RISC 32 bits pour l'embarqué...

A: http://www.opencollector.org

L'objectif de concevoir un CPU 64 bits haute performance remonte aux origines du projet lorsque les fondateurs voulaient contrer le Merced (ia64). Si vous souhaitez concevoir autre chose, il y a de grandes chances qu'un projet existe déjà avec un objectif se rapprochant du vôtre. OpenCollector est un des sites web qui répertorie les projets "libres" auquels vous pouvez avoir accès sur Internet. Si vous ne trouvez pas ce que vous voulez, n'hésitez pas à créer votre propre projet.

Il existe déjà beaucoup de projets de CPU libres disponibles sur Internet. Si vous ne désirez qu'un CPU 32 bits, MIPS/DLX et LEON sont des bons points de départ, même si F-CPU peut être facilement adapté à des mots de 32 bits seulement. Si vous désirez un microcontrôleur 16 ou 8 bits, il existe aussi beaucoup de versions libres (distribuées avec des licences variées). Vous n'avez qu'à en choisir un dans la liste du site web OpenCollector. Si vous êtes sûr que vous voulez un processeur tel que F-CPU, veuillez lire le présent manuel avant de vous investir trop vite dans le projet. Les buts généraux du projet sont fixés et ne changeront pas au gré des souhaits personnels.

# 2.2 Philosophie

#### Q1: Que signifie le F dans F-CPU?

A : Il signifie Freedom (liberté), qui est le premier nom de l'architecture ou Free (libre), dans le sens GNU/GPL.

Le F ne signifie pas qu'il est donné ou gratuit mais qu'il est "librement copiable et modifiable" (NdT: pourvu que l'on respecte la GPL). Vous devrez payer pour le circuit intégré, comme vous payez aujourd'hui pour une distribution GNU/Linux sur CD-ROM. Bien sûr, vous êtes libre de prendre les sources du circuit pour que votre fondeur favori vous fabrique des séries de F-CPU pour votre propre usage, en tant que tel ou intégré dans un autre produit.

## Q2: Pourquoi ne pas l'avoir appelé O-CPU (où O signifie Open)?

A: Il existe des différences philosophiques fondamentales entre le mouvement Open Source et le mouvement Free Software. Nous aspirons aux orientations de la FSF.

Le fait qu'une partie de code soit labellée Open Source ne signifie pas que la liberté de l'utiliser, de la comprendre et de l'améliorer vous soit garantie. De plus amples détails peuvent être trouvés sur http://www.gnu.org.

Nous avons tenté de créer une licence similaire à la GPL (GNU Public Licence de la Free Software Foundation) (voir http://www.opencollector.org/hardlicense/) mais cet effort a été abandonné car il ne semble ni nécessaire, ni utile. Aujourd'hui, elle est remplacée par une charte externe qui renforce et précise la signification de la GPL dans le cadre du monde de l'électronique industrielle.

D'un manière spécifique, il existe au moins trois niveaux de liberté qui doivent être préservés à tout prix:

- Liberté d'utiliser la Propriété Intellectuelle : aucune restriction ne doit exister pour utiliser le travail du projet F-CPU. Ceci signifie aucun péage pour l'accès au données et TOUTES les informations pour recréer un circuit doivent être fournies.

- Liberté d'analyser, de comprendre et de modifier la Propriété Intelectuelle à volonté. On peut remarquer qu'avec les sources, cela est beaucoup plus facile et rapide que pour un circuit déjà compilé ou synthétisé.

- Liberté de redistribuer les fichiers source.

Les sources ou tous les fichiers du projet ne sont PAS versés dans le domaine public. Les participants au projet F-CPU jouissent des droits d'auteur sur leurs créations et ils choisissent de les rendre librement disponibles à tout le monde par tous les moyens, à condition de respecter certaines règles. Chaque fichier créé à partir des fichiers sources du F-CPU conserve le Copyright du groupe F-CPU. Vous pouvez en lire plus sur htpp://www.gnu.org.

# Q3: Comment est protégée le F-CPU?

A: Le Groupe de Conception F-CPU protège ses travaux avec les lois sur le copyright. Chaque fichier contient la mention du copyright et de la GPL. Rien d'autre n'est nécessaire.

Des mesures additionnelles peuvent assurer qu'aucun dépot de brevet ne sera fait dans le futur. Les brevets sont connus pour leur inefficacité et leurs coûts élevés. Le Groupe de Conception F-CPU est protégé dans le sens où il ne fait que décrire le composant alors que les problèmes apparaissent lorsque le composant est fabriqué et vendu. Nous devons publier des documents pour prouver l'antériorité de nos idées, lors de conférences et dans la presse pour éviter les problèmes restants (et aussi pour nous faire mieux connaître). Le projet ne doit en aucun cas être encombré par des problèmes juridiques.

#### Q4: Et que ce passerait-il si je brevetais une fonctionalité du F-CPU?

A: Vous perdriez simplement du temps et de l'argent.

D'abord, l'architecture générale est basée sur des techniques connues et étudiées parfois depuis trente ans. Vous aurez beaucoup de mal à expliquer ce qui est suffisamment nouveau pour justifier un brevet.

Ensuite, si le brevet est accepté, personne n'acceptera de payer des royalties sur quelque chose qui a été volé au groupe F-CPU. Poursuivre ceux qui vont implémenter ces parties ne mènera à rien puisque le brevet sera contesté et, à la fin, vous possèderez un brevet inutile qui ne vous donne que des problèmes. Vous auriez mieux fait, pendant ce temps-là, de travailler à votre propre circuit.

## Q5: Pourquoi mon entreprise devrait-elle utiliser le F-CPU plutôt qu'un autre CPU?

A: Les avantages techniques du F-CPU sont décrits dans ce manuel: possibilités d'extension et orthogonalité extrême, conception propre et libre de brevets, accent mis sur la performance et la simplicité, l'implémentation aisée avec différentes technologies (FPGA/ASIC...)

Néanmoins, vous serez certainement encore plus sensible aux cotés non-techniques du projet si vous voulez intégrer un coeur F-CPU dans votre projet. Les fichiers sources peuvent être disponibles sans frais mais cela n'est pas la seule signification de "libre" pour F-CPU. C'est une conception transparente, pas une "boite noire" embrouillée par une équipe propriétaire et fermée. Si vous avez des problèmes avec le F-CPU (par exemple, si la version est obsolète, abandonnée par l'entreprise ou qu'elle a abandonné le produit, en résumé: vous restez seul avec le produit) vous n'avez pas à faire de reverse engineering sur la "boite noire" pour trouver ce qui ne va pas. Vous lisez simplement les sources et les corrigez (ou les patchez si un correctif existe). F-CPU est distribué sous les termes de la GPL qui vous donne le droit de comprendre et de modifier (personnaliser) les fichiers. Vous pouvez en plus participer au projet dans son ensemble, interagir avec les développeurs, soumettre et obtenir des patch preque en temps réel sur Internet.

Un autre aspect concerne les frais légaux. De même que la GPL est parfois appelée un "gentleman agreement", le F-CPU est un "gentleman CPU". Nous encourageons la collaboration pacifique entre les équipes: plus d'argent peut être dédié à la recherche et la conception, moins d'argent pour les avocats. A la fin, tout le monde gagne puisque le groupe des utilisateurs/développeurs F-CPU devient plus important et passe tout son temps à améliorer la qualité des sources, ce qui accelère la mise sur le marché de nouveaux produits. "Design and let design": les seules choses intéressantes et déterminantes sont les temps de réaction et l'efficacité (coût, performance, facilité d'utilisation) du produit et des équipes.

#### Q6: Cool mais où est le truc? Quels sont les inconvénients?

A: Ils sont bien connus et se trouvent dans la GPL et dans la charte F-CPU. De même que les sources sont disponibles librement, vous devez les maintenir libres et redistribuer toutes les modifications et additions faites au coeur. F-CPU (comme tous les projets GPL) étant basé sur la collaboration/coopération et non la compétition, vos mises à jour vont bénéficier aux autres mais ils peuvent toujours les améliorer et vous en bénéficierez en retour.

Si vous devez garder vos travaux complétement secrets, n'intégrez pas le F-CPU dans votre projet pour le modifier. Vous ne pourrez pas bénéficier du travail et de l'expérience des autres. Vous aurez à réinventer la roue et perdrez du temps et de l'argent.

# 2.3 Outils

#### Q1: Quel outil EDA allez-vous utiliser?

A: Il y a déjà eu beaucoup de débats sur ce sujet. C'est principalement une guerre entre Verilog et VHDL. Nous avons démarré avec VHDL'93 par commodité car c'est le plus utilisé en Europe (où la plupart du code est écrit) mais les fichiers seront certainement traduits en d'autres formats. Actuellement, les sources n'existent en VHDL que par commodité et uniformité. Les autres représentations en seront dérivées.

Maintenant que VHDL est le langage majeur, le choix des outils logiciels est plus limité. Nous voulons promouvoir des logiciels GNU mais cette branche n'est pas encore suffisamment developpée ou mature actuellement. Un logiciel spécifique peut être difficile à installer, un autre peut être instable, trop vieux ou incompatible avec les standards et besoins actuels.

L'utilisation d'Alliance (http://www-asim.lip6.fr/alliance/) est envisagé mais il ne sera utile que pendant le processus du layout pour une version "full custom". Les autres outils de conception libre peuvent être trouvés sur http://www.opencollector.org.

En ce moment, nous utilisons Simili (http://www.symphonyeda.com) sur la plateforme Win32. Ce n'est pas un logiciel GNU mais il a beaucoup d'avantages que l'on ne retrouve nulle part actuellement, comme l'indépendance par rapport aux constructeurs, le respect presque total des standards IEEE, la facilité d'utilisation, la compacité... Nous espérons un portage Unix dans le futur, de même que d'autres bons logiciels EDA GNU.

Les sources ont aussi été compilées sans modifications avec FreeHDL et Modelsim. D'autres compilateurs compatibles IEEE vont certainement confirmer la haute portabilité et la qualité des sources.

Cadence a proposé des licences gratuites pour quelque uns de ses outils. D'autres offres vont probablement suivre et sont les bienvenues tant que les contreparties sont compatibles avec la charte

F-CPU.

Nous allons probablement utiliser des outils commerciaux à un moment ou à un autre car les fondeurs utilisent des logiciels propriétaires mais dans tous les cas, un crayon, une feuille de papier et un cerveau sont les ingrédients les plus importants pour concevoir un circuit.

# 2.4 Architecture

Q1 : Quelle est cette architecture mémoire-à-mémoire dont j'ai entendu parler? Ou ce truc TTA? Pourquoi pas une architecture registre-à-registre comme tous les autres processeurs RISC?

A: M2M était une idée défendue au début du projet F-CPU. Elle avait quelques avantages sur l'architecture registre-à-registre, comme un délai de commutation de contexte très bas (pas de registre à sauver et restaurer). Aujourd'hui, le mécanisme SRB inclu dans FC0 résoud ces problèmes (voir Partie IV, chapitre 3, "Le mécanisme de Smooth Register Backup").

TTA est une autre architecture qui a été explorée avant que la conception actuelle de (FC0) ne soit démarrée.

L'architecture de F-CPU pourra évoluer dans le futur et emprunter quelques nouvelles fonctionnalités à d'autres architectures.

#### Q2: Envisagez-vous une FPU externe?

A : Non. la bande passante et le nombre de broches pose problème. Nous pouvons actuellement intégrer de telles unités dans une puce.

## Q3: Pourquoi ne supportez-vous pas le SMP?

A: Le Symmetric Multi-Processing tel qu'il est implémenté dans les PCs limite la performance et les possibilités d'extension de l'architecture. Nous cherchons activement d'autres architectures, principalement NUMA (Non-Uniform Memory Access) au travers d'un bus spécifique appelé F-BUS. Nous tentons d'éviter toutes les techniques complexes qui peuvent apparaître dans un système multi-CPU. Aucune décision ferme n'a été prise pour l'instant. Le coeur F-CPU est de toute manière indépendant de l'interface, tout type de connexion pouvant être implémentée.

# 2.5 Performance

# Q1: Que pouvons-nous espérer, en termes de performances, du F-CPU?

A: Merced-killer.:-). Plus sérieusement, nous espérons avoir de bonnes performances, bien qu'il soit impossible de faire une annonce avant d'avoir fait des mesures sur le circuit réel: ce serait une marque d'amateurisme et les performances dépendent largement des technologies disponibles, du budget, des contraintes et des besoins du fabricant.

Nous pensons pouvoir obtenir des bonnes performances car nous repartons de zéro avec une approche fraîche. x86 est relativement lent car il doit être compatible avec les anciens modèles. Les familles ARM, MIPS et SPARC vont avoir bientôt 20 ans, Power et Alpha/AXP approchent les 10 ans et nous pouvons tirer des leçons de leur évolution.

LINUX et GCC par eux-mêmes ne sont pas les meilleures garanties de performance. Par exemple, GCC ne traite pas les données SIMD. Nous allons certainement créer un compilateur qui est plus adapté au F-CPU et GCC sera utilisé au début comme "bootstrap" pour les logiciels existants. Le travail à venir sur les interfaces GNL et XML va probablement permettre aux développeurs de créer un meilleur code que GCC ne pourrait jamais le faire.

Objectivement, la famille de coeur FC0 est destinée à réaliser le meilleur ratio MOPS/MIPS possible. Le superpipeline garantit que la meilleur fréquence d'horloge est atteinte quelle que soit la technologie du circuit. La bande passante mémoire peut être virtuellement augmentée avec des stratégies d'"indices" explicites. Nous pouvons donc prévoir qu'un circuit à 100MHz avec 1 instruction décodée à chaque cycle peut facilement effectuer 100 millions d'opérations à la seconde. Ce qui n'est pas si mal du tout car vous pouvez l'obtenir avec une "anciènne" technologie silicium (bon marché) qui ne pourrait pas atteindre 100MOPS avec une architecture x86 pour le même prix. Ajoutez à ceci une largeur de donnée SIMD libérée de toute contrainte et vous avez une idée de la performance crête qu'il peut atteindre. Si vous voulez des chiffres parlants, avec la version 64 bits, les opérations SIMD sur des octets donnent 8 opérations par cycle, ou 800MOPS en pointe.

# 2.6 Compatibilité

#### Q1: F-CPU sera-t-il compatible avec les x86?

A: No. Ne. Nada. Niet. Nein. Non.

Il N'y aura PAS de compatibilité binaire entre F-CPU et les processeurs x86. Il pourra néanmoins faire tourner des émulateurs Windows qui incluent des émulateurs de CPU x86 comme Twin, de même que Windows lui-même sous tous les émulateur PC comme Bochs. Dans tous les cas, néanmoins, vous aurez besoin de faire tourner un autre système d'exploitation, comme GNU/Linux et l'émulation sera assez lente. Mais quel est l'intérêt d'utiliser Windblows alors que vous pouvez lancer GNU-Linux/xBSD à la place? ;-D

# Q2 : Aurais-je la possibilité de connecter un F-CPU dans un Socket 7, Super 7, Slot 1, Slot 2, Slot A standard ou sur toute autre carte mère existante?

A: Il y a de grandes chances qu'aucune version du F-CPU ne soit jamais disponible pour le Socket7 ou toute carte mère x86.

Raison 1: le BIOS doit être réécrit, les chipsets doivent être analysés et il existe trop de combinaisons chipsets/cartes mères. Cela est en dehors du champ du projet.

Raison 2: Socket/broches/bande passante: les circuits x86 sont réellement "memory-bound", la bande passante avec la mémoire est trop basse, de nombreuses broches ne sont pas utiles pour des circuits non-x86 et supporter toutes les fonctions de l'interface x86 rendra le circuit (sa conception et son débuggage) trop complexe, plus cher et plus lent.

Raison 3: nous ne voulons pas payer de licence pour l'utilisation de slots propriétaires.

Les slots ALPHA ou MIPS seront peut-être supportés. Nous pourrons inclure une interface EV-4 au F-CPU car de nombreux "chipsets" sont déjà disponibles pour le marché des cartes embarquées. Enfin, une interface personnalisé évitera tout problème de compatibilité et d'incompréhension. Si vous voulez connecter ou interfacer votre F-CPU sur quelque chose d'autre, "just do it".

# Q3: F-CPU supportera quel noyau d'OS?

A: Linux sera sûrement supporté en premier. Les autres portages suivrons et différents types de noyaux sont possibles. Mais avant cela, nous devons avoir un outil de développement de logiciel fonctionnel pour l'architecture. Nous devons donc définir complètement F-CPU en premier... Le kernel n'en est qu'au stade des discussions.

#### Q4: Quels programmes pourrais-je faire tourner sur F-CPU?

A : Nous avons un portage prototype/préliminaire de gcc/egcs pour l'architecture Freedom. Théoriquement, le F-CPU pourra exécuter tous les logiciels disponibles pour une distribution standard GNU/Linux, mis à part les parties bas niveau tels que I/O, code bootstrap ou écrit en assembleur.

Rappelez-vous que GCC n'est pas parfaitement adapté aux processeurs de cinquième génération (et plus). Nous l'avons adapté pour F-CPU mais c'était très difficile et il n'utilise qu'une petite partie des possibilités du jeu d'instruction et des ressources du F-CPU. N'attendez pas de performances extraordinaires d'un code généré ainsi, au moins pour le FCO.

# 2.7 Coût/Prix/Achat

#### Q1: Aurais-je la possibilité d'acheter un F-CPU un jour?

A: Nous l'espérons. C'est l'objectif du projet mais soyez patients et prenez part aux discussions! Si vous pensez qu'il n'est pas développé suffisamment rapidement, rejoignez le groupe et aidez nous. Avant que F-CPU n'existe en tant que circuit, il sera disponible sous d'autres formes telles que des émulations logicielles ou matérielles ou des simulations.

# Q2: Combien coûtera le F-CPU?

A: Nous ne savons pas. Cela dépend du nombre d'unités et de nombreux autres facteurs.

Il y a eu une estimation préliminaire optimiste qui donne aproximativement \$100 par unité pour un lot de 10000 circuits. Cela dépend aussi de beaucoup d'autres facteurs comme les performances souhaitées, la taille de la mémoire cache, le nombre de broches et surtout la possibilité de combiner tous ces facteurs dans les technologies disponibles. Les dernières estimations pour une première version limitée étaient autour de \$60 pièce pour un lot de 1000 ASIC. Le circuit FC0 ressemble à un

plus gros et simplifié. Il appartient à la classe des circuits à 1 million de transistors. C'est plus que le coeur LEON ou ARM mais c'est peu comparé aux autres circuits 64 bits haut de gamme. Il sera donc moins cher que ceux-ci.

# Chapitre 3

# La genèse du projet F-CPU

Ce chapitre provient essentiellement de la première période de F-CPU dont les auteurs sont mentionnés plus loin. Beaucoup de choses ont changé depuis que ce document a été écrit. La motivation n'a pourtant pas changé et la méthode est toujours la même. Les auteurs originaux sont maintenant injoignables mais nous avons continué de travailler de plus en plus sérieusement sur le projet. Au moment de l'écriture, plusieurs questions posées dans le texte suivant ont reçu une réponse mais maintenant que le groupe s'est lui-même structuré, les autres questions deviennent plus importantes car nous devons réellement y faire face : ce n'est plus une utopie, la fiction devient réalité.

N'oubliez pas que les éléments techniques qui sont décrit ici NE sont PAS réalistes et ne correspondent à rien de réel. C'est plus un rêve qu'une analyse cohérente. Please ne nous descendez pas pour les rêves des autres.

# 3.1 L'Architecture CPU Libre : Un microprocesseur 64 bits GNU/GPL à haute performance développé dans un environnement ouvert et collaboratif au travers du Web.

Auteurs: Andrew D. Balsa w/ plusieurs contributions de Rafael Reilova et Richard Gooch.

5 Août 1998

#### 3.1.1 Histoire

L'idée d'une conception de CPU GNU/GPL se trouve au milieu de quelques échanges de mails entre trois utilisateurs de longue date de GNU/Linux (aussi développeurs du noyau Linux à leurs moments perdus) avec diverse taches de fond.

Nous nous posions des questions sur les monopoles et comment la domination d'un système d'exploitation (incluant le noyau, l'Interface Graphique Utilisateur et la disponibilité de "killer-applications", de même que la documentation) était intimement reliée à la domination mondiale d'une architecture CPU spécifique, inefficace, dépassée et maladroite. Je suppose que vous devinez tous à qui je fais allusion.

Nous avons aussi exprimé notre croyance dans le fait que GNU/Linux est le mieux placé pour fournir les fondations de base pour un environnement logiciel totalement Libre (dans le sens GNU/GPL; please cherchez une copie de licence GNU GPL si vous lisez ceci ou allez sur www.gnu.org). Néanmoins, cette Liberté est limitée ou plutôt limité par le matériel propriétaire qui tourne dans beaucoup de maisons : le traditionnel PC basé sur le x86.

Finallement, nous étions inquiets de l'attitude de Intel qui ne fournit pas d'informations préliminaires à la communauté Free Software à propos de l'architecture du Merced à venir. Ceci a pour conséquence le retard du développement du compilateur gcc compatible, d'une version personnalisée du noyau Linux et finallement au vaste univers des outils Free Software. Il existe une vague rumeur que Linus Torvalds ait reçu des informations avancées sur Merced en signant un NDA Intel mais cela reste une exception individuelle et cela ne correspond pas à l'esprit du Logiciel Libre. Avec du recul, si Merced sera sûrement plus moderne que les architectures x86, il sera un pas en arrière en termes de Liberté car contrairement aux x86, il n'y aura sûrement pas de clone Merced.

Ces précédents jours, nous avons discuté sur les différents modèles de développement Free Software, leurs avantages et inconvénients. En rassemblant ces deux discussions ensemble, j'ai rapidement fait un brouillon d'une idée et l'ai posté à Rafael et Richard, les prévenant que cela serait bon à lire pendant

qu'ils compilaient XFree86 ou un gros package... et ils ont aimé! Ici, vous trouvez cette idée utopique, folle, mélangée avec des commentaires, des critiques et d'autres idées de Rafael et Richard:

# 3.1.2 L'architecture GNU/GPL Libre

Nous avons commencé avec quelques questions:

- Pourquoi ne pas développer un CPU 64 bits et mettre la conception sous GNU General Public License?

- Pourquoi ne pas rendre le processus de développement de ce nouveau CPU complètement ouvert et transparent, de manière à ce queque les meilleurs cerveaux du monde puissent contribuer avec les meilleures idées (d'une manière ou d'une autre, en utilisant les mêmes mécanismes de communication traditionnellements utilisés par la communauté Free Software)?

- Comment rendre le processus de développement du CPU entièrement démocratique et vraiment ouvert, là où il est habituellement entouré de paranoia et de secrets?

- Comment pouvons nous concevoir quelque chose qui améliorera les \*bases fondamentales de la technique\* de ce qui sera disponible en 2000 avec le groupe à l'architecture la plus avancée jamais rassemblée par aucune industrie (le Merced)?

Ici, on a deux incroyables challenges distincts:

- a) la performance et la faisabilité de l'architecture résultante et

- b) le processus de développement ouvert sous licence GNU/GPL et les questions de droits de propriété intellectuelle soulevés par ce procédé.

D'autres idées pour des architectures et des implémentations possibles peuvent être trouvées dans les annexes (de même que le coté "économique" du projet). Notez que nous appelons les architectures "Freedom" (pour des raisons évidentes), et sa première implémentation "F1". Le coût prévisionnel pour un utilisateur final d'un F1 est autour des \$100. Nous savons que tout est encore très utopique.: -)

Néanmoins, il nous semble qu'a ce point, les challenges réels à ce stade de notre projet sont entièrement dans b): le processus de développement et les versions des propriétés intellectuelles.

#### 3.1.3 Développer l'architecture Libre : versions et challenges

Le dessin Dilbert l'a résumé: en fait, notre projet \*est\* un paradigme en son entier! Ce qui nous proposons, en fait, est de rassembler les compétences et la puissance de création de milliers d'individus avec le web pour le processus de conception d'une architecture CPU GNU/GPL 64 bits avancée et Libre. Et nous ne savons même pas si c'est possible! Nous somme simplement sûrs de deux choses:

Dans le passé et le présent, les entreprises comme Intel, IBM et Motorola ont été connues pour avoir cassé des équipes de conception, de telle manière qu'aucun groupe (((((((((close)))))))))) ne puisse se former en étant capable de recréer entièrement les sources (et même quitter la firme et former leur propre compagnie). Récemment, Andy Grove a donné une nouvelle signification au mot "paranoia" comme outil de management. La proposition de notre environnement collaboratif, Libre, ouvert et transparent va à l'encontre de cette tendance. C'est aussi relié pour une grande partie à des tendances nouvelles dans les théories sur le management des Ressources Humaines et d'Organisation. En fait, c'est très collé au concept des Corporations Virtuelles, excepté que dans ce cas, nous parlons plutôt d'une Organisation Virtuelle à but non lucratif. De ce point de vue, le projet Freedom est aussi une expérimentation dans la théorie de l'Organisation mais cela n'est pas une expérience gratuite. Plusieurs études montrent que garder des personnes dans de petits groupes fermés, limités par des NDAs stricts et autres contraintes légales menant au silence en public et

imposer un haut niveau de pression sur ces groupes n'est pas le meilleur moyen pour libérer leur pouvoir créatif. Cela peut aussi mener à des conceptions erronées...

- Le développement du noyau Linux, par un groupe de programmeurs/développeurs système hautement talentueux, est un exemple: un environnement ouvert, collaboratif, destiné à un logiciel GNU/GPL avec un contenu à haute valeur intellectuelle/technologique peut être viable. De plus, il peut être démontré que dans certains domaines, le noyau Linux est plus performant que sa contre partie commerciale. Néanmoins, cette liste de certitudes est plutôt courte comparée à la liste des questions générées par nos propositions:

- Comment allons-nous écarter ou sélectionner les nouvelles idées pour les inclure dans la conception, parmi le "bruit" inévitable des Mauvaises Idées (tm)? Qui sera le juge de ce qui sera bon ou pas?

- Aussi, inévitablement, des options/fonctions mutuellement exclusives apparaitrons au cours du développement. encore une fois, qui décidera de la direction à suivre?

- Qui possèdera les droits finaux de la propriété intellectuelle? Le "copyleft" est-il applicable dans le cas de la conception de CPU? Qu'en est-il des masques pour les premier circuits?

- La GPL sera-t-elle suffisante comme instrument légal pour protéger les sources? Quels changements, s'il y en a, doivent être faits au GNU/GPL pour l'adapter à la conception de circuits?

- Si le processus de conception utilise des EDA commerciaux et d'autres outils, dans quelle mesure ces systèmes propriétaires "entachent" les sources GNU/GPL? Est-il possible de séparer la partie GPL de celle commerciale/propriétaire?

- Qu'en est-il des brevets existants? Le projet en aura-t-il besoin? Aura-t-il la possibilité d'en "acheter" ou de payer des royalties?

- Contrairement à un logiciel, des implémentations partielles des sources Freedom ne seront pas possibles. La première implémentation dans le silicium \*doit\* être fonctionelle et complète. Tous les "trous" dans la conception doivent être cablés avant que le premier masque ne soit dessiné. Comment faire pour que les volontaires acceptent un planning aussi rigide?

Il existe aussi quelques questions qui surviennent comme conséquence du possible succès de l'implémentation Freedom :

- Il y a de vastes possibilités pour des sources de CPU GNU/GPL dans l'industrie, le médical, l'aéronautique, l'automobile et autres domaines. En fait, une conception Libre, stable, haute performance offre des possibilités jamais encore imaginées par les concepteurs de matériel dans des domaines variés. Est-ce le début d'une petite révolution par exemple, dans le matériel embarqué?

- La conception va-elle se maintenir elle-même pendant des années comme le processeur idéal GNU/Linux?

- Cette expérimentation dans le développement ouvert aura-t-elle d'autres conséquences sur l'industrie électronique? Sommes-nous en train de proposer un nouveau paradigme pour le développement de CPU? Ce paradigme pourra-t-il être appliqué aux autres conceptions VLSI?

# 3.1.4 Outils

Mais nous avons aussi besoin de nouveaux outils qui n'existent probablement pas encore. Je pense qu'il faut mentionner que le premier pas dans cette direction est peut être le projet WELD, développé à Berkeley. Il pourrait très bien devenir la pierre d'angle du projet Freedom ou inversement, le projet Freedom pourrait être considéré comme le cas idéal de test pour le projet WELD.

# 3.1.5 Conclusion

La conclusion est simple et évidente:

- si vous êtes un ingénieur VLSI ou en architecture CPU, ou

- si vous avez une bonne idée sur la conception de CPU avec laquelle vous vous êtes déjà amusé pendant quelque temps et que vous voudriez tester, ou

si vous aimez simplement la stimulation provenant de propositions intellectuelles et d'interactions de reflexions:

Please rejoignez nous et aidez nous à transformer cette idée en réalité!

\*: Richard est un astrophysicien Australien préparant son Ph.D. sur la visualisation astronomique; Rafael est un chercheur sur outils EDA à l'Université de Cincinatti. Je suis un étudiant ex-Ph.D. en Management et un ingénieur ex-firmware, avec un intérêt particulier pour les problèmes éthiques dans les environnements multi-culturels (je suis né au Brésil et je vis actuellement en France). Aucun de nous n'a de formation spécifique en architecture CPU. Rafael s'en rapproche le plus, étant un concepteur VLSI et développeur d'outils EDA et il a aussi développé de nouveaux programmes pour la reconnaissance de CPU dans le noyau Linux. Richard a développé le portage du Pentium Pro MTRR dans les noyaux Linux 2.1.x (de même que de nouvelles routines de noyau), et c'est aussi un développeur de matériel. J'ai l'honneur d'avoir diagnostiqué le bug de "virgule" sur le Cyrix 6x86 et lui ait proposé une solution sous GNU/Linux (les deux étaient d'abord rejetés par Cyrix Corp.). Je suis aussi depuis longtemps un développeur de matériel et de firmware et j'ai contribué de différentes manières au développement de GNU/Linux (e.g. le HOWTO Linux Benchmarking).

Richard E. Gooch < Richard. Gooch@atnf.csiro.au>

Rafael R. Reilova < rreilova@ececs.uc.edu>

Andrew D. Balsa <andrebalsa@altern.org>

note: aujourd'hui aucune de ces adresses ne fonctionne. altern.org a même disparu.

#### 3.1.6 Annexe A

#### Idées pour la conception d'un processeur GPL 64 bits haute performance

C'est juste un rêve, une idée utopique de la conception d'un processeur libre. C'est aussi une liste des éléments que je souhaiterais avoir dans un futur processeur.

- Ce projet aurait besoin d'un sponsor si nous voulons qu'il devienne une réalité. Obtenir les premiers circuits ne permet ni de devenir libre, ni ne sera facile.

- Le choix d'un bus de donnée 64 bits pour l'espace d'adressage: c'est devenu évident et cela simplifie tout.

- Le débat RISC vs. CISC vs. flux de donnée est terminé! Prenez les avantages de chaque sans leurs inconvénients si possible.

- 1, 2 ou 4 pipelines 7-stages internes.

- Exécution spéculative: 4 branches, 8 profondeurs d'instruction pour chaque.

- Queue de pré-traitement d'instructions 64 octets.

- Buffer d'écriture 32 octets.

- Microprogramme partiellement en RAM. Nous devons être capable d'émuler le jeu d'instructions x86 (au niveau du code source assembleur).

- capacité d'interruption multiple 64 bits TSC w/.

- Système d'économie d'énergie.

- Émulation MMX et 3DNow!.

- Conception entièrement statique (possibilité d'arrêter l'horloge).

- Implémentation F1: bus de donnée externe 128 bits, capacité d'adressage externe de 40 bits.

- Registres de contrôle de performance à la Pentium.

- FPU externe, mémoire paginée (je n'ai pas idée à quoi cela peut ressembler). Les FPUs peuvent être additionnés pour le travail en parallèle (plus de 4?). Bus séparé. Le même bus peut traiter un coprocesseur graphique avec sa mémoire double.

- Caches L2 d'instructions et de données séparés de 64KB chaque, tournant à la vitesse du CPU.

- Contrôleur DMA intégré intelligent, 32 canaux.

- Contrôleur intégré d'interruption : 30 interruptions masquables, 1 interruption de la Gestion Système,

1 interruption non-masquable.

- Aucun registre interne! Oui, c'est une machine mémoire-mémoire. Le jeu d'instruction reconnaît 32 pseudo-registres à tout moment.

- Les interruptions commutent automatiquement le jeu de registre vers un jeu de registre vectorisé: pas de temps d'attente de commutation de contexte!

- Pas de pénalité pour les instructions qui accèdent des octets, des mots ou des mots doubles.

- Opérations dans le mode petit ou grand endian à la MIPS.

- Pagination à l'Intel, avec des pages de 4k + 4M d'extension.

- Aussi: VSPM à la Cyrix 6x86, avec des pages définissables de 1K.

- Registres ARR à la Cyrix 6x86 (similaire au MTRR sur Intel PPro): permet la définition de zones non cachables (utile pour NUMA, voir ci-dessous).

- PLL interne avec multiplicateur programmable par logiciel; peut commuter de 1x à 2x puis 3x puis nx avec des incréments de 0.5, à la volée.

- Le MMU doit aussi supporter la protection d'objet à la Apple Newton.

- Nom de projet de l'architecture CPU: "Freedom". Peut aussi être appelé "Merced-killer" ou "Anti-Merced" ou "!Merced" mais en fait nous ne sommes contre personne dans ce projet. Nous sommes simplement pro-liberté et ouverts; ce que nous détestons sur le Merced d'Intel, c'est sa conception propriétaire et son environnement de développement resteint. Ici, je suppose que le challenge est de déterminer comment la conception d'un CPU GPL est faisable. Est-ce qu'un développement collaboratif et ouvert d'un CPU WRT est possible? Comment fait-on avec le fondeur pour réellement mettre les sources sur le silicium, une fois que tout est prêt? Comment traite-t-on les révisions? Existe-t-il des brevets qui vont bloquer un tel processus de développement?

Aussi, l'idée est d'utiliser gcc comme compilateur idéal de développement pour ce type de CPU (contrairement au Merced). Et pour être à même de porter le noyau Linux avec un effort minimum sur ce nouveau processeur.

# 3.1.7 Annexe B

# surface de la puce / coût / caractéristiques physiques du boitier / bus externe pour le Freedom-F1

Simplement pour rappel, le CPU F1 n'inclue pas de FPU ou d'unité 3DNow! (mais des instructions entières SIMD seront incluses).

Taille maximum recommandée: 122 sq. mm. Ceci nous donne 200 wafer dies/8-inch (voir un exemple d'un tel wafer sur Hennessy et Patterson, page 11).

Grosso modo, die yield = 0.5 pour notre 122 mm2 5-couches 0.25 micron CPU (H AND P, page 13, mis à jour pour refléter de meilleures fabrications). Ceci permet plus ou moins 10-11 millions de transistors, divisé comme suit : 6-7 millions pour les caches, 4-5 millions pour le reste.

Supposons un wafer avec un yield = 95, et au test final: yield = 95. Coûts de tests de \$500/heure, 20 secondes/CPU.

Coût du boitier = \$25-50 (voir ci-dessous).

Grosso modo, suivant H et P, ceci nous donne un coût unitaire de \$75-100/bon CPU, testé, conditionné dans des supports anti-statiques et transporté vers les US, si les fondeurs Taiwannais peuvent garder le processus de wafer autour des \$3.500.

Boitier: Je vais proposer quelque chose de surprenant mais je pense que nous devrions utiliser le même boitier que le Celeron, en terme de dimensions physiques et de placement. De cette manière, nous pourrons utiliser les radiateurs/ventilateurs du Celeron déjà sur le marché et le matériel de montage du Celeron

Jeu PCI: je vais encore proposer une hérésie mais je pense que nous pourrions utiliser les cartes mères Slot 1 à 100MHz. En premier, Intel n'est plus le seul à fabriquer les chipsets Slot 1: VIA vient juste de sortir un chipset Slot 1 avec des performances excellentes et les dernières améliorations en terme de technologie (nous pouvons avoir les informations de synchronisation sur les datasheets des chipset VIA). En second, nous n'avons plus besoin de nous inquiéter sur l'avenir du jeu carte mère/PCI. En troisième, il est à peu près impossible d'aller au-delà des 100MHz sur une carte mère standard à cause des émissions

Maintenant, si nous acceptons ce qui est au-dessus, nous devons mettre sur le circuit imprimé du Freedom une petite EEProm qui contiendra le BIOS Freedom, le cache L2 et un socket pour le FPU. Ceci augmente le coût du CPU mais diminue le coût global donc je pense que c'est un bon mouvement.

Please regardez une photographie du Celeron et dites moi si je suis en train de réver.

#### 3.1.8 Annexe C

#### Emissions légales / financières

5 Août 1998

Nous souhaiterons avoir un support de la Free Software Foundation pour le projet Freedom.

Nous ne proposons pas que la Free Software Foundation construise une usine. Ce que nous proposons c'est que: si nous voyons des fondeurs aux US ou Taiwan, leur donnons un masque et leur demandons de faire un batch de 0.25 micron, 5 couches sur wafer 8-inch pour nous, qu'ils nous épaulent à hauteur de approximativement \$3K-5K ou même moins, par wafer, sur leurs prix (notre coût) pour nos batchs (dans l'année 2000).

Un coût approximatif pour un batch de CPU F1 tournera autour de \$500k et \$1000K, pour 5000-10000 CPUs on.

Ce n'est pas exactement de l'agent de poche mais nous pouvons vendre ces CPU sur une base de souscription. Comme ceci: les personnes qui y souscrivent auront le Merced-killer pour à peu près \$100 (comparé au coût prévu de \$5000/unité pour le Merced), sur une base de premier arrivé/premier servi et tout les CPU restants après les coûts de couverture du batch pourraient être vendus à un coût légèrement supérieur pour payer les batchs suivants et d'autres développements de masques.

Nous suggérons de mettre quelques quotas dans le système. La demande est susceptible d'être supérieure à l'offre. ;-)

La Free Software Foundation pourrait coordiner tous les aspects légaux/financiers/logistiques du projet (et auront une compensation adéquate pour ce travail). Ceci, bien entendu, dépend de l'obtention du support de Mr. Stallman pour cette initiative.

# Chapitre 4

# Un morceau d'histoire du F-CPU

(Et une réflexion sur l'évolution du F-CPU au travers d'un description des différentes architectures proposées.)

#### 4.1 M2M

La première génération était une architecture "mémoire à mémoire" (M2M) qui a disparu avec les membres de l'équipe originale (ils ont écrit le texte précédent). Ils pensaient que le temps de commutation de contexte prenait beaucoup de temps, ils ont donc réservé des zones de mémoire pour le jeu de registres. De cette manière, ils pouvaient changer de registres en changeant leur adresse de base. Je n'ai pas recherché les raisons pour lesquelles ceci a été abandonné car je suis arrivé plus tard dans le groupe. De toute manière, ils ont lancé le projet F-CPU, avec les buts que nous connaissons maintenant et le rêve de créer un "Merced Killer". Je pense que nous pouvons réellement nous mesurer avec l'ALPHA directement;-)

# 4.2 TTA

La seconde génération était la "Transfer Triggered Architecture" (TTA) où les calculs étaient déclenchés par les transferts entre les différentes unités d'exécution. Les instructions consistent principalement en des nombres correspondant aux "registres" de source et de destination, qui peuvent être des ports d'entrée ou de sortie d'unités d'exécution. Dès qu'il est écrit quelque chose dans les ports d'entrée d'une unité, l'opération est effectuée et le résultat est lisible sur le port de sortie. Cette architecture a été proposée par AlphaRISC l'anonyme, aussi connu comme AlphaGhost. Il a fait un gros travail dessus mais il a quitté la liste de diffusion et le groupe a perdu la piste du projet avec lui.

Brian Fuhs (bkfuhs1@attglobal.net) a expliqué le TTA sur la liste de diffusion de cette manière:

TTA signifie Transfer-Triggered Architecture. L'idée de base est de ne pas dire au CPU ce qu'il doit faire des données, mais seulement où les mettre. Alors, en positionnant les données aux bons endroits, vous récupérez magiquement de nouvelles données à d'autres endroits qui résultent d'opérations effectuées sur les anciènnes données. Alors que sur une machine traditionelle OTA (operation-triggered architecture), vous devez dire "ADD R3, R1, R2"; dans une TTA, vous diriez "MOV R1, add; MOV R2, add; MOV add, R3". L'intérêt du jeu d'instruction (si on peut dire, car le TTA n'a qu'une instruction : MOV) est sur la donnée elle-même, à l'opposé des opérations que vous faites sur la donnée. Vous spécifiez simplement les adresses puis vous cartographiez celles-ci en des fonctions comme ADD ou DIV.

C'est l'idée de base. Je devrais commencer en spécifiant que je me concentre ici sur le traitement global et j'ignore temporairement les choses comme les interruptions. De cette manière, il est possible de traiter les cas réels car personne ne l'a encore fait. Pour l'instant, je me suis plus intérressé à la théorie. Tout pipeline CPU peut être décomposé en trois étapes de base : approvisionnement et décodage, exécuter et stocker. Garbage in, garbage processing, garbage out. Avec les OTA, tout est fait par matériel. Vous donnez "ADD~R3,~R1,~R2" et le matériel fait le reste. Il traite les moyens de communication interne pour obtenir les données de R1 et R2 vers l'entrée de l'additionneur, le laisse traiter l'information et récupère les données à la sortie vers le fichier de registre, dans R3. Dans les architectures modernes, il contrôle les anomalies, fait suivre les données pour que le

reste du pipeline puisse l'utiliser plus tôt et truc encore plus compliqué comme réordonner les instructions. Le logiciel ne connait que le 32 bits ; le matériel fait le reste.

L'étape IF/ID d'un TTA est très différente. Toute la charge est placée sur le logiciel. L'instruction n'est pas spécifiée comme ADD (quelque chose), mais comme une série de paires d'adresses SRC, DEST. Tout ce que le matériel doit faire est le contrôle des bus internes pour mettre les données là où elles sont supposées aller. Toutes les vérifications de risque, d'ordre d'instructions optimal, etc doit être fait par le compilateur. Ici, la clé est qu'un TTA, pour réaliser des mesures IPC comparables à un OTA, doit être VLIW: vous DEVEZ pouvoir spécifier des mouvements multiples en un seul cycle, pour que vous puissiez déplacer toutes vos sources de données vers les zones appropriées et encore bouger les résultats vers votre fichier de registres (où là ou vous voulez qu'ils aillent). En résumé, pour faire un "ADD~R3,~R1,~R2", le matériel fera ce qui suit:

TTAOTA ADD R3, R1, R2 MOV R1, add Move  $R1 \rightarrow adder$ Contrôle de danger MOV R2, add Contrôle d'additionneur disponible Move  $R2 \rightarrow adder$ Sélectionne un bus interne et déplace la donnée (l'additionneur fait le traitement dans les deux cas) MOV add, R3 Contrôle de danger Move  $adder \rightarrow R3$ Planifie l'instruction pour la récupération Sélectionne un bus interne et déplace la donnée Abandonne l'instruction

Le compilateur, bien sûr, devient beaucoup plus compliqué car il doit faire tout le travail de planification, au moment de la compilation. Mais le matériel n'a pas besoin de s'occuper de grand chose dans un TTA... Tout ce qu'il fait dans les cas simple est d'envoyer les instructions et de générer les signaux de contrôle pour tous les bus.

L'exécution est identique entre le TTA et OTA. Crunch the bits. Period.

La complétion des instructions est encore simplifiée dans un TTA. Si vous voulez un comportement correct, assurez vous que le compilateur génère les bonnes séquences de déplacement. C'est à comparer avec un OTA où vous devez au moins savoir quels port d'écriture vous devez utiliser, etc.

A la base, un TTA et un OTA sont fonctionellement identiques. La principale différence est qu'un TTA doit vraiment être VLIW et demande plus au compilateur. Néanmoins, si la philosophie "smart compiler and dumb machine" est réellement là où l'on veut aller, le TTA doit fonctionner. Il offre une partie plus importante du pipeline au logiciel, réduisant les besoins de matériel et laissant plus de champ au compilateur pour l'optimisation. Bien sûr, il y a des cas comme les embouteillages de code et la génération de constantes, mais ces cas sont traités plus tard. Les idées de base ont été couvertes ici (quoique d'une manière assez décousue)... J'ai composé cet email dans ma tête et j'ai trouvé quelques explications claires directement lorsque je me suis assis et j'ai commencé à saisir). Pour plus d'informations, voyez http://www.cs.uregina.ca/~bayko/design/design.html et http://cardit.et.tudelft.nl/MOVE. Ceux-ci ont beaucoup plus d'informations sur les détails de TTA; j'espère encore que nous pourrons le mener à bien et je pense que cela sera bien pour la performance, générale, de coût et en simplicité. En plus, c'est suffisamment révolutionaire pour faire détourner les têtes -et que cela puisse nous donner une plus grande base d'utilisateurs (et de développeurs) et rendre le projet plus stable.

Envoyez moi les questions, je sais qu'il en a beaucoup ...

Brian

Si vous voulez comprendre le concept TTA un peu mieux, la différence est dans la philosophie, c'est comme si vous aviez des instructions pour coder le flux de données de la machine à la volée. Notez aussi le fait que moins de registres sont nécessaires: les registres sont requis pour stocker les résultats temporaires des opérations entre les instructions d'une séquence de code. Ici, les résultats sont directement stockés par les unités d'où un moindre besoin de "stockage temporaire" et moins de pression sur les registres.

Pour visionner cette différence, pensez au graphe de dépendance des données: dans un OTA, une instruction est un noeud alors que dans TTA l'instruction mov est la branche. Une fois que cela est compris, il n'y a pas beaucoup de travail à faire sur un compilateur existant (jusqu'ici simple) pour générer des instructions TTA.

Examinons: S = (a+b)\*(c-d) par exemple. a, b, c, d sont des "ports", des registres ou des adresses TTA connus.

```

ADD r5, a, b

SUB r6, c, d

MUL r7, r5, r6

```

(par exemple).

Dans TTA il y a un "port" dans chaque unité pour chaque branche entrante. Ceci signifie que ADD, ayant deux opérandes, a deux ports. Il y a un port de résultat qui utilise l'adresse d'un port mais qui est utilisé en lecture, pas en écriture. Un autre détail est que le port de lecture peut être statique : il contient le résultat jusqu'à ce qu'une autre opération ne soit déclenchée. Nous pouvons coder

```

mv ADD1,a

mv SUB1,c

mv ADD2,b (ceci déclenche l'opération a+b)

mv SUB2,d (ceci déclenche l'opération c-d)

mv MUL1,ADD

mv MUL2,SUB (ceci déclenche l'opération *)

```

Comme nous en avons parlé quelques fois, il y a longtemps, à cause de ses problèmes de croissance (assignation des ports et flexibilité), TTA n'est pas le choix parfait pour une famille de CPU sur le long terme alors que le ratio performance/complexité est bon. Il est donc possible que le groupe F-CPU travaille sur un traducteur RISC  $\rightarrow$  TTA devant un coeur TTA qui n'aura pas la plupart des problèmes de croissance. Il sera appelé le "FC1" (FC0 est le coeur RISC). Bien sûr, le temps montrera comment les fantômes TTA du groupe F-CPU changerons.

Mais le problème du TTA est trop spécialisé là où l'OTA peut changer son coeur et toujours utiliser les mêmes binaires. C'est un des points qui a "tué" la tentative précédente du F-CPU. Chaque implémentation TTA ne peut pas être complètement compatible avec une autre à cause du format des instructions, de l'assignation des "ports" et autres détails similaires: la notion "d'instruction" est liée à la notion de "registre".

Je ne suis pas en train de prouver les avantages d'une technique sur une autre, je tente de montrer la différence de point de vue, qui traite finalement du même problème. La croissance, qui est nécessaire pour un tel projet est plus importante que nous le pensons et le groupe s'est intérressé à une technologie plus classique lorsque AlphaRISC l'a quitté.

# 4.3 RISC Traditionel

La troisième génération est partie des membres de la liste de diffusion qui ont naturellement étudié les bases de l'architecture RISC, comme la première génération de processeurs MIPS ou le DLX (décrit par Patterson et Hennessy dans leur livre "QA"), le MMIX (Knuth), les CPUs MISC (tels que les machines Forth de Chick Moore ou le 4Stack de Bernd) et d'autres projets similaires simple. Ces conceptions sont expliquées et décrites dans des livres bien connus et enseignés en universités. A partir d'un simple projet RISC, le projet est devenu plus complexe et est devenu indépendant des autres architectures existantes, principalement grâce aux leçons apprises de leur histoire et des besoins spécifique du groupe, qui a mené vers des choix adaptés et des caractéristiques particulières. C'est ce dont nous parlons dans les parties suivantes de ce document.

# Chapitre 5

# Les contraintes de conception

Le groupe F-CPU est plutôt hétérogène mais chaque membre a le même espoir que le projet devienne une réalité car nous sommes convaincus que ce n'est pas impossible et donc faisable. Rappelez-vous la Constitution du Projet Freedom CPU:

Développer et rendre une architecture librement disponible, ainsi que toutes les propriétés intellectuelles nécessaires pour fabriquer un ou plusieurs implémentations de cette architecture, avec les propriétés suivantes, dans l'ordre décroissant d'importance :

- 1) adaptabilité et utilité pour le champ d'applications le plus grand possible

- 2) Performance, accent mis sur le parallélisme au niveau de l'utilisateur et dérivé avec une architecture intelligente, plutôt que par des processus avancés en electronique

- 3) Architecture (((((((((((((lifespan))))))))))) et compatibilité directe

- 4) Coût, incluant des considérations monétaires et thermiques

Nous pourrions aussi ajouter: 5) réussir!

Ce texte résume beaucoup d'aspects du projet : c'est une "propriété intellectuelle libre", signifiant que tout le monde peut faire de l'argent avec sans être inquiété, tant que le produit respecte les règles et les standards généraux décrits dans la charte F-CPU et toutes les caractéristiques sont librement disponibles (sous la GNU Public Licence et en respectant la charte F-CPU). Tout comme le projet LINUX, les membres du groupe espèrent que la libre disponibilité de cette conception bénéficiera à tout le monde en réduisant les coûts des produits (car la plupart du travail intellectuel est déjà réalisé), en fournissant un standard ouvert et flexible que tout le monde peut influencer à volonté sans signer de NDA. C'est aussi un banc de test de nouvelles techniques et le "premier CPU" pour un grand nombre de "passionnés" qui peuvent le construire à la maison. Bien sûr, les autres résultats sont que le F-CPU sera utilisé dans tous les ordinateurs familliaux ainsi que par tous les autres marchés spécialisés (embarqués/temps réels, ordinateurs portables/(((((((((((wearable)))))))))))))), machines parallèles pour le décodage de nombres scientifiques...).

Dans cette situation, il est clair qu'un seul circuit ne remplit pas tous les besoins. Il existe aussi des contraintes économiques qui influencent aussi les décisions technologiques et tout le monde ne peut pas accéder aux unités de fabrication des fondeurs les plus avancés. La réalité du F-CPU "pour et par tout le monde" est plus dans le royaume des FPGA reconfigurables, des ((((((((sea-of-gates)))))))))) bon marché et des ASICS qui seront fabriqués en petits volumes. Même si le but ultime est d'utiliser des technologies entièrement personnalisées, il existe une forte limitation dûe aux prototypes et aux faibles volumes. La complexité est limitée pour les premières générations et FCO, les estimations du nombre de transistors pour les premiers circuits seront de 1 Million, incluant un peu de cache. C'est plutôt faible comparé aux CPUs actuels mais c'est énorme si on se rappelle les coeurs ARM ou les premiers CPUs RISC.

La "Propriété Intellectuelle" est disponible car les fichiers VHDL'93 (ou VERILOG) sont disponibles pour quiconque peut les lire, les compiler et les modifier. Une vue schématique est aussi souvent nécessaire

pour comprendre une fonction d'un circuit d'un premier coup d'oeil. Le processeur existe alors plus sous la forme d'un logiciel descriptif que d'un circuit matériel. Ceci permettra à la famille de processeur d'évoluer plus facilement et mieux que les versions commerciales et ce polymorphisme garantira que tout le monde pourra trouver le meilleur coeur dans toutes les situations. Et comme le développement du logiciel sera commun à toutes les puces, librement disponible avec la GPL, le portage de tous les logiciels sur toutes les plateformes sera facilité au maximum.

L'intéropérabilité du logiciel quelque soit le membre de la famille est une forte contrainte et probablement une des règles de développement du projet les plus importantes: "AUCUNE RESSOURCE NE DOIT ETRE LIMITEE". Ceci mène à créer un CPU avec une largeur de donnée "indéterminée". Une puce F-CPU peut implémenter une caractéristique de largeur de donnée de toute taille au dessus de 32 bits. Le logiciel portable respectera quelques règles simples donc il pourra tourner aussi rapidement que le processeur le peut, indépendemment des considérations algorithmiques. En fait la vitesse d'un CPU est déterminé par des contraintes économiques et le concepteur construira un CPU aussi large que le permettent le budget et la technologie. De cette manière, il n'y a pas d'autre "roadmap" que les besoins des utilisateurs car c'est son propre fondeur. Le projet n'est pas limité par la technologie et est suffisamment flexible pour durer... aussi longtemps que nous le souhaitons.

# Chapitre 6

# Cheminement du projet

Il existe des étapes que le projet tente de suivre dans le futur. Il N'Y A PAS DE PLANNING car c'est un projet grossisant naturellement, pas un projet orienté vers le commercial; nous sommes plus concernés par la pertinence et l'efficacité que par la mise sur le marché dans les temps; et plusieurs "coopérateurs" peuvent changer les priorités du groupe F-CPU. Ce cheminement n'est pas définitif, il a déjà été changé et changera dans le futur. Il aide à comprendre les orientations du travail du groupe. Les étapes suivantes sont néanmoins très importantes et montrent que c'est un projet EVOLUTIF plutôt qu'une utopie sans fondement.

| Génération           | Prototype                                              | Pre-séries                                              | Classe Commerciale          |

|----------------------|--------------------------------------------------------|---------------------------------------------------------|-----------------------------|

| Nom de               | "POC": Preuve du                                       | "JOUET": dois-je en dire                                | F1, F2, F3 d'autres so-     |

| Code                 | Concept                                                | plus?                                                   | briquets seront trouvés (et |

| D.                   | A                                                      |                                                         | trademarkés)                |

| But                  | Avoir une "puce" qui                                   | Fournir les premier uti-                                | Définir une plateforme      |

|                      | peut être montrée ou                                   | lisateurs avec une plate-                               | matérielle à partir de      |

|                      | avec laquelle on peut                                  | forme avancée, encore li-                               | laquelle les autres puces   |

|                      | faire une démonstration                                | mitée pour tester le F-                                 | compatibles broches à       |

|                      | dans les salons com-                                   | CPU au réel. Permettre                                  | broches peuvent être        |

|                      | merciaux / conférences,                                | aux gens d'écrire des lo-                               | dérivées. La "carte         |

|                      | faire fonctionner le coeur                             | giciels réels et d'avoir de                             | mère" et les interfaces     |

|                      | FC0, le tester, explorer                               | l'expérience avec le jeu                                | I/O doivent fournir au-     |

|                      | la mémoire d'interface                                 | d'instruction et les ha-                                | tant d'espace libre que     |

|                      | et son impact sur la                                   | bitudes de programma-                                   | possible pour de fu-        |