## .

## 1. Overview on sequential circuits

- 2. Synchronous circuits

- 3. Danger of synthesizing asynchronous circuit

Outline

- 4. Inference of basic memory elements

- 5. Simple design examples

- 6. Timing analysis

- 7. Alternative one-segment coding style

- 8. Use of variable for sequential circuit

RTL Hardware Design Chapter 8 by P. Chu

# RTL Hardware Design by P. Chu

Chapter 8

Sequential Circuit Design:

Principle

.

### 1. Overview on sequential circuit

- · Combinational vs sequential circuit

- Sequential circuit: output is a function of current input and state (memory)

- · Basic memory elements

- D latch

- D FF (Flip-Flop)

- -RAM

- · Synchronous vs asynchronous circuit

RTL Hardware Design Chapter 8 3 by P. Chu

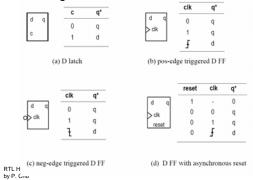

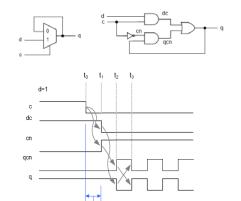

- D latch: level sensitive

- D FF: edge sensitive

RTL Hardware Design Chapter 8 5 by P. Chu

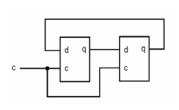

Problem wit D latch:

Can the two D latches swap data?

RTL Hardware Design Chapter 8 by P. Chu

1

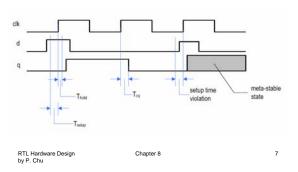

- Timing of a D FF:

- Clock-to-q delay

- Constraint: setup time and hold time

## 2. Synchronous circuit

- One of the most difficult design aspects of a sequential circuit:

How to satisfy the timing constraints

- The Big idea: Synchronous methodology

- Group all D FFs together with a single clock: Synchronous methodology

- Only need to deal with the timing constraint of one memory element

| RTL Hardware Design<br>by P. Chu | Chapter 8 | 9 |

|----------------------------------|-----------|---|

|----------------------------------|-----------|---|

RTL Hardware Design Chapter 8 11 by P. Chu

## Synch vs asynch circuits

- Globally synchronous circuit: all memory elements (D FFs) controlled (synchronized) by a common global clock signal

- Globally asynchronous but locally synchronous circuit (GALS).

- · Globally asynchronous circuit

- Use D FF but not a global clock

- Use no clock signal

RTL Hardware Design Chapter 8 8 by P. Chu

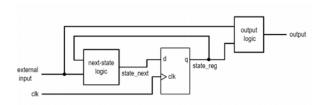

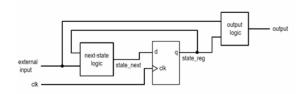

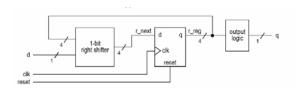

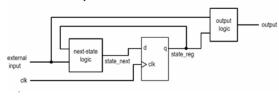

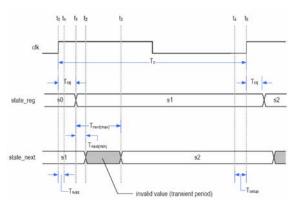

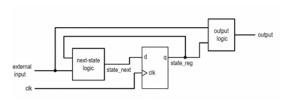

- · Basic block diagram

- State register (memory elements)

- Next-state logic (combinational circuit)

- Output logic (combinational circuit)

- Operation

- At the rising edge of the clock, state\_next sampled and stored into the register (and becomes the new value of state\_reg

- The next-state logic determines the new value (new state\_next) and the output logic generates the output

- At the rising edge of the clock, the new value of state\_next sampled and stored into the register

- Glitches has no effects as long as the state\_next is stabled at the sampling edge

RTL Hardware Design Chapter 8 10 by P. Chu

## Sync circuit and EDA

- Synthesis: reduce to combinational circuit synthesis

- Timing analysis: involve only a single closed feedback loop (others reduce to combinational circuit analysis)

- Simulation: support "cycle-based simulation"

- Testing: can facilitate scan-chain

RTL Hardware Design Chapter 8 12 by P. Chu

## Types of sync circuits

- · Not formally defined, Just for coding

- Three types:

- "Regular" sequential circuit

- "Random" sequential circuit (FSM)

- "Combined" sequential circuit (FSM with a Data path, FSMD)

# RTL Hardware Design Chapter 8 13 by P. Chu

# E.g., a D latch from scratch

RTL Hardware Design by P. Chu

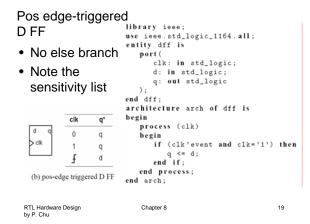

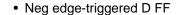

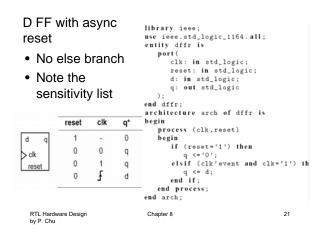

# 4. Inference of basic memory elements

- VHDL code should be clear so that the pre-designed cells can be inferred

- VHDL code

- D Latch

- Positive edge-triggered D FF

- Negative edge-triggered D FF

- D FF with asynchronous reset

```

RTL Hardware Design Chapter 8 17 by P. Chu

```

# 3. Danger of synthesizing asynchronous circuit

#### • D Latch/DFF

- Are combinational circuits with feedback loop

- Design is different from normal combinational circuits (it is delay-sensitive)

- Should not be synthesized from scratch

- Should use pre-designed cells from device library

RTL Hardware Design Chapter 8 14 by P. Chu

#### D Latch

RTL Har by P. Ch.

- No else branch

- D latch will be inferred

RTL Hardware Design by P. Chu

16

Chapter 8 18

#### Register

# 5. Simple design examples

- · Follow the block diagram

- Register

- Next-state logic (combinational circuit)

- Output logic (combinational circuit)

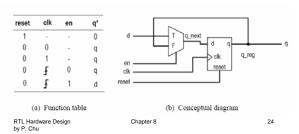

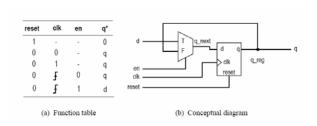

#### D FF with sync enable

- · Note that the en is controlled by clock

- · Note the sensitivity list

```

library ieee;

use ieee.std_logic_1164.all;

entity dff_en is

port (

clk: in std_logic;

reset: in std_logic;

en: in std_logic;

d: in std_logic;

q: out std_logic

);

end dff_en;

```

```

signal q_reg: std_logic;

signal q_next: std_logic;

begin

-- a D FF

process (clk,reset)

begin

if (reset='1') then

q_reg <= '0';

elsif (clk'event and clk='1') ther</pre>

q_reg <= q_next;

end if;</pre>

end process;

- next-state logic

q_next <= d when en ='1' else

q_reg;

-- output logic

q <= q_reg;

end two_seg_arch;

```

architecture two\_seg\_arch of dff\_en is

RTL Hardware Design by P. Chu

Chapter 8

RTL Hardware Design by P. Chu

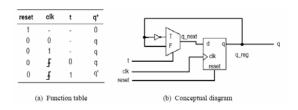

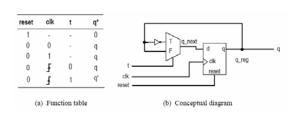

#### T FF

library ieee;

use ieee.std\_logic\_1164.all; entity tff is port ( clk: in std\_logic; reset: in std\_logic; t: in std\_logic; q: out std\_logic end tff; architecture two\_seg\_arch of tff is signal q\_reg: std\_logic; signal q\_next: std\_logic;

RTL Hardware Design by P. Chu

Chapter 8

RTL Hardware Design by P. Chu

Chapter 8

30

#### $architecture \ {\tt two\_seg\_arch} \ of \ {\tt tff} \ is$ signal q\_reg: std\_logic; signal q\_next: std\_logic; begin -- a D FF process (clk,reset) begin if (reset='1') then q\_reg <= '0'; elsif (clk'event and clk='1') then q\_reg <= q\_next; end if; end process; - next-state logic $q_next <= q_reg when t=000 else$ not(q\_reg); -- output logic q <= q\_reg; end two\_seg\_arch; RTL Hardware Design by P. Chu Chapter 8

29

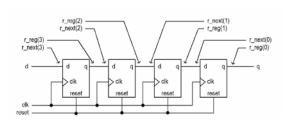

## Free-running shift register

RTL Hardware Design by P. Chu Chapter 8

RTL Hardware Design by P. Chu

Chapter 8

31

33

RTL Hardware Design by P. Chu

Chapter 8

32

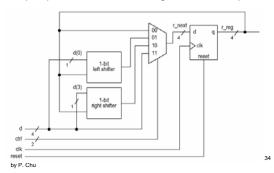

### Universal shift register

• 4 ops: parallel load, shift right, shift left, pause

```

library isse;

use isses.std_logic_li64.all;

entity shift_register is

port(

clk, reset: in std_logic;

ctrl: in std_logic_vector(1 downto 0);

d: in std_logic_vector(3 downto 0);

q: out std_logic_vector(3 downto 0));

end shift_register;

architecture two_seg_arch of shift_register is

signal r_reg: std_logic_vector(3 downto 0);

signal r_next: std_logic_vector(3 downto 0);

```

RTL Hardware Design Chapter 8 35 by P. Chu

```

-- register

process (clk,reset)

begin

if (reset='1') then

r_reg <= (others=>'0');

elsif (clk'event and clk='1') then

r_reg <= r_next;

end if;

end process;

- next-state logic

with ctrl select

r_next <=

r_reg

when "00", --no op

r_reg(2 downto 0) & d(0) when "01", --shift left;

d(3) & r_reg(3 downto 1) when "10", --shift right

d

when others:

-- output

q <= r_reg;

end two_seg_arch;

RTL Hardware Design by P. Chu

36

Chapter 8

```

#### Arbitrary sequence counter

```

input pattern output pattern

000

011

110

101

101

111

111

000

entity arbi_seq_counter4 is

clk, reset: in std_logic;

q: out std_logic_vector(2 downto 0)

end arbi_seq_counter4;

architecture two_seg_arch of arbi_seq_counter4 is

signal r_reg: std_logic_vector(2 downto 0);

signal r_next: std_logic_vector(2 downto 0);

RTL Hardware Design

by P. Chu

Chapter 8

```

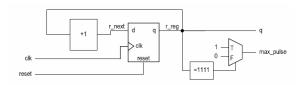

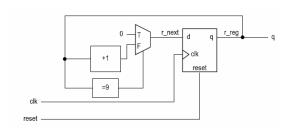

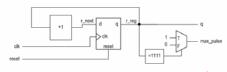

## Free-running binary counter

- · Count in binary sequence

- With a max\_pulse output: asserted when counter is in "11...11" state

- · Wrapped around automatically

- Poor practice:

```

r_next \le (r_reg + 1) \mod 16;

RTL Hardware Design Chapter 8 41

```

Chapter 8

## Binary counter with bells & whistles

RTL Hardware Design by P. Chu

```

operation

svn_clr load en

00 - - - 00

synchronous clear

d

parallel load

0

٥

1

q+1

count

0

0

0

q

pause

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity binary_counter4_feature is

port (

clk, reset: in std_logic;

syn_clr, en, load: std_logic;

d: std_logic_vector(3 downto 0);

q: out std_logic_vector(3 downto 0)

end \  \  \, \texttt{binary\_counter4\_feature;}

RTL Hardware Design by P. Chu

Chapter 8

```

```

architecture two_seg_arch of binary_counter4_feature is

signal r_reg: unsigned(3 downto 0);

signal r_next: unsigned(3 downto 0);

begin

-- register

process (clk.reset)

begin

if (reset='1') then

r_reg <= (others=>'0');

elsif (clk'event and clk='1') then

r_reg <= r_next;

end if;

end process;

-- next-state logic

r_next <= (others=>'0') when syn_clr='1' else

unsigned(d) when load='1' else

r_reg + 1 when en ='1' else

r_reg + 1

r_reg;

- output logic

q <= std_logic_vector(r_reg);

end two_seg_arch;

RTL Hardware Design by P. Chu

Chapter 8

```

# Decade (mod-10) counter

```

architecture two_sog_arch of modi0_counter is

constant TEN: integer := 10;

signal r_reg: unsigned(3 downto 0);

signal r_next: unsigned(3 downto 0);

begin

-- register

process (clk,reset)

begin

if (reset='1') then

r_reg <= (others=>'0');

elsif (clk'event and clk='1') then

r_reg <= r_next;

end if;

end process;

-- next-state logic

r_next <= (others=>'0') when r_reg=(TEN-1) else

r_reg +1;

-- output logic

q <= std_logic_vector(r_reg);

end two_seg_arch;

RTL Hardware Design

Dyp. Chu

```

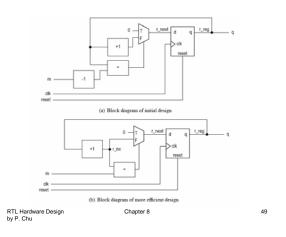

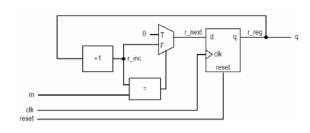

## Programmable mod-m counter

```

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity prog_counter is

port(

clk, reset: in std_logic;

m: in std_logic_vector(3 downto 0);

q: out std_logic_vector(3 downto 0)

);

end prog_counter;

architecture two_seg_clear_arch of prog_counter is

```

RTL Hardware Design Chapter 8 45 by P. Chu

RTL Hardware Design Chapter 8 4 by P. Chu

```

signal r_reg: unsigned(3 downto 0);

signal r_next: unsigned(3 downto 0);

;begin

-- register

process (clk,reset)

begin

if (reset='1') then

r_reg (= (others=>'0');

elsif (clk'event and clk='1') then

r_reg <= r_next;

end if;

end process;

-- next-state logic

r_next <= (others=>'0') when r_reg=(unsigned(m)-1) else

r_reg + 1;

-- output logic

q <= std_logic_vector(r_reg);

send two_seg_clear_arch;</pre>

```

Chapter 8

RTL Hardware Design by P. Chu

47

```

architecture two_seg_effi_arch of prog_counter is

signal r_reg: unsigned(3 downto 0);

signal r_next, r_inc: unsigned(3 downto 0);

begin

-- register

process (clk,reset)

begin

if (reset='1') then

r_reg <= (others=>'0');

elsif (clk'event and clk='1') then

r_reg <= r_next;

end if;

end process;

-- next-state logic

r_inc <= r_reg + 1;

r_next <= (others=>'0') when r_inc=unsigned(m) else

r_inc;

-- output logic

q <= std_logic_vector(r_reg);</pre>

end two_seg_effi_arch;

RTL Hardware Design

by P. Chu

Chapter 8

48

```

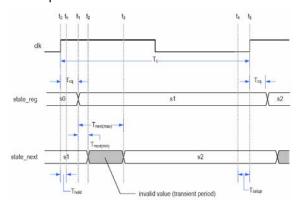

#### 6. Timing analysis

- · Combinational circuit:

- characterized by propagation delay

- · Sequential circuit:

- Has to satisfy setup/hold time constraint

- Characterized by maximal clock rate (e.g., 200 MHz counter, 2.4 GHz Pentium II)

- Setup time and clock-to-q delay of register and the propagation delay of next-state logic are embedded in clock rate

RTL Hardware Design Chapter 8

- state\_next must satisfy the constraint

- · Must consider effect of

- state\_reg: can be controlled

- synchronized external input (from a subsystem of same clock)

- unsynchronized external input

- Approach

- First 2: adjust clock rate to prevent violation

$t_3 = t_0 + T_{cq} + T_{next(max)}$

Last: use "synchronization circuit" to resolve violation

#### · Setup time violation and maximal clock rate

$$t_4 = t_5 - T_{setup} = t_0 + T_c - T_{setup}$$

$$t_3 < t_4$$

$$t_0 + T_{cq} + T_{next(max)} < t_0 + T_c - T_{setup}$$

$$T_{cq} + T_{next(max)} + T_{setup} < T_c$$

RTL Hardware Design Chapter 8 53 by P. Chu

$T_{c(min)} = T_{cq} + T_{next(max)} + T_{setup}$

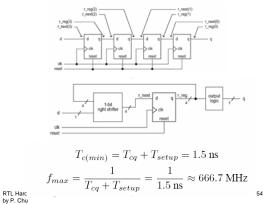

• E.g., shift register; let Tcq=1.0ns Tsetup=0.5ns

#### • E.g., Binary counter; let Tcq=1.0ns Tsetup=0.5ns

| width | VHDL operator |     |      |      |         |        |        |      |       |     |

|-------|---------------|-----|------|------|---------|--------|--------|------|-------|-----|

|       | nand          | xor | >a   | >d   | =       | $+1_a$ | $+1_d$ | +a   | $+_d$ | mux |

|       |               |     |      | are  | a (gate | count  | )      |      |       |     |

| 8     | 8             | 22  | 25   | 68   | 26      | 27     | 33     | 51   | 118   | 21  |

| 16    | 16            | 44  | 52   | 102  | 51      | 55     | 73     | 101  | 265   | 42  |

| 3.2   | 32            | 85  | 105  | 211  | 102     | 113    | 153    | 203  | 437   | 85  |

| 64    | 64            | 171 | 212  | 398  | 204     | 227    | 313    | 405  | 755   | 171 |

|       |               |     |      |      | delay   | (ns)   |        |      |       |     |

| 8     | 0.1           | 0.4 | 4.0  | 1.9  | 1.0     | 2.4    | 1.5    | 4.2  | 3.2   | 0.3 |

| 16    | 0.1           | 0.4 | 8.6  | 3.7  | 1.7     | 5.5    | 3.3    | 8.2  | 5.5   | 0.3 |

| 32    | 0.1           | 0.4 | 17.6 | 6.7  | 1.8     | 11.6   | 7.5    | 16.2 | 11.1  | 0.3 |

| 64    | 0.1           | 0.4 | 35.7 | 14.3 | 2.2     | 24.0   | 15.7   | 32.2 | 22.9  | 0.3 |

RTL Hardware Design Chapter 8 by P. Chu

$$\begin{split} f_{max} &= \frac{1}{T_{cq} + T_{8\_bit\_inc(area)} + T_{setup}} = \frac{1}{1 \text{ ns} + 2.4 \text{ ns} + 0.5 \text{ ns}} \approx 256.4 \text{ MHz} \\ f_{max} &= \frac{1}{T_{cq} + T_{16\_bit\_inc(area)} + T_{setup}} = \frac{1}{1 \text{ ns} + 5.5 \text{ ns} + 0.5 \text{ ns}} \approx 142.9 \text{ MHz} \\ f_{max} &= \frac{1}{T_{cr} + T_{32\_bit\_inc(area)} + T_{setup}} = \frac{1}{1 \text{ ns} + 11.6 \text{ ns} + 0.5 \text{ ns}} \approx 76.3 \text{ MHz} \end{split}$$

$$\begin{split} f_{max} &= \frac{1}{T_{cq} + T_{8.bit\_inc(delay)} + T_{setup}} = \frac{1}{1 \text{ ns} + 1.5 \text{ ns} + 0.5 \text{ ns}} \approx 333.3 \text{ MHz} \\ f_{max} &= \frac{1}{T_{cq} + T_{16\_bit\_inc(delay)} + T_{setup}} = \frac{1}{1 \text{ ns} + 3.3 \text{ ns} + 0.5 \text{ ns}} \approx 208.3 \text{ MHz} \\ \text{and} \\ f_{max} &= \frac{1}{T_{cq} + T_{32\_bit\_inc(delay)} + T_{setup}} = \frac{1}{1 \text{ ns} + 7.5 \text{ ns} + 0.5 \text{ ns}} \approx 111.1 \text{ MHz} \\ \text{RTL Hardware Design} & \text{Chapter 8} & 56 \end{split}$$

#### · Hold time violation

$$t_2 = t_0 + T_{cq} + T_{next(min)}$$

$$t_h = t_0 + T_{hold}$$

$$t_h < t_2$$

$$T_{hold} < T_{cq} + T_{next(min)}$$

$$T_{hold} < T_{cq}$$

RTL Hardware Design Chapter 8 5 by P. Chu

# Output delay

$$T_{co} = T_{cq} + T_{output}$$

RTL Hardware Design Chapter 8 59 by P. Chu

# 7. Alternative one-segment coding style

- Combine register and next-state logic/output logic in the same process

- May appear compact for certain simple circuit

- But it can be error-prone

RTL Hardware Design Chapter 8 by P. Chu

## D FF with sync enable

```

library ieee;

use ieee.std_logic_1164.all;

entity dff_en is

port(

clk: in std_logic;

reset: in std_logic;

en: in std_logic;

d: in std_logic;

q: out std_logic

);

end dff_en;

```

RTL Hardware Design Chapter 8 61 by P. Chu

```

RTL Hardware Design Chapter 8 6 by P. Chu

```

```

architecture two_seg_arch of dff_en is

signal q_reg: std_logic;

signal q_next: std_logic;

begin

-- a D FF

process (clk,reset)

begin

if (reset='1') then

q_reg <= '0';

elsif (clk'event and clk='1') ther

q_reg <= q_next;

end if;</pre>

end process;

- next-state logic

q_next <= d when en = '1' else

q_reg;

-- output logic

q <= q_reg;

end two_seg_arch;</pre>

RTL Hardware Design by P. Chu

Chapter 8

```

```

Architecture one_seg_arch of dff_en is

begin

process (clk,reset)

begin

if (reset='1') then

q <='0';

elsif (clk'event and clk='1') then

if (en='1') then

q <= d;

end if;

end process;

end one_seg_arch;

```

Interpretation: any left-hand-side signal within the clk'event and clik='1' branch infers a D FF

RTL Hardware Design Chapter 8 64 by P. Chu

#### T FF

RTL Hardware Design Chapter 8 65 by P. Chu

RTL Hardware Design Chapter 8 66 by P. Chu

```

architecture \ {\tt two\_seg\_arch} \ of \ {\tt tff} \ is

signal q_reg: std_logic;

signal q_next: std_logic;

begin

__ a D FF

process (clk.reset)

begin

if (reset='1') then

q_reg <= '0';

elsif (clk'event and clk='1') then

q_reg <= q_next;

end if;

end process;

- next-state logic

- output logic

q <= q_reg;

end two_seg_arch;

RTL Hardware Design by P. Chu

```

RTL Hardware Design Chapter 8 by P. Chu

#### Binary counter with bells & whistles

```

operation

svn_clr load en

00 \cdots 00

synchronous clear

parallel load

d

0

٥

- 1

q+1

count

0

0

0

q

pause

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity \  \, \texttt{binary\_counter4\_feature} \  \, is

port (

clk, reset: in std_logic;

syn_clr, en, load: std_logic;

d: std_logic_vector(3 downto 0);

q: out std_logic_vector(3 downto 0)

end binary_counter4_feature;

RTL Hardware Design by P. Chu

Chapter 8

```

```

architecture two_seg_arch of binary_counter4_feature is

signal r_reg: unsigned(3 downto 0);

signal r_next: unsigned(3 downto 0);

-- register

process (clk,reset)

begin

if (reset='1') then

r_reg <= (others=>'0');

elsif (clk'event and clk='1') then

r_reg <= r_next;

end process;

- next-state logic

r_next <= (others=>'0') when syn_clr='1' else

unsigned(d) when load='1' else

r_reg + 1 when en ='1' else

r_reg;

-- output logic

q <= std_logic_vector(r_reg);

end two_seg_arch;</pre>

RTL Hardware Design

by P. Chu

Chapter 8

```

```

architecture one_seg_arch of binary_counter4_feature is

signal r_reg: unsigned(3 downto 0);

signal r_next: unsigned(3 downto 0);

begin

- register & next-state logic

process (clk,reset)

begin

if (reset='1') then

r_reg <= (others=>'0');

elsif (clk'event and clk='1') then

if syn_clr='1' then

r_reg <= (others=>'0');

elsif load='1' then

r_reg <= unsigned(d);

elsif en ='1' then

r_reg <= r_reg + 1;

end if;

end if;

end process;

-- output logic

q <= std_logic_vector(r_reg);</pre>

end one_seg_arch;

```

#### Free-running binary counter

- · Count in binary sequence

- With a max\_pulse output: asserted when counter is in "11...11" state

```

architecture not_work_one_seg_glitch_arch

of binary_counter4_pulse is

signal r_reg: unsigned(3 downto 0);

begin

process (clk, reset)

begin

if (reset='1') then

r_reg <= (others => '0');

elsif (clk'event and clk='1') then

r_reg <= r_reg + 1;

if r_reg="1111" then

max_pulse <= '1';

else

max_pulse <= '0';

end if;

end if;

end process;

q <= std_logic_vector(r_reg);</pre>

75

end not_work_one_seg_glitch_arch;

```

```

architecture \  \, \mathtt{work\_one\_seg\_glitch\_arch}

of binary_counter4_pulse is

signal r_reg: unsigned(3 downto 0);

begin

process (clk, reset)

begin

if (reset='1') then

r_reg <= (others=>'0');

elsif (clk'event and clk='1') then

r_reg <= r_reg + 1;

end if;

end process;

q <= std_logic_vector(r_reg);</pre>

max_pulse <= '1' when r_reg="1111" else

,0,:

end work_one_seg_glitch_arch;

RTL Hardware Design

by P. Chu

Chapter 8

```

# Programmable mod-m counter

```

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity prog_counter is

port(

clk, reset: in std_logic;

m: in std_logic_vector(3 downto 0);

q: out std_logic_vector(3 downto 0)

);

end prog_counter;

architecture two_seg_clear_arch of prog_counter is

```

```

architecture two_seg_effi_arch of prog_counter is

signal r_reg: unsigned(3 downto 0);

signal r_next, r_inc: unsigned(3 downto 0);

begin

-- register

process (clk,reset)

begin

if (reset='1') then

r_reg <= (others=>'0');

elsif (clk'event and clk='1') then

r_reg <= r_next;

end if;

end process;

-- next-state logic

r_inc <= r_reg + 1;

r_next <= (others=>'0') when r_inc=unsigned(m) else

r_inc;

-- output logic

q <= std_logic_vector(r_reg);</pre>

end two_seg_effi_arch;

RTL Hardware Design

by P. Chu

78

Chapter 8

```

RTL Hardware Design Chapter 8 79 by P. Chu

```

architecture work_one_arch of prog_counter is

signal r_reg: unsigned(3 downto 0);

signal r_inc: unsigned(3 downto 0);

begin

process (clk,reset)

begin

if reset='1' then

r_reg <= (others=>'0');

elsif (clk'event and clk='1') then

if (r_inc=unsigned(m)) then

r_reg <= (others=>'0');

else

r_reg <= r_inc;

end if;

end if;

end process;

r_inc <= r_reg + 1;

q <= std_logic_vector(r_reg);

end work_one_arch;

RTL Hardware Design

Design Chapter 8 81

```

```

architecture not_work_one_arch of prog_counter is

signal r_reg: unsigned(3 downto 0);

begin

process (clk, reset)

begin

if reset='1' then

r_reg <= (others=>'0');

elsif (clk'event and clk='1') then

r_reg <= r_reg+1;

if (r_reg=unsigned(m)) then

r_reg <= (others => '0');

end if;

end if;

end process;

q <= std_logic_vector(r_reg);</pre>

end not_work_one_arch;

RTL Hardware Design by P. Chu

Chapter 8

```

- Two-segment code

- Separate memory segment from the rest

- Can be little cumbersome

- Has a clear mapping to hardware component

- One-segment code

- Mix memory segment and next-state logic / output logic

- Can sometimes be more compact

- No clear hardware mapping

- Error prone

- Two-segment code is preferred

RTL Hardware Design Chapter 8 82 by P. Chu