# Sequential Circuit Design: Practice

## Outline

- 1. Poor design practice and remedy

- 2. More counters

- 3. Register as fast temporary storage

- 4. Pipelined circuit

RTL Hardware Design Chapter 9 1 by P. Chu

RTL Hardware Design by P. Chu

Chapter 9

# 1. Poor design practice and remedy

- Synchronous design is the most important methodology

- Poor practice in the past (to save chips)

- Misuse of asynchronous reset

- Misuse of gated clock

- Misuse of derived clock

RTL Hardware Design Chapter 9 by P. Chu

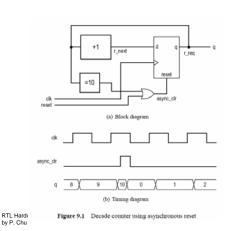

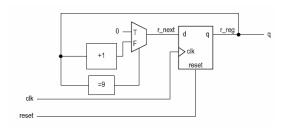

# Misuse of asynchronous reset

- Poor design: use reset to clear register in normal operation.

- e.g., a poorly mod-10 counter

- Clear register immediately after the counter reaches 1010

```

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity mod10_counter is

port(

clk, reset: in std_logic;

q: out std_logic_vector(3 downto 0)

);

end mod10_counter;

```

RTL Hardware Design Chapter 9 by P. Chu

- Problem

- Glitches in transition 1001 (9) => 0000 (0)

- Glitches in aync\_clr can reset the counter

- How about timing analysis? (maximal clock rate)

- Asynchronous reset should only be used for power-on initialization

RTL Hardware Design Chapter 9 by P. Chu

RTL Hardware Design Chapter 9 9 by P. Chu

• Remedy: load "0000" synchronously

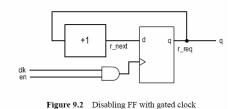

# Misuse of gated clock

- Poor design: use a and gate to disable the clock to stop the register to get new value

- E.g., a counter with an enable signal

RTL Hardware Design Chapter 9 12 by P. Chu

- Problem

- Gated clock width can be narrow

- Gated clock may pass glitches of en

- Difficult to design the clock distribution network

RTL Hardware Design Chapter 9 13 by P. Chu

## • Remedy: use a synchronous enable

```

architecture two_seg_arch of binary_counter is

signal r_reg: unsigned(3 downto 0);

signal r_next: unsigned(3 downto 0);

begin

— register

process (clk,reset)

begin

if (reset='1') then

r_reg <= (others=>'0');

elsif (clk'event and clk='1') then

r_reg <= r_next;

end if;

end process;

— next state logic

r_next <= r_reg + 1 when en='1' else

r_reg;

— output logic

q <= std_logic_vector(r_reg);

end two_seg_arch;

RTLHardware Design

byP.Chu</pre>

```

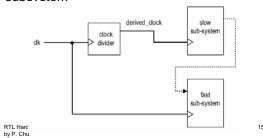

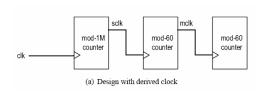

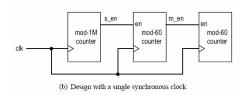

## Misuse of derived clock

- Subsystems may run at different clock rate

- Poor design: use a derived slow clock for slow subsystem

#### Problem

- Multiple clock distribution network

- How about timing analysis? (maximal clock rate)

RTL Hardware Design Chapter 9 16 by P. Chu

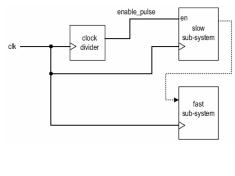

• Better use a synchronous one-clock enable pulse

RTL Hardware Design Chapter 9 17 by P. Chu

- E.g., second and minutes counter

- Input: 1 MHz clock

- Poor design:

RTL Hardware Design Chapter 9 18 by P. Chu

#### - Better design

RTL Hardware Design Chapter 9 by P. Chu

```

-- register

process (clk, reset)

begin

if (reset='1') then

r_reg <= (others=>'0');

elsif (clk'event and clk='1') then

r_reg <= r_next;

end if;

end process;

-- next state logic

r_next <= (others=>'0') when r_reg=99999 else

r_reg + 1;

-- output logic

sclk <= '0' when r_reg < 500000 else

'1';

```

RTL Hardware Design Chapter 9 by P. Chu

```

-- minute divider

process (mclk, reset)

begin

if (reset='1') then

m_reg <= (others=>'0');

elsif (mclk'event and mclk='1') then

m_reg <= m_next;

end if;

end process;

-- next state logic

m_next <= (others=>'0') when m_reg=59 else

m_reg + 1;

-- output logic

min <= std_logic_vector(m_reg);

end multi_clock_arch;

```

RTL Hardware Design Chapter 9 23 by P. Chu

## • VHDL code of poor design

```

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity timer is

port (

clk, reset: in std_logic;

sec,min: out std_logic_vector(5 downto 0)

);

end timer;

architecture multi_clock_arch of timer is

signal r_reg: unsigned(3 downto 0);

signal r_next: unsigned(3 downto 0);

signal s_reg, m_reg: unsigned(5 downto 0);

signal s_next, m_next: unsigned(5 downto 0);

signal sclk, mclk: std_logic;

begin

RTL Hardware Design

by P. Chu

```

```

-- second divider

process (sclk, reset)

begin

if (reset='1') then

s_reg <= (others=>'0');

elsif (sclk'event and sclk='1') then

s_reg <= s_next;

end if:

end process;

-- next state logic

s_next <= (others=>,0,0) when s_neg=59 else

s_reg + 1;

-- output logic

mclk <= '0' when s_reg < 30 else

11;

sec <= std_logic_vector(s_reg);</pre>

```

RTL Hardware Design Chapter 9 by P. Chu

#### Remedy: use a synchronous 1-clock pulse

```

-- next state logic/output logic for mod-1000000 counter

r_next <= (others=>'0') when r_reg=999999 else

r_reg + 1;

s_en <= '1' when r_reg = 500000 else

'0';

-- ext state logic/output logic for second divider

s_next <= (others=>'0') when (s_reg=59 and s_en='1') else

s_reg;

m_en <= '1' when s_reg=30 and s_en='1' else

'0';

-- next state logic for minute divider

m_next <= (others=>'0') when (m_reg=59 and m_en='1') else

m_reg + 1 when m_en='1' else

s=c <= std_logic_vector(s_reg);

sec <= std_logic_vector(m_reg);

end single_clock_arch;

RTL Hardware Design Chapter 9 25

by P. Chu

```

## A word about power

- · Power is a major design criteria now

- In CMOS technology

- Dynamic power is proportional to the switching frequency of transistors

- High clock rate implies high switching freq

- Clock manipulation

- Can reduce switching frequency

- But should not be done at RT level

RTL Hardware Design Chapter 9 by P. Chu

## Development flow:

- Design/synthesize/verify a regular synchronous subsystems

- 2(a). Derived clock: use special circuit (PLL etc.) to obtain derived clocks

- 2(b). Gated clock: use "power optimization" software tool to convert some register into gated clock

RTL Hardware Design Chapter 9 27 by P. Chu

## 2. More counters

- · Counter circulates a set of specific patterns

- Counter:

- Binary

- Gray counter

- Ring counter

- Linear Feedback Shift Register (LFSR)

- BCD counter

## • Binary counter:

- State follows binary counting sequence

- Use an incrementor for the next-state logic

RTL Hardware Design Chapter 9 29 by P. Chu

## · Gray counter:

- State changes onebit at a time

- Use a Gray incrementor

| gray code | incremented gray code |  |

|-----------|-----------------------|--|

| 0000      | 0001                  |  |

| 0001      | 0011                  |  |

| 0011      | 0010                  |  |

| 0010      | 0110                  |  |

| 0110      | 0111                  |  |

| 0111      | 0101                  |  |

| 0101      | 0100                  |  |

| 0100      | 1100                  |  |

| 1100      | 1101                  |  |

| 1101      | 1111                  |  |

| 1111      | 1110                  |  |

| 1110      | 1010                  |  |

| 1010      | 1011                  |  |

| 1011      | 1001                  |  |

| 1001      | 1000                  |  |

| 1000      | 0000                  |  |

RTL Hardware Design Chapter 9 by P. Chu

```

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity gray_counter4 is

port (

clk, reset: in std_logic;

q: out std_logic_vector(3 downto 0)

end gray_counter4;

architecture arch of gray_counter4 is

constant WIDTH: natural := 4;

signal g_reg: unsigned(WIDTH-1 downto 0);

signal g_next, b, b1: unsigned(WIDTH-1 downto 0);

```

31

35

```

begin

- register

process (clk,reset)

begin

if (reset='1') then

g_reg <= (others => '0');

elsif (clk'event and clk='1') then

g_reg <= g_next;

end if;</pre>

end process;

-- next-state logic

-- gray to binary

b <= g_reg xor ('0' & b(WIDTH-1 downto 1));

b1 <= b+1; -- increment

-- binary to gray

g_next <= b1 xor ('0' & b1(WIDTH-1 downto 1));

- output logic

q <= std_logic_vector(g_reg);

end arch;

RTL Hardware Design by P. Chu

```

Chapter 9

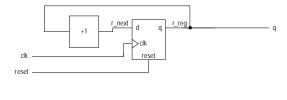

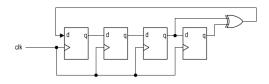

# Ring counter

Chapter 9

• Circulate a single 1

RTL Hardware Design by P. Chu

- E.g., 4-bit ring counter: 1000, 0100, 0010, 0001

- *n* patterns for *n*-bit register

- Output appears as an n-phase signal

- · Non self-correcting design

- -Insert "0001" at initialization and circulate the pattern in normal operation

- -Fastest counter

33 RTL Hardware Design by P. Chu Chapter 9

```

library ieee;

use ieee.std_logic_1164.all;

entity ring_counter is

port (

port(

clk, reset: in std_logic;

q: out std_logic_vector(3 downto 0));

end ring_counter;

architecture reset_arch of ring_counter is

constant WIDTH: natural := 4;

signal r_reg: std_logic_vector(WIDTH-1 d

signal r_next: std_logic_vector(WIDTH-1

begin

— register

RTL Hardware

by P. Chu

```

· Self-correcting design: shifting in a '1' only when 3 MSBs are 000

```

-- register

process (clk,reset)

begin

if (reset='1') then

r_reg <= (others=>'0');

elsif (clk'event and clk='1') then

r_reg <= r_next;

end if;

end process;

-- next-state logic

s_in <= '1' when r_reg(WIDTH-1 downto 1)="000" else

,0,:

r_next <= s_in & r_reg(WIDTH-1 downto 1);

RTL Hardware Design

by P. Chu

Chapter 9

```

# LFSR (Linear Feedback Shift Reg)

- A sifter reg with a special feedback circuit to generate the serial input

- The feedback circuit performs xor operation over specific bits

- Can circulate through 2<sup>n</sup>-1 states for an nbit register

RTL Hardware Design Chapter 9 by P. Chu

## Property of LFSR

- N-bit LFSR can cycle through 2n-1 states

- The feedback circuit always exists

- The sequence is pseudorandom

|                     | Register size | Feedback expression                          |  |

|---------------------|---------------|----------------------------------------------|--|

|                     | 2             | $q_1 \oplus q_0$                             |  |

|                     | 3             | $q_1 \oplus q_0$                             |  |

|                     | 4             | $q_1 \oplus q_0$                             |  |

|                     | 5             | $q_2 \oplus q_0$                             |  |

|                     | 6             | $q_1 \oplus q_0$                             |  |

|                     | 7             | $q_3 \oplus q_0$                             |  |

|                     | 8             | $q_4 \oplus q_3 \oplus q_2 \oplus q_0$       |  |

|                     | 16            | $q_5 \oplus q_4 \oplus q_3 \oplus q_0$       |  |

|                     | 32            | $q_{22} \oplus q_2 \oplus q_1 \oplus q_0$    |  |

|                     | 64            | $q_4 \oplus q_3 \oplus q_1 \oplus q_0$       |  |

| RTL Hardware Design | 128           | $q_{29} \oplus q_{17} \oplus q_2 \oplus q_0$ |  |

|                     |               |                                              |  |

use ieee.std\_logic\_1164.all;

entity lfsr4 is

port(

clk, reset: in std\_logic;

q: out std\_logic\_vector(3 downto 0));

end lfsr4;

architecture no\_zero\_arch of lfsr4 is

signal r\_reg, r\_next: std\_logic\_vector(3 downto 0);

signal fb: std\_logic;

constant SEED: std\_logic\_vector(3 downto 0):="0001";

RTL Hardware Design Chapter 9 41 by P. Chu

## • E.g, 4-bit LFSR

"1000", "0100", "0010", "1001", "1100", "1100", "1011", "1011", "1010", "1101", "1110", "1111", "01011", "0001", "0001".

RTL Hardware Design by P. Chu

Chapter 9

#### Application of LFSR

- Pseudorandom: used in testing, data encryption/decryption

- A counter with simple next-state logic

e.g., 128-bit LFSR using 3 xor gates to circulate

2<sup>128</sup>-1 patterns (takes 10<sup>12</sup> years for a 100 GHz system)

RTL Hardware Design Chapter 9 4

by P. Chu

```

begin

-- register

process (clk,reset)

begin

if (reset='1') then

r_reg <= SEED;

elsif (clk'event and clk='1') then

end process;

-- next-state logic

fb <= r_reg(1) xor r_reg(0);

r_next <= fb & r_reg(3 downto 1);

-- output logic

q <= r_reg;

end no_zero_arch;</pre>

```

RTL Hardware Design Chapter 9 by P. Chu

- Read remaining of Section 9.2.3 (design to including 00..00 state)

- Read Section 9.2.4 (BCD counter, design similar to the second/minute counter in Section 9.1.3

RTL Hardware Design Chapter 9 4 by P. Chu

RTL Hardware Design Chapter 9 45 by P. Chu

```

begin

-- register & buffer

process (clk,reset)

begin

if (reset='1') then

r_reg <= (others=>'0');

buf_reg <= '0';

elsif (clk'event and clk='1') then

r_reg <= r_next;

buf_reg <= buf_next;

end if;

end process;

-- next-state logic

r_next <= r_reg + 1;

-- output logic

buf_next <=

'1' when (r_reg<unsigned(w)) or (w="0000") else

'0';

pwm_pulse <= buf_reg;

end two_seg_arch;</pre>

```

RTL Hardware Design Chapter 9 by P. Chu

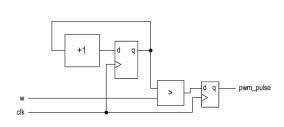

# PWM (pulse width modulation)

- Duty cycle: percentage of time that the signal is asserted

- PWM: use a signal, w, to specify the duty cycle

- Duty cycle is w/16 if w is not "0000"

- Duty cycle is 16/16 if w is "0000"

- Implemented by a binary counter with a special output circuit

RTL Hardware Design Chapter 9 by P. Chu

```

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity pwm is

port(

clk, reset: in std_logic;

w: in std_logic_vector(3 downto 0);

pwm_pulse: out std_logic

end pwm;

architecture two_seg_arch of pwm is

signal r_reg: unsigned(3 downto 0);

signal r_next: unsigned(3 downto 0);

signal buf_reg: std_logic;

signal buf_next: std_logic;

```

RTL Hardware Design Chapter 9 by P. Chu

## 3. Register as fast temporary storage

- RAM

- RAM cell designed at transistor level

- Cell use minimal area

- Behave like a latch

- For mass storage

- Need a special interface logic

- Register

- D FF requires much larger area

- Synchronous

- For small, fast storage

- E.g., register file, fast FIFO, Fast CAM (content addressable memory)

RTL Hardware Design Chapter 9 by P. Chu

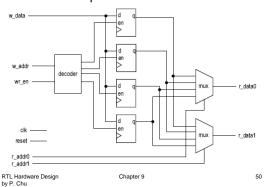

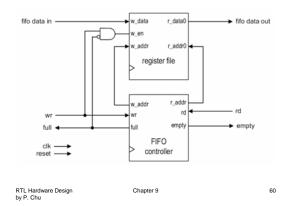

# Register file

- · Registers arranged as an 1-d array

- · Each register is identified with an address

- Normally has 1 write port (with write enable signal)

- · Can has multiple read ports

RTL Hardware Design Chapter 9 by P. Chu

- · Register array:

- 4 registers

- Each register has an enable signal

- Write decoding circuit:

- 0000 if wr\_en is 0

- 1 bit asserted according to w\_addr if wr\_en is 1

- · Read circuit:

- A mux for each read por

RTL Hardware Design Chapter 9 5 by P. Chu

```

--- register

process(clk, reset)

begin

if (reset='1') then

array_reg(3) <= (others=>'0');

array_reg(2) <= (others=>'0');

array_reg(1) <= (others=>'0');

array_reg(0) <= (others=>'0');

elsif (clk'event and clk='1') then

array_reg(3) <= array_next(3);

array_reg(2) <= array_next(2);

array_reg(1) <= array_next(1);

array_reg(0) <= array_next(0);

end if;

end process;

--- enable logic for register

```

RTL Hardware Design Chapter 9 53 by P. Chu

E.g., 4-word register file w/ 1 write port and two read ports

#### · 2-d data type needed

```

— enable logic for register

process(array_reg, en, w_data)

begin

array_next(3) <= array_reg(3);

array_next(2) <= array_reg(2);

array_next(1) <= array_reg(1);

array_next(0) <= array_reg(0);

if en(3)='1' then

array_next(3) <= w_data;

end if;

if en(2)='1' then

array_next(2) <= w_data;

end if;

if en(1)='1' then

array_next(1) <= w_data;

end if;

if en(0)='1' then

array_next(0) <= w_data;

end if;

end process;

RTL Hardware Design

by P. Chu

Chapter 9

```

```

process(wr_en,w_addr)

begin

if (wr_en='0') then

en <= (others=>'0');

else

case w_addr is

when "00" => en <= "0001";

when "01" => en <= "0010";

when "10" => en <= "0100";

when "10" => en <= "1000";

end case;

end if;

end process;

— read multiplexing

with r_addr0 select

r_data0 <= array_reg(1) when "01",

array_reg(2) when "10",

array_reg(3) when others;

with r_addr1 select

r_data1 <= array_reg(0) when "00",

array_reg(1) when "01",

array_reg(2) when "10",

array_reg(2) when "10",

array_reg(2) when "10",

array_reg(3) when others; 55

byP.Chu

end no_loop_arch;

```

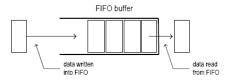

## FIFO Buffer

• "Elastic" storage between two subsystems

Figure 9.11 Conceptual diagram of a FIFO buffer.

RTL Hardware Design Chapter 9 56 by P. Chu

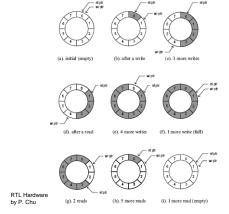

- Circular queue implementation

- Use two pointers and a "generic storage"

- Write pointer: point to the empty slot before the head of the queue

- Read pointer: point to the tail of the queue

RTL Hardware Design Chapter 9 55 by P. Chu

- FIFO controller

- Read and write pointers: 2 counters

- Status circuit:

- Difficult

- Design 1: Augmented binary counter

- Design 2: with status FFs

- LSFR as counter

RTL Hardware Design Chapter 9 59 by P. Chu

- · Augmented binary counter:

- increase the counter by 1 bits

- Use LSBs for as register address

- Use MSB to distinguish full or empty

| Write pointer | Read pointer | Operation      | Status |

|---------------|--------------|----------------|--------|

| 0 000         | 0 000        | initialization | empty  |

| 0 111         | 0 000        | after 7 writes |        |

| 1 000         | 0 000        | after 1 write  | full   |

| 1 000         | 0 100        | after 4 reads  |        |

| 1 100         | 0 100        | after 4 writes | full   |

| 1 100         | 1 011        | after 7 reads  |        |

| 1 100         | 1 100        | after 1 read   | empty  |

| 0 011         | 1 100        | after 7 writes |        |

| 0 100         | 1 100        | after 1 write  | full   |

| 0 100         | 0 100        | after 8 reads  | empty  |

RTL Hardware Design Chapter 9 by P. Chu

```

-- register

process(clk, reset)

begin

if (reset='1') then

w_ptr_reg <= (others=>'0');

r_ptr_reg <= (others=>'0');

elsif (clk'event and clk='1') then

w_ptr_reg <= w_ptr_next;

r_ptr_reg <= r_ptr_next;

end if;

end process;

```

RTL Hardware Design Chapter 9 by P. Chu

#### • 2 extra status FFs

- Full\_erg/empty\_reg memorize the current staus

- Initialized as 0 and 1

- Modified according to wr and rd signals:

- 00: no change

- 11: advance read pointer/write pointer; full/empty no change

- 10: advance write pointer; de-assert empty; assert full if needed (when write pointer=read pointer)

- 01: advance read pointer; de-assert full; asserted empty if needed (when write pointer=read pointer)

65

RTL Hardware Design Chapter 9 by P. Chu

RTL Hardware Design Chapter 9 62 by P. Chu

- register process(clk, reset) w\_ptr\_reg <= (others=>'0'); r\_ptr\_reg <= (others=>'0'); elsif (clk'event and clk='1') then

w\_ptr\_reg <= w\_ptr\_next;

r\_ptr\_reg <= r\_ptr\_next;

end if; end process; -- statue FF process(clk, reset) begin if (reset='1') then full\_reg <= '0'; empty\_reg <= '1'; elsif (clk'event and clk='1') then full\_reg <= full\_next; empty\_reg <= empty\_next; end if: end process; RTL Hardware Design by P. Chu Chapter 9

11

#### Non-binary counter for the pointer

- Exact location does not matter as long as the write pointer and read pointer follow the same pattern

- Other counters can be used for the second scheme

- E.g, use LFSR

```

u_ptr_succ <=

(u_ptr_reg(1) xor u_ptr_reg(0)) & u_ptr_reg(3 downto 1);

r_ptr_succ <=

(r_ptr_reg(1) xor r_ptr_reg(0)) & r_ptr_reg(3 downto 1);</pre>

```

RTL Hardware Design Chapter 9 69 by P. Chu

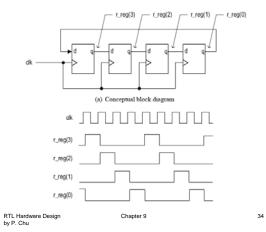

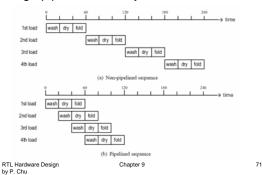

## 4. Pipelined circuit

- Two performance criteria:

- Delay: required time to complete one task

- Throughput: number of tasks completed per unit time.

- · E.g., ATM machine

- Original: 3 minutes to process a transaction delay: 3 min; throughput: 20 trans per hour

- Option 1: faster machine 1.5 min to process delay: 1.5 min; throughput: 40 trans per hour

- Option 2: two machines delay: 3 min; throughput: 40 trans per hour

- · Pipelined circuit: increase throughput

RTL Hardware Design Chapter 9 70 by P. Chu

- Pipeline: overlap certain operation

- E.g., pipelined laundry:

- · Non-pipelined:

- Delay: 60 min

- Throughput 1/60 load per min

- Pipelined:

- Delay: 60 min

- Throughput k/(40+k\*20) load per min about 1/20 when k is large

- Throughput 3 times better than non-pipelined

RTL Hardware Design Chapter 9 72 by P. Chu

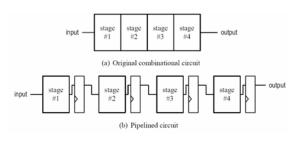

# Pipelined combinational circuit

RTL Hardware Design Chapter 9 73 by P. Chu

# Adding pipeline to a comb circuit

- · Candidate circuit for pipeline:

- enough input data to feed the pipelined circuit

- throughput is a main performance criterion

- comb circuit can be divided into stages with similar propagation delays

- propagation delay of a stage is much larger than the setup time and the clock-to-q delay of the register.

RTL Hardware Design Chapter 9 75 by P. Chu

#### • Procedure

- Derive the block diagram of the original combinational circuit and arrange the circuit as a cascading chain

- Identify the major components and estimate the relative propagation delays of these components

- Divide the chain into stages of similar propagation delays

- Identify the signals that cross the boundary of the chain

- Insert registers for these signals in the boundary.

RTL Hardware Design Chapter 9 76 by P. Chu

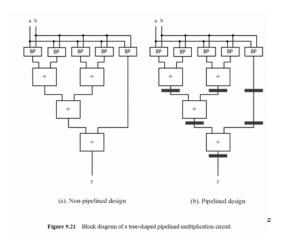

# Pipelined comb multiplier

RTL Hardware Design Chapter 9 77 by P. Chu

```

begin

au <= unsigned(a);

bv0 \le (others = > b(0)):

(others=>b(1));

bv1 <=

(others=>b(2));

bv3 <=

(others=>b(3));

bv4 <=

(others=>b(4));

bv5 <=

(others=>b(5)):

bv6 \le (others = > b(6)):

bv7 <= (others => b(7));

p0 <="00000000" & (bv0 and au);

p1 <="0000000" & (bv1 and au) & "0";

<="000000" & (bv2 and au) & "00";

p3 <= "00000" & (bv3 and au) & "000";

p4 <= "0000" & (bv4 and au) & "0000";

p5 <= "000" & (bv5 and au) & "00000";

p6 <= "00" & (bv6 and au) & "000000";

p7 <= "0" & (bv7 and au) & "0000000"

prod <= ((p0+p1)+(p2+p3))+((p4+p5)+(p6+p7));

y <= std_logic_vector(prod);

end comb1_arch;

```