# **Actel**® **Tools**Designer User's Guide R1-2003

## Actel® Corporation, Sunnyvale, CA 94086

© 2002 Actel Corporation. All rights reserved.

Part Number: 5029122-4 Release: December 2002

No part of this document may be copied or reproduced in any form or by any means without prior written consent of Actel.

Actel makes no warranties with respect to this documentation and disclaims any implied warranties of merchantability or fitness for a particular purpose. Information in this document is subject to change without notice. Actel assumes no responsibility for any errors that may appear in this document.

This document contains confidential proprietary information that is not to be disclosed to any unauthorized person without prior written consent of Actel Corporation.

#### Trademarks

Actel and the Actel logotype, Action Logic, Activator, and Actionprobe are registered trademarks of Actel Corporation.

Windows is a registered trademark of Microsoft in the U.S. and other countries.

Sun Workstations and Sun Microsystems are trademarks or registered trademarks of Sun Microsystems, Inc.

Liberty is a licensed trademark of Synopsys Inc. This product uses SDC, a Proprietary format of Synopsys Inc.

UNIX is a registered trademark of UNIX System Laboratories, Inc.

All other products or brand names mentioned are trademarks or registered trademarks of their respective holders.

# **Table of Contents**

| . xiii . xiii . xiii . xiii . xiii . 11 . 11                    |

|-----------------------------------------------------------------|

| . xiii . xiii . xiii . xiii . 111 . 111 . 130 . 160 . 177 . 200 |

| . xiii . xiii . 11 . 11 . 13 . 16 . 17 . 20                     |

| . xiiii . 11 . 11 . 13 . 16 . 17 . 20                           |

| . 11<br>. 11<br>. 13<br>. 16<br>. 17                            |

| . 11<br>. 13<br>. 16<br>. 17<br>. 20                            |

| <br>. 13<br>. 16<br>. 17<br>. 20                                |

| <br>. 16<br>. 17<br>. 20                                        |

| <br>. 17                                                        |

| <br>. 20                                                        |

|                                                                 |

| . 21                                                            |

|                                                                 |

| . 22                                                            |

| <br>. 23                                                        |

|                                                                 |

| <br>. 27                                                        |

| <br>. 30                                                        |

| <br>. 33                                                        |

| <br>. 35                                                        |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

| ,                                                               |

| <br>. 50                                                        |

| <br>. 53                                                        |

| <br>57                                                          |

|                                                                 |

## Table of Contents

|   | Back-Annotation                                     |  |

|---|-----------------------------------------------------|--|

|   | Generating Programming Files                        |  |

|   | Changing Design Name and Family                     |  |

|   | Changing Design Information                         |  |

|   | Exporting Files                                     |  |

|   | Generating Reports                                  |  |

|   | Setting Designer Preferences                        |  |

|   | Starting other Applications from Designer           |  |

|   | Saving a Design                                     |  |

|   | License Details                                     |  |

|   | Ending the Designer Session                         |  |

| 3 | Scripting                                           |  |

|   | Tcl Overview                                        |  |

|   | Tcl Extension Commands Added by Designer            |  |

|   | PDC Commands                                        |  |

|   | SDC Commands                                        |  |

|   | Tcl Commands for Timer                              |  |

|   | Tcl Commands for PinEdit                            |  |

|   | Running Scripts from the Command Line               |  |

|   | Running Scripts within Designer                     |  |

|   | Recording Scripts                                   |  |

|   | Example Scripts                                     |  |

| A | Constraints in ProASIC and ProASIC PLUS Devices 121 |  |

| Λ | Types of Constraints                                |  |

|   | ProASIC Timing Constraints                          |  |

|   | Highlevel Timing Constraints                        |  |

|   | Timing Constraints                                  |  |

|   | Global Resource Constraints                         |  |

|   | Netlist Optimization Constraints                    |  |

|   | Constraint Quick Reference                          |  |

|   | Constraint File Syntax Summary                      |  |

|   | Constraint in Cyman Cammary                         |  |

## Table of Contents

| В | Setting Up a Printer in UNIX                     |

|---|--------------------------------------------------|

| C | Product Support                                  |

|   | Actel U.S. Toll-Free Line                        |

|   | Customer Service                                 |

|   | Actel Customer Technical Support Center          |

|   | Guru Automated Technical Support                 |

|   | Web Site                                         |

|   | Contacting the Customer Technical Support Center |

|   | Worldwide Sales Offices                          |

|   |                                                  |

|   | Index                                            |

| Designer Software                                                        |

|--------------------------------------------------------------------------|

| Setup Design Dialog Box                                                  |

| Open Design Dialog Box                                                   |

| Designer, Design Session Initiated (PC Version)                          |

| Designer Toolbar                                                         |

| Design Tools Toolbar                                                     |

| Log Window All Anti-fuse Families                                        |

| Starting Designer                                                        |

| Setup Design Dialog Box                                                  |

| Open Design Dialog Box                                                   |

| Import Source Files Dialog Box                                           |

| Add Source File Dialog Box                                               |

| Import Source Files Dialog Box with EDIF File Added                      |

| Import Auxiliary Files Dialog Box                                        |

| Add Auxiliary Files                                                      |

| File Added to the Import Auxiliary Files Dialog                          |

| Importing a PDC File Dialog Box                                          |

| Selecting the PDC Files                                                  |

| PDC File Added to the Import Auxiliary Files Dialog                      |

| Import Auxiliary Files Dialog Box                                        |

| Adding an SDC File                                                       |

| Audited File is Out of Date Dialog Box                                   |

| Update Audit Source Files Dialog Box                                     |

| Device Selection Dialog Box                                              |

| Device Selection Wizard, Device Variations (Screen Varies Depending Upon |

| Device)                                                                  |

| Device Selection Wizard - Variations for the Axcelerator Family 41       |

| Device Selection Wizard, Operating Conditions                            |

| Compile Options Dialog Box, Axcelerator Family                           |

| Compile Options Dialog Box, SX Family                                    |

| Set Variable Dialog Box                                                  |

| Axcelerator Layout Options Dialog Box                                    |

| Other Anti-fuse Families Layout Options Dialog Box |

|----------------------------------------------------|

| ProASIC and ProASIC PLUS Options Dialog Box        |

| Advanced Layout Options (SX, SX-A, and eX)         |

| BackAnnotate Dialog Box                            |

| Generate Fuse File Dialog Box                      |

| Bitstream Generation Dialog Box                    |

| Setup Design Dialog Box                            |

| Bitstream Export Options Dialog Box                |

| Exporting Your PDC File                            |

| Export Timing Files Dialog Box                     |

| Timing Preferences Dialog Box                      |

| Report Type Dialog Box                             |

| Timing Report Dialog Box                           |

| Timing Preferences Dialog Box                      |

| Timing Report                                      |

| Pin Report Dialog Box                              |

| Pin Report                                         |

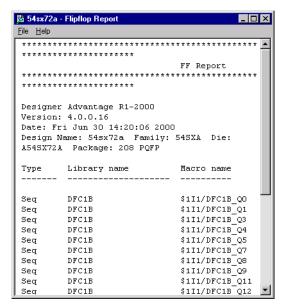

| Flip-Flop Report Dialog Box                        |

| Flip-Flop Extended Report                          |

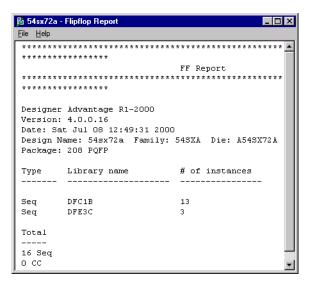

| Flip-Flop Summary Report                           |

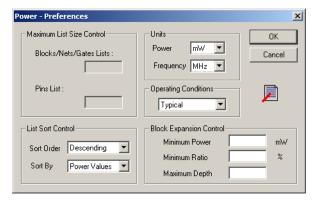

| Power Report Dialog Box                            |

| Power Preferences Dialog Box                       |

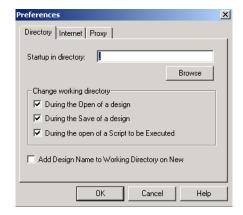

| Directory Preferences Dialog Box                   |

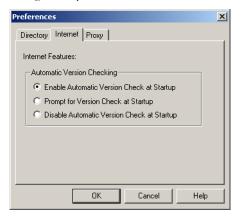

| Internet Tab (in Preferences Dialog Box)           |

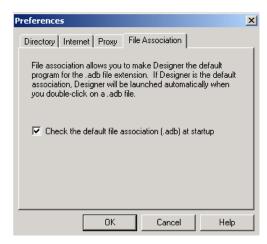

| File Association Tab                               |

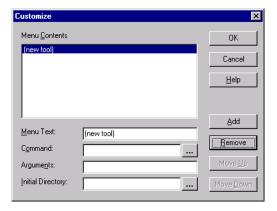

| Customize Dialog Box                               |

| License Details Dialog Box                         |

| Execute Script Dialog Box                          |

| Export Tcl Script Files Dialog Box                 |

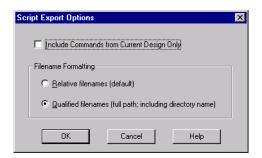

| Script Export Options Dialog Box                   |

| Global Resource Promotion Scheme                   |

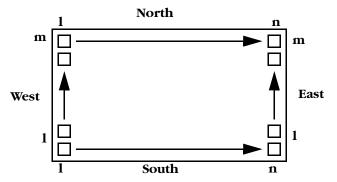

| Pad Locations                                      |

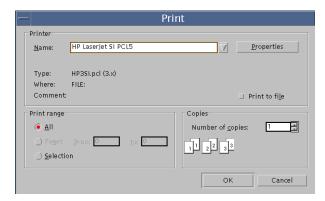

| Drint Dialog Boy 140                               |

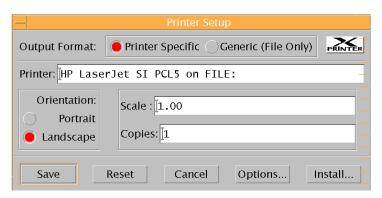

| Printer Setup Dialog Box        |  |  |  |  |  |  |  |  |  |  |  | 149 |

|---------------------------------|--|--|--|--|--|--|--|--|--|--|--|-----|

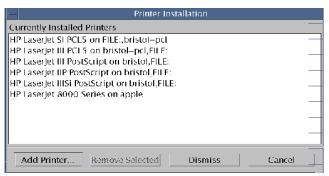

| Printer Installation Dialog Box |  |  |  |  |  |  |  |  |  |  |  | 150 |

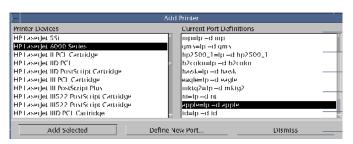

| Add Printer Dialog Box          |  |  |  |  |  |  |  |  |  |  |  | 150 |

## Introduction

The Designer User's Guide contains an overview of Actel's Designer software and the design implementation process.

## **Document Organization**

This guide provides detailed cross-platform information about Designer. Use it as a reference in your everyday work.

Step-by-step instructions for using Designer on Windows and Unix workstations are included in this guide. Any platform differences in procedures and commands are noted in the text.

The Using Designer Guide is divided into the following chapters:

**Chapter 1 - Getting Started** with Designer explains how to invoke and initiate a Designer session and describes Designer's interface, toolbars, and menu commands.

**Chapter 2 - Using Designer** describes how to use the Designer software to optimize and implement designs to program Actel devices.

**Chapter 3 - Scripting** contains information on using Tcl inside Designer. A list of all Designer Tcl extension commands is provided.

**Appendix A - Using Constraints in ProASIC and ProASIC Devices** explains how to create a ProASIC constraint file (.gcf), which can then be imported into Designer.

**Appendix B - Setting up a Printer on UNIX** contains directions on how to set your printer up to work with Designer.

Appendix C - Product Support describes our support services.

**Appendix D - Revision History** contains information on changes made to this guide.

## Document Assumptions

The information in this manual is based on the following assumptions:

- 1. You have installed the Designer Series software.

- 2. You are familiar with UNIX workstations and UNIX operating systems, or with PCs and Windows operating environments.

- 3. You are familiar with FPGA architecture and FPGA design software.

## Platform Support

Supported Platforms include:

PC

- WinNT 4.0 SP6

- Win2000 SP1

- Win98 2nd Edition

- · Windows XP

HP

HP-UX 11.0

Solaris

- Solaris 7

- Solaris 8

## Your Comments

Actel Corporation strives to produce the highest quality online help and printed documentation. We want to help you learn about our products and get your work done quickly. We welcome your feedback about this guide and our online help. Please send your comments to **docs@actel.com**.

# Online Help

Designer comes with online help. Online help specific to each Actel software tool is available.

Introduction

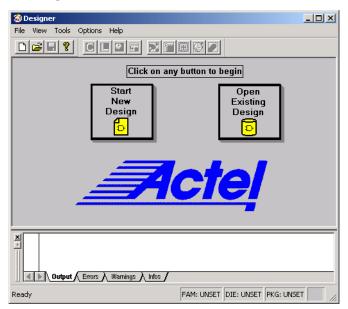

# Designer: Getting Started

This chapter will familiarize you with Designer's graphical user interface and associated menu commands. For more information on how to use Designer, refer to "Using Designer" on page 23.

## Starting Designer

#### To start Designer:

#### 1. On a PC

Choose Designer from the Designer group in the Programs menu under the Start menu.

#### On Unix

Type the following command at the prompt:

#### <location of Actel software>/bin/designer

Designer opens. If this is your first time using Designer, you are asked if you would like to associate the \*.adb file type with Designer. You are also asked if you would like to check for a software update. After making your

## Chapter 1: Designer: Getting Started

selections, Designer opens and is ready for you to begin, as shown in Figure 1-1.

Figure 1-1. Designer Software

## Initiating the Designer Session

To begin a design session, you must start a new design or open an existing design file.

# Starting a New Design

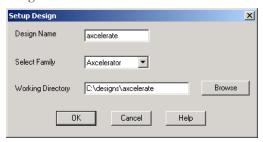

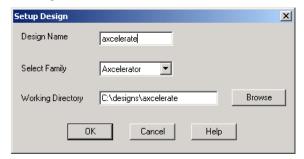

1. Click the *Start New Design* button in the main window, or in the File menu, click *New*. This displays the Setup Design dialog box, as shown in Figure 1-2.

Figure 1-2. Setup Design Dialog Box

#### 2. Setup Design.

- Enter a Design Name. The design name is used in reports and as the default name when saving or exporting files.

- Select an Actel product Family from the drop down menu list.

- Specify a working directory.

#### 3. Click OK.

Designer's custom design flow window appears (as shown in Figure 1-4 on page 20). All Designer's tools and commands are activated.

## Opening an Existing Design

Designer can open designs that have previously been saved, including designs from previous versions of Designer (refer to the next section, "Opening Designs Created in Previous Versions of Designer").

#### To open an existing design:

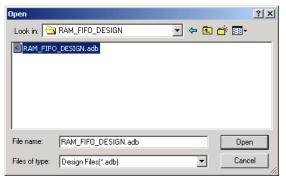

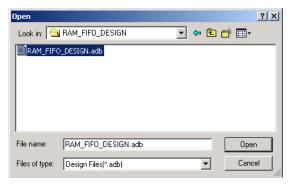

1. Click the *Open Existing Design* button or in the File menu, click *Open*. This displays the Open dialog box (Figure 1-3).

Figure 1-3. Open Design Dialog Box

- Select File. Type the full path name of the ADB file in the File Name box, or select the file from the list.

- 3. Click Open.

Note: When you open an existing design, Designer checks to see if you have modified your netlist since the last time you imported the netlist into this design. If you have, Designer prompts you to re-import your netlist.

Designer's custom design flow window appears (as shown in Figure 1-4 on page 20) and all tools commands are activated.

Opening Designs Created in Previous Versions of Designer

Designer can directly open designs created with previous versions of the Designer software.

Note: If your design was created in version 3.1 or earlier, contact Actel Technical Support or go to http://www.actel.com/support for information on converting your design.

All existing die, package, pin assignment, and place-and-route information is read and maintained. Designs created in previous versions of software may need library conversions when loaded into the Designer environment. If your design requires this conversion, Designer prompts you to allow the software to update the design to the new library before you attempt to start any of the Designer features.

## Designer

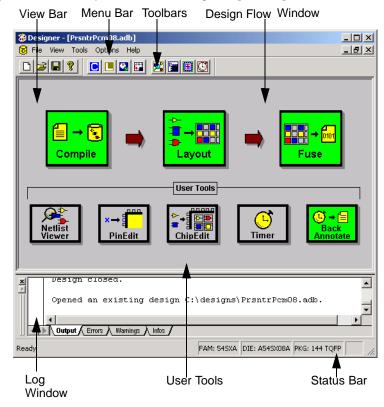

Once you have initiated the design session, Designer displays a design flow specific to the family selected in the Setup Design Dialog Box.

Figure 1-4. Designer, Design Session Initiated (PC Version)

The Design Flow window guides you through the development process, filling in completed steps. The message window displays status and error messages.

## Designer's Menu Commands

Menu commands are different between the PC and UNIX platforms. Differences are noted below. Dialog boxes may look slightly different on the two platforms due to the different window environments. The functionality is the same on both platforms, though the locations of the fields and buttons on the dialog boxes may vary. The names of some fields may also vary between the PC and Unix versions

## File Menu

**New**: Creates a new design.

**Open**: Opens an existing design, an \*.adb file.

**Close**: Closes the design. Save: Saves the design.

**Save As**: Saves the design with a new name.

**Execute Script:** Executes a batch script.

**Import Source Files:** Imports netlist and constraint files.

**Import Auxiliary Files**: Add, modify or delete associated criticality, SDC, PIN, SAIF, Physical Design Constraint Files (PDC), DCF, and VCD files.

Audit Settings: Changes audit settings for imported source files.

**Export: Netlist**: Exports the design netlist.

**Export:** Auxiliary Files: Exports pin, constraint, and BSDL, and placement

files.

**Export: Fuse:** Exports file required to program an antifuse device.

**Export: Bitstream:** Exports file required to program a ProASIC or ProASICPLUS device.

**Export: Timing Files**: Exports timing data for Backannotation.

**Export: Script Files**: Exports a script file.

**Export:** Log Files: Exports a log of the current session.

**Preferences**: Sets design, internet and proxy preferences.

#### Chapter 1: Designer: Getting Started

Recent Files: Lists recent files.

Exit: Exits Designer.

**View Menu** Toolbar: Displays or hides the Toolbar.

**Design Tools**: Displays or hides the Design Tools toolbar.

**Log Window**: Displays or hides the log window.

**Status Bar**: Displays or hides the Status Bar.

**Tools Menu** Setup Design: Selects design name, family, and working directory.

**Device Selection:** Defines die, package, and other parameters.

Compile: Compiles the loaded design.

Layout: Runs layout on the loaded design.

Back-Annotate: Generates delay data.

**Fuse**: Generates fuse data for antifuse devices.

**Bitstream**: Generates a bitstream file for ProASIC and ProASIC devices.

PinEdit: Starts PinEdit.ChipEdit: Starts ChipEdit.

**Netlist Viewer**: Starts the Netlist Viewer tool. **Timer**: Starts Timer for static timing analysis.

**SmartPower:** Starts the power analysis tool.

**Reports**: Generates status, timing, pin flip-flop, and timing violation reports.

**Software Update**: Checks Actel website for latest software updates. **Customize**: Adds custom macros to Designer's tools menu (PC Only).

### **Options Menu**

Netlist Import: EDIF Naming: Sets default EDIF import options.

**Netlist Import: ADL Naming:** Sets default ADL import naming style.

Compile: Sets compile options specific to each family.

Get Variable: Displays a selected variable's value.

**Set Variable**: Sets a selected variable's value.

**Clear Log**: Clears the session log.

## Window (PC Only)

**Arrange Icons**: Arrange icons at the bottom of the Design window.

**Cascade**: Arrange windows in the Design window so they overlap.

**Tile Horizontally:** Arrange windows in the Design window as non-

overlapping tiles.

**Tile Vertically**: Arrange windows in the Design window as non-overlapping

tiles.

**Close Design**: Closes the current design.

## Help Menu

**Help Topics**: Lists help topics.

Reference Manual: Lists available online manuals.

**Actel on the Web**: Starts your internet browser and opens the Actel website

or the Actel Product Support Portal.

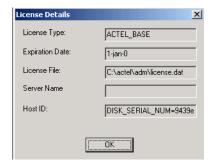

License Details: Displays information about your license.

**About Designer**: Displays program information and current version.

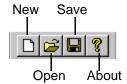

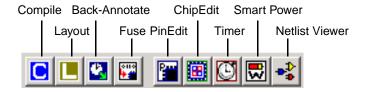

## Toolbar

Frequently used commands are available from Designer's toolbars. Use the View menu to display or hide these toolbars.

If you position the mouse pointer over a toolbar button, a short description (called a tool tip) appears next to the button and a longer description appears in the status bar at the bottom of the main window.

Figure 1-5. Designer Toolbar

Figure 1-6. Design Tools Toolbar

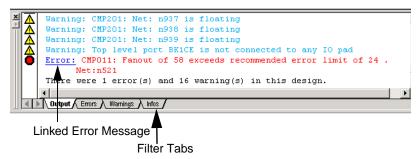

## Log Window

For ProASIC and ProASIC families the log window displays notes and warnings. For Antifuse families, the log window displays error, warning, and informational messages. Messages are represented by symbols and color coded:

| Туре        | Symbol   | Color |  |  |  |  |  |  |

|-------------|----------|-------|--|--|--|--|--|--|

| Error       | •        | Red   |  |  |  |  |  |  |

| Warning     | <u> </u> | Blue  |  |  |  |  |  |  |

| Information | 0        | Black |  |  |  |  |  |  |

Table A-1.

While the Output tab displays everything, you can filter for errors, warnings, or informational messages by clicking the other tabs. The views within the error, warnings, and infos displays are reset when a new command is executed or a new design is opened. To see a complete history of your design session(s), click the output tab.

Figure 1-7. Log Window All Anti-fuse Families

## Chapter 1: Designer: Getting Started

Error and warning messages that are dark blue and underlined are linked to online help to provide you with more details or helpful workarounds.

## Status Bar

As you roll your mouse over commands, tool tips appear in the left part of the status bar. Family, die, and package information always appear in the left corner of the status bar.

## **Using Designer**

This chapter contains information on how to use Designer. For an overview of Designer's interface and commands, please refer to "Designer: Getting Started" on page 15. This chapter covers the general design flow process for implementing your design, including:

- Starting and Initiating a Design Session on page 24

- Importing Source Files on page 27

- Importing Auxiliary Files on page 30

- Importing PDC Files (Axcelerator family only) on page 33

- Importing SDC Files on page 35

- Auditing Files on page 37

- Device Selection Wizard on page 39

- Compiling a Design on page 44

- Compile Options on page 45

- User Tools on page 47

- Layout on page 50

- Layout Failures on page 57

- Back-Annotation on page 58

- Generating Programming Files on page 60

- Changing Design Name and Family on page 65

- Exporting Files on page 67

- Generating Reports on page 72

- Setting Designer Preferences on page 83

- Starting other Applications from Designer on page 86

- Saving a Design on page 87

- License Details on page 88

- Ending the Designer Session on page 88

## Starting and Initiating a Design Session

Before you implement a design, you must start Designer and initiate a design session.

#### To start Designer:

From the Start menu, click Programs. From the Programs menu, select Designer and Click *Designer Series*.

#### Unix

Type the following command at the prompt:

#### <location of Actel software>/bin/designer

Designer opens and is ready for you to initiate your Designer Session, as shown in Figure 2-1.

Figure 2-1. Starting Designer

After starting Designer, you are ready to begin your design session. Begin the design session by starting a new design or opening an existing design file.

# Starting a New Design

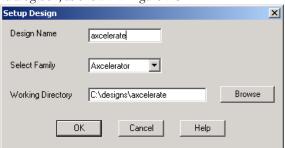

1. Click the *Start New Design* button in the main window, or in the File menu, click *New*. This displays the Setup Design dialog box, as shown in Figure 2-2.

Figure 2-2. Setup Design Dialog Box

#### 2. Setup Design.

- Enter a Design Name. The design name is used in reports and as the default name when saving or exporting files.

- Select an Actel product Family from the drop down menu list.

- Specify a working directory. (Do not use spaces in the directory name.)

#### 3. Click OK.

Designer's custom design flow window appears (as shown in Figure 1-4 on page 20). All Designer's tools and commands are activated.

## Opening an Existing Design

Designer can open designs that have previously been saved, including designs from previous versions of Designer (refer to the next section, "Opening Designs Created in Previous Versions of Designer").

#### To open an existing design:

1. Click the *Open Existing Design* button or in the File menu, click *Open*. This displays the Open dialog box (Figure 2-3).

Figure 2-3. Open Design Dialog Box

- Select File. Type the full path name of the ADB file in the File Name box, or select the file from the list.

- 3. Click Open.

Note: When you open an existing design, Designer checks to see if you have modified your netlist since the last time you imported the netlist into this design. If you have, Designer prompts you to re-import your netlist.

Designer's custom design flow window appears (as shown in Figure 1-4 on page 20) and all tools commands are activated.

Opening

Designs

Created in

Previous

Versions of

Designer

Designer can directly open designs created with previous versions of the Designer software.

Note: If your design was created in version 3.1 or earlier, contact Actel Customer Technical Support or go to http://www.actel.com/support for information on converting your design.

All existing die, package, pin assignment, and place-and-route information is read and maintained. Designs created in previous versions of software may need library conversions when loaded into the Designer environment. If your design requires this conversion, Designer prompts you to allow the software to update the design to the new library before you attempt to launch any of the Designer features.

## Importing Source Files

Design implementation begins with importing source files. Source files include your netlist and constraint files, such as the files in Table 2-1:

File Type Extension

EDIF \*.ed\*

Verilog \*.v

VHDL \*.vhd

Actel ADL Netlist \*.adl

Criticality \*.crt

Flash Constraint File \*.gcf

.pdc

Physical Design Constraint

File

Table 2-1. Source Files

### Chapter 2: Using Designer

The choice of source files is family dependent. Only supported source files are displayed in the Import Source dialog box. If you are working on a new design or if you have changed your netlist, then you must re-import your netlist into Designer.

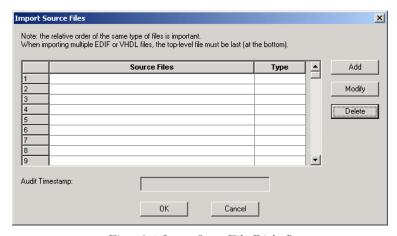

### To import a source file:

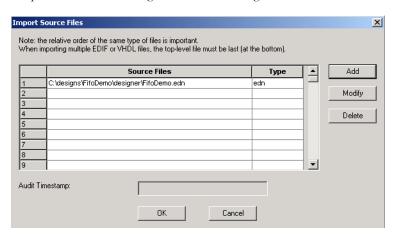

**1. In the File menu, click** *Import Source Files.* This displays the Import Source Files dialog box, as shown in Figure 2-4.

Figure 2-4. Import Source Files Dialog Box

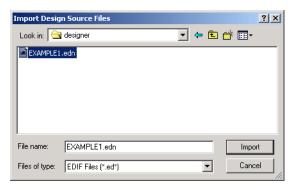

**2. Click the** *Add* **button.** The Add Source Files dialog appears, as shown in Figure 2-5.

Figure 2-5. Add Source File Dialog Box

**3. Select your EDIF netlist and click** *Import.* The File is added to the Import Source Files dialog box.as shown in Figure 2-6.

Figure 2-6. Import Source Files Dialog Box with EDIF File Added

**4. Add any more source files to the list.** All files added to the Import Source Files dialog box are imported at the same time.

If you need to modify a selection, select the file row and click *Modify*.

If you need to delete a file, select the file row and click *Delete*.

- **5. Ordering your source files.** Select and drag your files to specify the import order. Specifying a priority is useful if you are importing multiple netlist files, .gcf files, or .pdc files. When importing multiple EDIF or structural HDL files, the top-level file must appear last in the list (at the bottom).

- **6. After you are done adding all your source files, click** *OK***.** Your source files are imported. Any errors appear in Designer's Log Window.

Note: Do not use spaces in your file or path names. Rename the file or path, removing the spaces, and re-import.

## Importing Auxiliary Files

Auxiliary Files include are listed in Table 2-2:

Table 2-2. Auxiliary Files

| File Type                             | Extension |

|---------------------------------------|-----------|

| Criticality                           | *.crt     |

| PIN                                   | *.pin     |

| SDC                                   | *.sdc     |

| Physical Design Constraint            | *.pdc     |

| Value Change Dump                     | *.vcd     |

| Switching Activity Interchange Format | *.saif    |

| Design Constraint File                | *.dcf     |

Note: .vcd and .saif are used by SmartPower for power analysis. Refer to the *SmartPower User's Guide* for more details about performing power analysis.

Note: Criticality (.crt) is a legacy file format. It is supported for the following families: ACT1, ACT2, ACT3, 40MX, and 42MX.

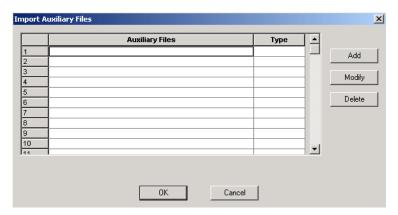

### To import an auxiliary file:

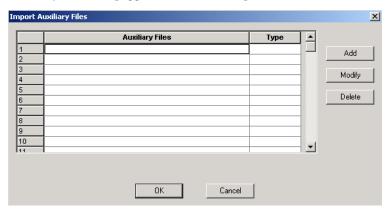

**1. From the File menu, click** *Import Auxiliary Files.* The Import Auxiliary Files dialog appears, as shown in Figure 2-7.

Figure 2-7. Import Auxiliary Files Dialog Box

**2. Click** *the Add* **button.** The Add Auxiliary Files dialog box appears, as shown in Figure 2-8.

Figure 2-8. Add Auxiliary Files

Filter for files by using the Files of Type drop-down list box.

3. Select your file and click *Import*. The file is added to the Import Auxiliary Files dialog box, as shown in Figure 2-9.

Figure 2-9. File Added to the Import Auxiliary Files Dialog

- 4. Continue to add more auxiliary files to the list.

- To modify a selection, select the file row and click Modify.

- To delete a file, select the file row and click Delete.

- **5. Ordering your source files.** Select and drag your files to specify the import order. Specifying a priority is useful if you are importing multiple netlist files, .gcf files, or .pdc files.

- **6. After you are done adding all your Auxiliary files, click OK.** Your auxiliary files are imported. Any errors appear in Designer's Log Window.

Note: File names or paths with spaces may not import into Designer. Rename the file or path, removing the spaces, and re-import.

# Importing PDC Files (Axcelerator family only)

The Physical Design Constraint (PDC) file can specify:

- I/O standards and features

- VCCI and VREF for all or some of the banks

- Pin assignments

- · Placement locations

- · Net criticality

The Axcelerator family of devices supports multiple I/O standards (with different I/O voltages) in a single die. You can use ChipEdit and PinEdit to set I/O standards and attributes, or alternatively you can export and import this information in a PDC file.

Physical Design Constraint (PDC) files are TCL script files. For information on TCL, see "Scripting" on page 89. PDC commands, syntax, and examples are listed on page page 100.

PDC files are only supported for the Axcelerator family of devices. The PDC file replaces the PIN file.

## To import a PDC file:

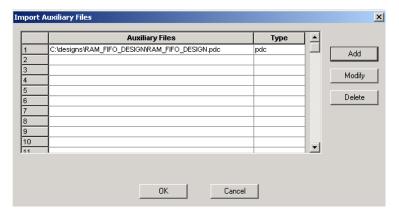

**1. From the File menu, click** *Import Auxiliary Files*. The Import Auxiliary Files dialog appears, as shown in Figure 2-10.

Figure 2-10. Importing a PDC File Dialog Box

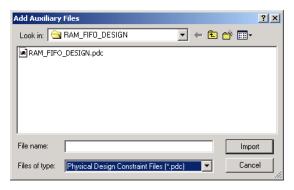

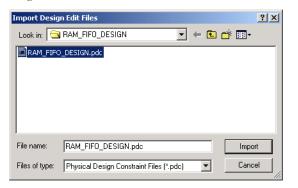

**2. Click** *the Add* **button.** The Add Auxiliary Files dialog box appears, as shown in Figure 2-11.

Figure 2-11. Selecting the PDC Files

Filter for your PDC file by selecting *Physical Design Constraint Files* (\*.pdc) from the Files of Type drop-down list box.

Import Auxiliary Files

Auxiliary Files

Type

C:vlesigns\RAM\_FIFO\_DESIGN\RAM\_FIFO\_DESIGN.pdc

Delete

OK

Cancel

3. Select the PDC file and click *Import*. The file is added to the Import Auxiliary Files dialog box, as shown in Figure 2-12.

Figure 2-12. PDC File Added to the Import Auxiliary Files Dialog

**4. Click OK.** The PDC file is imported into Designer. Any errors appear in the Log Window.

Note: File names or paths with spaces may not import into Designer. Rename the file or path, removing the spaces, and re-import.

# Importing SDC Files

Synopsys Design Constraints (SDC) files can be imported into Designer, to be read by Timer. SDC is a widely used format that allows designers to utilize the same sets of constraints to drive synthesis, timing analysis, and place-and-route.

SDC is a Tcl based format constraint file. The commands of an SDC file follow the Tcl syntax rules. Designer accepts an SDC constraint file generated by a third-party tool. This file is used to communicate design intent between tools and provide clock and delay constraints. The Synopsis Design Compiler, Prime Time, and Synplicity tools can generate SDC descriptions or the user can generate the SDC file manually.

For more information on supported SDC commands and limitations, see "SDC Commands" on page 104.

# Importing SDC Files

## To import an SDC file:

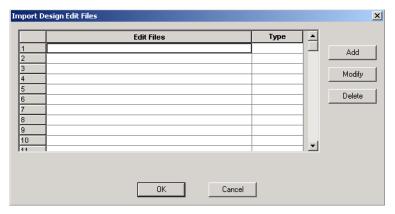

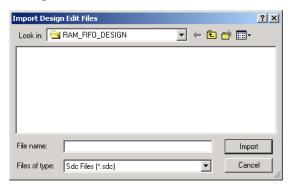

**1. From the File menu, click** *Import Auxiliary Files.* The Import Auxiliary Files dialog box is displayed, as shown in Figure 2-13

Figure 2-13. Import Auxiliary Files Dialog Box

2. Click *Add*. The Add Auxiliary Files dialog box appears, as shown in Figure 2-14.

Figure 2-14. Adding an SDC File

**3. Select your SDC file.** Filter for SDC files by selecting SDC Files in the Files of Type drop-down list box.

- Click Import. The SDC file is added to the Import Auxiliary Files dialog box.

- 5. **Click OK in the Import Auxiliary Files dialog box.** The SDC file is imported into your design. Any errors appear in the Log Window.

Note: File names or paths with spaces may not import into Designer. Rename the file or path, removing the spaces, and re-import.

# **Auditing Files**

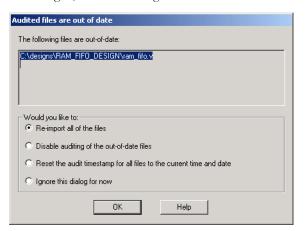

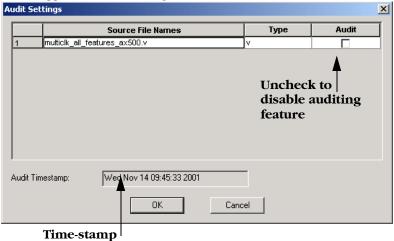

Designer audits your source files to ensure that your imported source files are current. All imported source files are date and time stamped. Designer notifies you if the file is changed, as shown in Figure 2-15.

Figure 2-15. Audited File is Out of Date Dialog Box

When notified, select the appropriate action and click OK. To disable auditing, follow the steps below.

## To change your audit settings:

**1. From the File menu, click** *Audit Settings***.** The Audit Settings dialog box appears, as shown in Figure 2-16.

Figure 2-16. Update Audit Source Files Dialog Box

Audit Timestamp reflects the last time/date that the import source or audit update was successfully done.

2. Disable auditing by un-checking the audit check box next to the file.

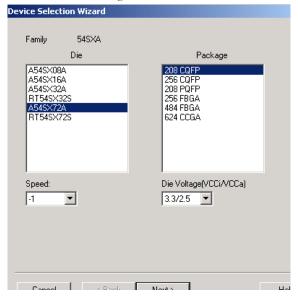

## Device Selection Wizard

After you import your source files, the Device Selection Wizard helps you specify the device, package, and other operating conditions. (You must complete these steps before your netlist can be compiled. Starting compile without completing the device selection automatically starts the Device Selection Wizard.) To change this information for existing designs, refer to "Changing Design Name and Family" on page 65 and "Changing Design Information" on page 66.

## To select device, package, and other operating conditions:

**1. In the Tools menu, click** *Device Selection.* The Device Selection Wizard starts, as shown in Figure 2-17.

Figure 2-17. Device Selection Dialog Box

- **2. Select die and package.** Select a die from the Die list. Available packages are listed for each die. Select a package.

- **3. Specify speed and die voltage.** Select from the available settings in the Speed Grade and Die Voltage drop-down menus. Two numbers separated

by a "/" are shown if mixed voltages are supported. If two voltages are shown, the first number is the I/O voltage and the second number is the core (array) voltage.

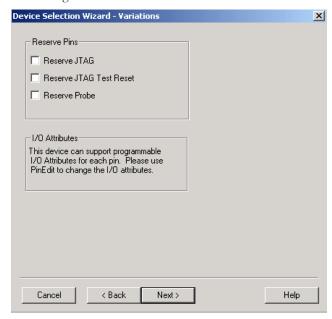

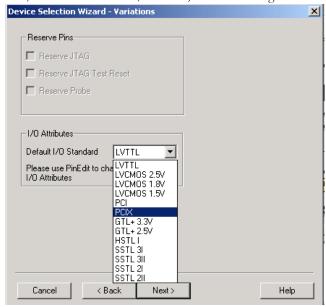

**4. Click** *Next*. The Device Selection Wizard prompts you to set Variations, as shown in Figure 2-18.

Figure 2-18. Device Selection Wizard, Device Variations (Screen Varies Depending Upon Device)

#### 5. Set device variations.

Note: Reserve Pins are not selectable for the Axcelerator, ProASIC, and ProASIC  $\frac{\text{PLUS}}{\text{pamilies}}$  families.

#### Reserve Pins:

- Check the Reserve JTAG box to reserve the JTAG pins "TDI," "TMS," "TCK," and "TDO" during layout.

- Check the Reserve JTAG Reset box to reserve the JTAG reset Pin "TRST" during layout.

• Check the Reserve Probe box to reserve the Probe pins "PRA," "PRB," "SDI," and "DCLK" during layout. (Probe pins are family dependent.)

The I/O Attributes section notifies you if your device supports the programming of I/O attributes on a per-pin basis.

For the Axcelerator family, the I/O Attribute section allows you to set the default I/O standard for the I/O banks, as shown in Figure 2-19.

Figure 2-19. Device Selection Wizard - Variations for the Axcelerator Family

Use PinEdit to assign different I/O standards to different I/O banks, if necessary. (Refer to the *PinEdit User's Guide* for more information on assigning I/O attributes.)

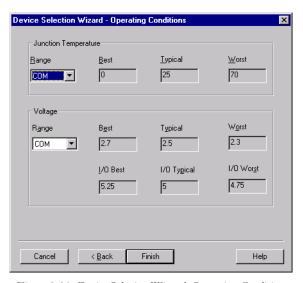

**6. Click** *Next***.** The Device Selection Wizard prompts you to set the Operating Conditions.

Figure 2-20. Device Selection Wizard, Operating Conditions

7. Set Operating Conditions and Click Finish. Use the Operating Conditions dialog box (see Figure 2-20) to define the voltage and temperature ranges a device encounters in a working system. Supported ranges include standard industry temperature and voltage ranges, including commercial (COM), industrial (IND), and military (MIL). This displays supported ranges. Select Custom in the pull-down menu to specify a custom range. The operating condition range entered in the Operating Conditions dialog box is used by Timer, the timing report, and the back-annotation function. These tools enable you to analyze worst, typical, and best case timing. The operating conditions are summarized in Table 2-3.

| 1 0          |         |             |         |  |

|--------------|---------|-------------|---------|--|

| Timing       | Process | Temperature | Voltage |  |

| Best Case    | Best    | Best        | Best    |  |

| Typical Case | Typical | Typical     | Typical |  |

| Worst Case   | Worst   | Worst       | Worst   |  |

Table 2-3. Operating Conditions

The temperature range represents the junction temperature of the device. For commercial and industrial devices, the junction temperature is a function of ambient temperature, air flow, and power consumption. For military devices, the junction temperature is a function of the case temperature, air flow, and power consumption. Because Actel devices are CMOS, power consumption must be calculated for each design. For most low power applications (e.g. 250mW), the default conditions should be adequate. You can calculate junction temperature from values in the Actel *Data Sheet*, available at http://www.actel.com/techdocs/ds/index.html. Performance decreases approximately 2.5% for every 10 degrees C that the temperature values increase. For Axcelerator, ProASIC, and the ProASIC families please use SmartPower for more accurate power consumption estimation. Refer to the *SmartPower User's Guide* for more information about power consumption.

#### **Temperature Range**

Select a supported temperature range from the pull-down menu (COM, IND, MIL or Custom). If you select Custom, edit the Best, Typical, and Worst fields. Modify the range to the desired value (real) such that Best  $\leq$  Typical  $\leq$  Worst.

#### **Voltage Range**

Select a voltage range from the pull-down menu (COM, IND, MIL or Custom). If you select Custom, edit the Best, Typical, and Worst fields. Modify the range to the desired value (real) such that Best ≥ Typical ≥ Worst. The top row indicates core (array) voltage, or both core and array voltages if they are the same. The lower row shows the I/O voltage for mixed voltage devices, and is ignored for non-mixed voltage devices.

# Compiling a Design

After you import your netlist file(s) and select your device, you must compile your design. Compile contains a variety of functions that perform legality checking and basic netlist optimization. Compile checks for netlist errors (bad connections and fan-out problems), removes unused logic (gobbling), and combines functions to reduce logic count and improve performance. Compile also verifies that the design fits into the selected device.

There are three ways to select the compile command:

- In the Tools menu, click Compile.

- Click the *Compile* button in the Design Flow.

• Click the compile icon in the toolbar.

If you have not already done so, Designer's Device Selection Wizard prompts you to set the device and package. See "Device Selection Wizard" on page 39 for information on the Device Selection Wizard.

During compile, the message window in the Main window displays information about your design, including warnings and errors. Designer issues warnings when your design violates recommended Actel design rules. Actel recommends that you address all warnings, if possible, by modifying your design before you continue.

If the design fails to compile due to errors in your input files (netlist, constraints, etc.), you must modify the design to remove the errors. You must then re-import and re-compile the files.

After you compile the design, you can run Layout to place-and-route the design or use the User Tools (PinEdit, ChipEdit, ProASIC Layout Viewer, Timer, SmartPower, or Netlist Viewer) to perform additional optimization prior to place-and-route.

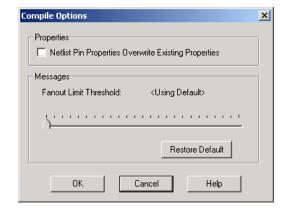

# Compile Options

The compile options are specific to each family. Compile options are not available for the ProASIC and ProASIC PLUS families.

## To set compile options:

- 1. From the Options menu, click *Compile*. The compile option dialog box opens, as shown in Figure 2-21 and as shown in Figure 2-22. Options available from this dialog box are dependent upon your family.

- 2. Select your options and click OK. Options are explained below.

Figure 2-21. Compile Options Dialog Box, Axcelerator Family

Figure 2-22. Compile Options Dialog Box, SX Family

## Netlist Pin Properties Overwrite Existing Properties

During the Compile process, Designer checks the netlist properties. If the netlist file specifies a pin assignment for a pin that was also assigned in PinEdit session, there is a conflict. How this conflict is resolved is determined by your selection in this box.

- If this option is off, or unchecked, then Designer uses the assignment made in PinEdit and the assignment in the netlist file for the conflicting pin is ignored.

- If this option is on, or checked, then Designer uses the assignment in the netlist file for that pin and the PinEdit assignment is ignored.

If you edit pin assignments in PinEdit, this option is automatically set to "off."

## Combine Registers into I/Os

The Axcelerator family includes an optional register on the input path, an optional register on the output path, and an optional register on the 3-state control pin.

Select the option *Combine Registers into I/Os where possible* to take advantage of these registers.

## Abort on PDC Error

Axcelerator family only. Setting *Abort on PDC Error* aborts the PDC import when an error is encountered. When this box is checked, the PDC file is either imported fully or the design is left untouched.

## Fanout Messages

Use the control slider in the Messages area to control the warning level for fanout. Use the control slider to specify the fanout limit that the Compile step checks against. Setting the control slider to '0' informs the system to use the system defaults. Any non-zero value replaces the system default value for the fanout limit with the user-specified value. Typically, this value range is 1 to 24.

This does not adjust the fanout of the design and it has no effect on the netlist. This only adjusts the warning level, by controlling what level of fanout checking you want to be warned about during Compile. Changing this fanout limit option does not invalidate the Compile design state.

Note: This option is available for non Axcelerator, ProASIC and ProASIC PLUS.

## User Tools

After importing and compiling your design, you can, if necessary, optimize and customize your design with the User Tools before running Layout. The User Tools include PinEdit, ChipEdit, ChipView, Netlist Viewer, SmartPower, Timer, and Back-Annotate. Below is a brief summary of the User Tools. Specific details on using these tools can be found in their respective User's Guides.

#### **PinEdit**

Use PinEdit to customize I/O assignments and attributes.

There are two methods for I/O signal placement. You can let Designer automatically assign I/O locations during Layout, or you can manually assign I/O locations prior to Layout.

For non-Axcelerator families Actel recommends that you let Designer automatically assign I/O locations during Layout. You can then use PinEdit to optimize your design, if needed. Layout is designed to place the I/Os for optimum routability and performance. Refer to "Layout" on page 50 for information about automatically assigning I/O locations during place-androute.

When targeting the Axcelerator family and individual I/O bank configuration is needed, you must use PinEdit to assign I/O standards to each bank before running Layout.

Manually assign I/O locations in your design schematic, in imported files, or by using PinEdit. Imported files can include PIN files (non-Axcelerator families), PDC files (Axcelerator family only), or GCF files (ProASIC and ProASIC families only).

Refer to documentation included with your CAE tools for information about assigning I/O signal placement in a schematic or in a pin file. Refer to the *PinEdit's User's Guide* for more information on using PinEdit.

## ChipEdit

Use ChipEdit to view and edit the placement of both I/O and logic macros. Refer to the *ChipEdit's User's Guide* for more information on using ChipEdit.

Note: For the Axcelerator family, you must use ChipEdit before running Layout to place the I/O FIFO Block Controllers. ChipEdit does not support the ProASIC and ProASIC PLUS families.

## ChipView (ProASIC and ProASIC<sup>PLUS</sup> families only)

For the ProASIC and ProASIC PLUS families, ChipView displays the results of place-and-route. These results provide information to guide later place-and-route operations, if necessary. The window creates no new data. It displays the design layout and is used for identifying problems and providing insights to solve them. Refer to the *ChipEdit's User's Guide* for more information on using the ChipViewer.

## **Timer**

Timer performs static timing analysis on your design. Use Timer to analyze timing performance and set timing constraints. If you want to run Timing-Driven Layout, you must use Timer to set and commit timing constraints.

#### **Netlist Viewer**

The Netlist Viewer displays a graphical representation of the netlist. Use it in conjunction with ChipEdit and Timer to locate objects and to trace paths. Refer to the *Netlist Viewer User's Guide* for more information.

## **SmartPower**

SmartPower calculates the power consumption of the currently loaded design. Refer to the *SmartPower User's Guide* for more information.

## Back-Annotate

The backannotation function is used to extract timing delays from your post layout data. These extracted delays are put into a file to be used by your CAE packages timing simulator. Refer to "Back-Annotation" on page 58 of this User's Guide for more information.

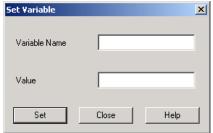

# Place-and-Route Variables (Non-ProASIC and ProASIC PLUS Families)

Use the Set Variable dialog box to set a variable or use Actel scripting to set variables. (For information in scripting commands, refer to "Scripting" on page 89.) Variables must be set before running layout.

#### To set a variable:

**1. From the Options menu, click** *Set Variable.* The Set Variable dialog box appears as shown in Figure 2-23.

Figure 2-23. Set Variable Dialog Box

**2. Enter a Variable Name and Value.** Variables and their values include the following:

#### PLACESEEDRANDOM

Place-and-route uses several different inputs to determine where to start with the algorithms. Some of the inputs include: pin placement, device and package, previously placed macros, timing constraints, etc. In addition, there is another user-definable input called the SEED. This variable enables you to get a different result without changing any of the other place-and-route inputs. This can be valuable for designs that marginally fail to place-and-route. Set this variable to any value between 1 and (2^31) -1 before running Layout. A script to automatically run Layout with different seeds can be found in "Extended Layout" on page 118.

PLACEACCEPTHINTS (Non-Axcelerator Families)

This variable enables you to use the contents of a .loc file as a starting point for layout. The .loc file contains all the placement information for a design. Using this variable is similar to using incremental ON, and should only be used as a last resort for design conversion situations. Make sure the .loc file has the same name as your design and place it in the directory of the design you are working on. Then set this variable to '1' and run Layout.

# Layout

After you compile, the design is ready for layout. Layout takes the netlist information and any constraints and maps this information into the selected Actel device. Layout assigns physical locations to unassigned I/O and logic modules (placement), routing tracks to nets (routing), and calculates detailed delays for all paths (extract).

Designer supports two modes of layout, Standard and Timing-Driven. The physical result of each approach is similar, but the tools and algorithms are quite different. In either mode, the incremental placement option allows you to save the performance of a successfully placed and routed design, even if you change the netlist.

## To layout your design.

## 1. There are three ways to initiate the Layout command:

- In the Tools menu, click Layout.

- Click the Layout button in the Design Flow.

• Click the Layout icon in the toolbar.

This displays the Layout Options dialog box, as shown in Figure 2-24.

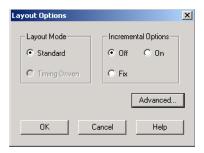

Figure 2-24. Axcelerator Layout Options Dialog Box

Figure 2-25. Other Anti-fuse Families Layout Options Dialog Box

Figure 2-26. ProASIC and ProASIC PLUS Options Dialog Box

**2. Set your Layout options.** Options are family dependent. See "Layout Options" on page 53 for a complete description of these options.

**3. Set your Advanced Layout options (Optional).** Click the *Advanced* button in the Layout dialog box. This displays the Advanced Layout Options dialog box, as shown in Figure 2-27.

Figure 2-27. Advanced Layout Options (SX, SX-A, and eX)

Use the Advanced Layout Options dialog box to select extended run, specify an effort level, and set a timing weight. See "Layout Options" on page 53 for a complete description of these options.

4. Click OK. Layout runs. Status messages appear in the Log window.

# Layout Options

The options available in the Layout and Advanced Layout dialog boxes are family dependent. Below is a description of the various options.

## Layout Mode

#### Standard

Standard layout maximizes the average performance for all paths. Standard layout treats each part of a design equally for performance optimization. Standard layout uses net weighting (or criticality) to influence the results.

Standard layout does not consider delay constraints that have been set for a design during place-and-route. However, a delay report based on delay constraints entered in Timer can still be generated for the design. This is helpful to determine if Timing-Driven Layout is required.

## Timing-Driven

The primary goal of Timing-Driven layout is to meet delay constraints set in Timer, SDC files (Axcelerator family only), DCF files (non-Axcelerator families), and GCF files (ProASIC and ProASIC PLUS) For information on GCF files, refer to "ProASIC Timing Constraints" on page 121.

Timing-Driven layout's secondary goal is to produce high performance for the rest of the design. Delay constraint driven design is more precise and typically results in higher performance.

Note: Timing Driven Layout is available after you have entered timing constraints.

## **Place Options**

#### Run

The Run checkbox selects whether the placer runs during Layout. By default, it reflects the current Layout state. If you have not run Layout before, Run is checked by default. If your design has already been placed, this box is not checked.

#### Incremental Placement Mode

- Off: No previous placement data is used.

- On: Previous placement data is used as the initial placement for the next place run.

- Fix: Previous placement data is used and is fixed for the next place run.

In either Standard or Timing-Driven mode, the Incremental Mode option allows you to preserve the timing of a design after a successful place-and-route, even if you change part of the netlist. Incremental placement has no effect the first time you run layout. During design iteration, incremental placement attempts to preserve the placement information for any unchanged macros in a modified netlist. As a result, the timing relationships for unchanged macros

approximate their initial values, decreasing the execution time to perform Layout.

By forcing Designer to retain the placement information for a portion of the design, some flexibility for optimal design layout may be lost. Therefore, do not use incremental placement to place your design in pieces. You should only use it if you have successfully run Layout and you have minor changes to your design. Incremental placement requires prior completion of Layout. Do not use incremental placement if the previous Layout failed to meet performance goals.

The FIX setting treats all unchanged macros as fixed placements. This is the strongest level of control, but it may be too restrictive for the new placement to successfully complete. The default ON setting treats unchanged macro locations as placement hints, but alters their locations as needed to successfully complete placement. Refer to the *ChipEdit User's Guide* for details on fixing macros.

For ProASIC and ProASIC PLUS designs, Designer always produces a placement constraints file in the design directory called

```

<design>.dtf/Last_placement.gcf.

```

This file contains all the information about the latest placement. Blocks with fixed placement constraints generate fixed placement constraints, while the others generate initial placement constraints. The existing constraint files can be edited to remove any prior placement constraints. The GCF command

```

read "last_placment.gcf";

```

can be added to an existing constraint file to indicate that the latest placement is to be used as the initial placement.

Move or copy "last\_placment.gcf" to use it as an input constraint file. Other wise, it is overwritten by any subsequent placement if it is left in its original location.

Note: For information on .gcf files, refer to "ProASIC Timing Constraints" on page 121.

## Effort Level (Axcelerator Family)

Use the Effort Level slider to increase or decrease the amount of time you want Layout to run. A higher effort level runs Layout for a longer period of time and generally improves the quality of results. The default level is 3.

## **Route Options**

#### Run

Selecting the Run checkbox runs the router during Layout. By default, it reflects the current Layout state. If you have not run Layout before, Run is checked. Run is also checked if your previous Layout run completed with routing failures. If your design has been routed successfully, this box is checked.

#### Incremental Mode

- Off: No previous routing data is used.

- On: Previous routing data is used as the starting point for the next router run.

Incremental routing allows you to fully route a design when some nets failed to route during a previous run. You can also use it when the incoming netlist has undergone an E.C.O. (Engineering Change Order).

Incremental routing should only be used if a low number of nets fail to route (less than 50 open nets or shorted segments).

A high number of failures usually indicates a less than optimal placement (if using manual placement through macros for example) or a design that is highly connected and does not fit in the device. If a high number of nets fail, relax constraints, remove tight placement constraints, or select a bigger device and rerun routing.

## Advanced Layout Options

#### Extended Run

Extended run attempts to improve layout quality by using a greater number of iterations during optimization. An extended run layout can take up to 5 times as long as a normal layout. For scripting information, refer to "Extended Layout" on page 118.

Note: This advanced option is available for all Antifuse Families.

#### Effort Level (SX, SX-A, and eX Families)

This variable specifies the duration of the timing-driven phase of optimization during layout. Its value specifies the duration of this phase as a percentage of the default duration.

The default value is 100 and the selectable range is within 25 - 500. Reducing the effort level also reduces the run time of Timing Driven place-and-route (TDPR). With an effort level of 25, TDPR is almost four times faster. With fewer iterations, however, performance may suffer. Routability may or may not be affected. With an effort level of 200, TDPR is almost two times slower. This variable does not have much effect on timing.

Note: This advanced option is only available for the SX, SX-A, and eX families.

## **Timing Weight**

Setting this option to values within a recommended range of 10-150 changes the weight of the timing objective function, thus biasing TDPR in favor of either routability or performance.

The timing weight value specifies this weight as a percentage of the default weight (i.e. a value of 100 has no effect). If you use a value less than 100, more emphasis is placed on routability and less on performance. Such a setting would be appropriate for a design that fails to route with TDPR. In case more emphasis on performance is desired, set this variable to a value higher than 100. In this case, routing failure is more likely. A very high timing value weight could also distort the optimization process and degrade performance. A value greater than 150 is not recommended.

Note: This advanced option is only available for the SX, SX-A, and eX families

# Layout Failures

If Layout fails at any stage, Designer provides information that can help you determine and correct the problem. This section describes some failures and methods to fix the failures.

## Failures During Timing Driven Layout

Layout can fail during initialization if the assigned constraints are impossible (i.e. no routing path on the device can meet the assigned constraint). You must

change the circuit or relax the constraints to proceed with Timing-Driven Layout.

- Change the Speed Grade to increase minimum delay.

- Modify the design to reduce the number of logic levels in these paths.

- Relax over-restrictive delay constraints. If the constraints from Timer or a DCF file are unnecessarily tight, change them to more realistic values that still satisfy your timing requirements.

- Fixed pin placements may not allow Layout to succeed. Unplace or unfix I/O pins.

## **Back-Annotation**

The backannotation functions are used to extract timing delays from your post layout data. These extracted delays are put into a file to be used by your CAE package's timing simulator. If you wish to perform pre-layout back-annotation, select *Export* and *Timing Files* from the File menu.

#### To back-annotate your design:

1. From the Tools menu, click *Back-Annotate*, or click the *Back-Annotate* button in the Design Flow window. This displays the Back-Annotate dialog box, as shown in Figure 2-28.

Figure 2-28. BackAnnotate Dialog Box

- **2. Extracted Files Directory.** The file directory is your default working directory. If you wish to save the file elsewhere, click *Browse* and specify a different directory.

- 3. Extracted File Names. This name is used as the base-name of all files written out for back-annotation. Do not use directory names or file extensions in this field. The file extensions is assigned based on your selection of which file formats to export. The default value of this field is <design>\_ba.

- **4. Select Output format.** Select an output format the Output Format drop-down menu.

- 5. Select a Simulator Language. Select either Verilog or VHDL93. Simulator Language becomes available when you select SDF as an output format.

- **6. Export Additional Files.** Check Netlist or Pin to export these files at the same time.

- 7. Click OK. The Back-Annotation program creates the files necessary for back-annotation to the CAE file output type that you chose. Refer to Actel Interface Guides or the documentation included with your simulation tool for information about selecting the correct CAE output format and using the back-annotation files.

# Generating Programming Files

Once you have completed your design, and you are satisfied with the back-annotated timing simulation, create your programming file. Depending upon your device family, you need to generate a Fuse, Bitstream or STAPL programming file.

Table 2-4. Programming Files

|   | 8        | 0 |

|---|----------|---|

| D | Antifuse |   |

| Programmer             | Antifuse<br>Programming File    | Flash<br>Programming File                                        |

|------------------------|---------------------------------|------------------------------------------------------------------|

| Flash Pro              | N/A                             | STAPL                                                            |

| Silicon<br>Sculptor I  | Fuse (Non-Axcelerator families) | Dos and Windows: Bit-<br>stream                                  |

| Silicon<br>Sculptor II | Fuse (All families)             | Dos Version: Bitstream<br>Windows Version:<br>Bitstream or STAPL |

#### **Fuse**

Fuse allows you to generate a programming file for your design to program an Actel device.

## Silicon Signature (Antifuse Devices only)

You can specify a unique silicon signature to program into the device when you generate a programming file. This signature is stored in the design database, the programming file, and programmed into the device permanently during programming. With Designer tools, you can use the silicon signature to identify and track Actel designs and devices.

## To generate a programming file:

1. In the Tools menu, click *Fuse* or click the Fuse button in the **Design Flow window.** This displays the Generate Fuse file dialog box (Figure 2-29).

Figure 2-29. Generate Fuse File Dialog Box

- **2. Specify File Type.** Select the appropriate file type in the File Type pull-down menu. Select "AFM-APS2" if you are using a Silicon Sculptor programmer.

- **3. Enter Silicon Signature (Optional).** Enter a 5 digit hexadecimal value in the Silicon Signature box to identify the design. Valid characters are "0" through "9," and "a" through "f."

## 4. Specify File name and directory in the Output filename box.

Designer automatically names the file based on the <design\_name>.adb file. You can change the name by entering it in the File Name box. Click *Browse* to change the directory.

Note: Do not add a file extension or suffix to the file name. The Designer software automatically adds the extension to the programming file name when you specify the programming format.

- **5. Generate Probe File Also.** This option automatically generates a .prb file for use with Silicon Explorer

- 6. Disable clamping diode for unused I/O pins. (SX-A and eX families). Check box to disable clamping diode.

- **7. Save the file.** Click *OK* when finished to save the file.

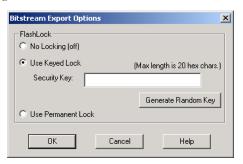

## Bitstream and STAPL Files

JashLock

Bitstream allows you to generate a bitstream or STAPL file for ProASIC and ProASIC PLUS devices. Actel's ProASIC and ProASIC PLUS devices contain FlashLock circuitry to lock the device by disabling the programming and readback capabilities after programming. Care has been taken to make the locking circuitry very difficult to defeat through electronic or direct physical attack.

FlashLock has three options:

#### No Lock

Creates a programming file which does not secure your device.

#### Permanent Lock

The permanent lock makes your device one time programmable. It cannot be unlocked by you or anyone else.

#### **Keyed Lock**

Within each ProASIC and ProASIC device, there is a multi-bit security key user key. The number of bits depends on the size of the device. Table 2-5 and Table 2-6 show the key size of different ProASIC and ProASIC devices,

respectively. Once secured, read permission and write permission can only be enabled by providing the correct user key to first unlock the device.

Table 2-5. Key Size of ProASIC Devices

| Device   | Key Size (bits) | Key Size (Hex) |

|----------|-----------------|----------------|

| A500K050 | 51 Bits         | 13             |

| A500K130 | 51 Bits         | 13             |

| A500K180 | 51 Bits         | 13             |

| A500K270 | 51 Bits         | 13             |

Table 2-6. Key Size of ProASIC PLUS Devices

| Device  | Key Size (Bits) | Key Size (Hex) |

|---------|-----------------|----------------|

| APA075  | 79 Bits         | 20             |

| APA150  | 79 Bits         | 20             |

| APA300  | 79 Bits         | 20             |

| APA450  | 119 Bits        | 30             |

| APA600  | 167 Bits        | 42             |

| APA750  | 191 Bits        | 48             |

| APA1000 | 263 Bits        | 66             |

The maximum security key for the device is shown in the dialog box.

## To generate a bitstream or STAPL file:

1. In the Tools menu, click *Bitstream* or click the *Bitstream* button in the Design Flow window. This displays the Bitstream dialog box (as shown in Figure 2-30).

Figure 2-30. Bitstream Generation Dialog Box

- 2. Select *Bitstream* or *STAPL* from the File Type drop-down list box.

- **3. FlashLock.** Select one of the following options:

- No Locking: Creates a programming file which does not secure your device.

- Use Keyed Lock: Creates a programming file which secures your device with a FlashLock key (see "Keyed Lock" on page 62).

- Use Permanent Lock: Creates a one-time programmable device.

- Click OK. Designer validates the security key and alerts you to any concerns.

Note: The bitstream file header contains the security key.

#### Programming the Security Bit

Two device programmers, Silicon Sculptor and Flash Pro, are available for ProASIC and ProASIC devices. If the programming file contains the security key, by default the Silicon Sculptor and Flash Pro programming software automatically enables the "secure" option and programs the security key. You can turn this off, should you decide not to program using the security key.

Please refer to the application note "Implementation of Security in Actel's ProASIC and ProASIC Flash-Based FPGAs" for more details.

# Changing Design Name and Family

Design name and family are set when you import a netlist and compile a new design. However, you can change this information for existing designs. If you change the family, Designer notifies you that you must re-import the netlist and automatically prompts you when you select the next Designer function. Use the following procedure to change the name of a design and the targeted Actel family for the design.

## To change the design name or family:

**1. In the Tools menu, click** *Setup Design.* This displays the Setup Design dialog box, as shown in Figure 2-31..

Figure 2-31. Setup Design Dialog Box

**2. Specify the design name and family.** Click *OK.* Refer to the Actel *FPGA Data Book* for Actel Family specifications.

# **Changing Design Information**

Device and package information, device variations, and operating conditions are set when you import a netlist and compile a new design. However, you can change this information for existing designs.

#### To change design information for existing designs:

- In the Tools menu, click Device Selection. The Device Selection Wizard appears.

- **2. Select Die, Package, and Speed Grade.** (You must select die and package to continue.) Click *Next*.

- 3. Select Device Variations. Click Next.

- 4. Select Operating Conditions. Click Finish.

Refer to the Actel FPGA Data Book or call your local Actel Sales Representative for information about device, package, speed grade, variations, and operating conditions.

## Changing Device, Package, and Speed Grade

Use the Device Selection dialog box (see Figure 2-17 on page 39) to specify or change the device and package type and the speed grade based on your design needs.

If you select a device, available packages are then displayed in the Package list box. If you select a package, specify a speed grade in the Speed Grade pulldown menu.

Devices that are no longer available from the Device Selection dialog box can be selected using Designer Script. Because these parts may no longer be available, do not use these devices unless approved by Actel.

## Compatible Die Change

When you change the device, some design information can be preserved depending on the type of change.

#### **Changing Die Revisions**

If you change the die from one technology to another, all information except timing is preserved. An example is changing an A1020A (1.2um) to an A1020B (1.0um) while keeping the package the same.

## **Device Change Only**

Constraint and pin information is preserved, when possible. An example is changing an A1240A in a PL84 package to an A1280A in a PL84 package.

## Repackager Function (Non-Axcelerator families only)

When the package is changed (for the same device), the Repackager automatically attempts to preserve the existing pin and Layout information by mapping external pin names based on the physical bonding diagrams. This always works when changing from a smaller package to a larger package (or one of the same size). When changing to a smaller package, the Repackager determines if any of the currently assigned I/Os are mapped differently on the smaller package. If any of the I/Os are mapped differently, then the layout is invalidated and the unassigned pins identified.

# Exporting Files

Designer lets you export auxiliary files (.afl, .bsd, .cob, .crt, .dcf, .gcf, .loc, .pdc, .pin, .prb, .saif, seg, .vdc), fuse files (.afm, .dio, .fus), bitstream files (.bit), log files (.log), netlist files (.adl, .edn, structural VHDL, STAPL files (.stp), and structural Verilog), script files (.tcl), stamp files (\*.mod and \*data), and delay files (.stf and .sdf) from your design.

Note: Designer does not support VHDL 87 in export. Exported file types are family dependent.

## To export a file:

- 1. In the File menu, click an export option from the *Export* submenu. Select *Netlist, Auxiliary, Fuse, Bitstream, Timing, Script*, or *Log* files. This displays a dialog box specific to the file type.

- 2. Specify file name and file type.

- 3. Click OK.

## Exporting Bitstream Files

For important information on Bitstream and STAPL files, read "Bitstream and STAPL Files" on page 62.

#### To export a bitstream file:

- 1. In the File menu, click the *Bitstream* export option from the Export sub-menu.

- **2. Specify file name and file type.** Designer supports two file types, bitstream (\*.bit) for Silicon Sculptor, and STAPL (\*.stp) files for programming systems that support the STAPL standard.

- **3. Click OK.** This displays the Bitstream Export Options dialog box, as shown in Figure 2-32.

Figure 2-32. Bitstream Export Options Dialog Box

**4. Read and follow the instructions in** "Bitstream and STAPL Files" on page 62.

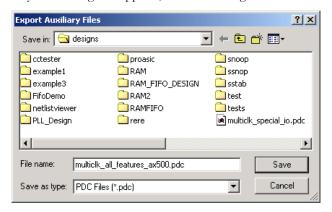

# Exporting PDC Files

## To export a Physical Design Constraint (PDC) file:

1. From the File Menu, select *Export*, and click *Auxiliary Files*. . . from the Export sub-menu. The Export Auxiliary Files dialog box appears, as shown in Figure 2-33

Figure 2-33. Exporting Your PDC File

- Save in: Navigate to the drive and folder where you want to save the file.

- File Name: Type your file name.

- Save As Type: Select PDC.

#### 2. Click Save.

## Exporting STAMP files

Designer supports Stamp model generation for the eX, Axcelerator, SX-A, and RTSX-S families. Stamp is an industry-standard file format that contains timing data. Stamp models are read by board timing verification tools, such as Mentor Graphics's TAU and Viewlogic's BLAST.

The Stamp model for a design consists of two files:

- The \*.mod file describes the Interface (IOs) and all timing arcs of the model.

- The \*.data file gives a timing value for each timing arc defined in the model.

Designer supports the following subset of Stamp modeling language for best, typical, and worst operating conditions:

#### Chapter 2: Using Designer

- Inputs to Outputs propagation delay arcs, for shortest and longest paths.

- Inputs setup and hold timing-check arcs.

- Clock period timing-check arcs.

## To export a STAMP file:

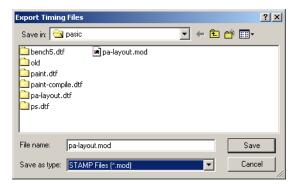

1. In the File Menu, click the *Timing* export option from the **Export sub-menu**. This displays the Export Timing Files dialog box, as shown in Figure 2-34.

Figure 2-34. Export Timing Files Dialog Box

- 2. Select STAMP from the Save As Type list box.

- 3. Enter a file name in the File Name text box, followed by .mod, and click *Save*. The Preferences dialog box appears, as shown in Figure 2-35.

Note: The corresponding \*.data file is generated with the same name.

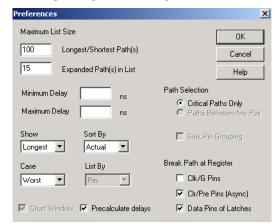

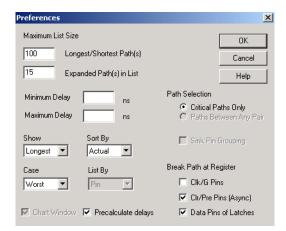

Figure 2-35. Timing Preferences Dialog Box

**4. Set your preferences and click** *OK***.** Timer exports the file to the area specified in the Export Timing Files dialog box. For information on setting preferences, please refer to the *Timer User's Guide*.

Note: Inputs to Outputs /Shortest/Longest delays cannot be generated in the same data file. You must output two separate Stamp files.

Longest Paths / Shortest Paths selection in the Preferences dialog box only affects Inputs to Outputs propagation delays and does not affect Period, Setup, and Hold timing-check delays.

Operating conditions potentially affect all timing values of the Stamp data file. It is necessary to export 3 separate Stamp files if best/typical/worst models are needed.

## Generating Reports

Designer's reports provide you with frequently used information in a convenient format.

## To generate a report:

In the Tools menu, click Reports. The Report Types dialog box appears.

Figure 2-36. Report Type Dialog Box

2. Select a report type from the drop-down menu and click OK.

## Status Report

The status report enables you to create a report containing device and design information, such as die, package, percentage of the logic and I/O modules used, etc.

## To generate a status report:

- 1. In the Tools menu, click Reports.

- 2. Choose Status from the drop-down list in the Report Type dialog box. The status report opens in a separate window. You can save or print the report.

## Timing Report

The timing report enables you to quickly determine if any timing problems exist in your design. The timing report lists the following information about your design:

- maximum delay from input I/O to output I/O

- maximum delay from input I/O to internal registers

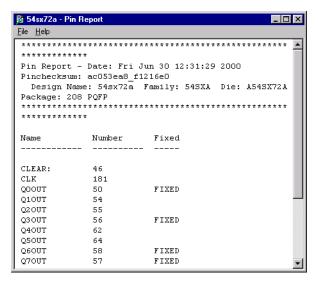

- maximum delay from internal registers to output I/O