## EXCALIBUR™

16

╘श∕ѧ∖

# Excalibur-Nios Embedded Software Processor Core

## Enter a New Realm of Technology....

Quartus II Limited Edition

- PCI32 Nios Target

- Nios Ethernet Development Kit (NEDK)

- Microtronix Linux Development Kit (LDK)

- Nios 2.0

Competitive Landscape

## Quartus II Limited Edition

© 2001

## Quartus II Limited Edition

- Provides device compilation for Nios Development Kit customers

- Feature set based on Quartus II Web Edition, with some extra features to support Nios

- TCL scripting

- LeonardoSpectrum synthesis for Nios core

- Development kit-specific devices:

- EP20K200EFC484 Used in NDK

- EP20K200EBC652

- EP20K100EQC240

See <u>https://go.altera.com/extranet2001/products/literature/mb\_2001/mb\_411.dzc</u> for QII Web edition details.

- Provided to all Nios customers, starting in September

- Shipped to all current Nios custor ters

- Shipping today with all new Excalibur Nios Development Kits

## Quartus II LE Key Points Current Quartus II subscribers do not need to install QII LE

#### Obtaining License Files

- Altera sends an email that includes a new license file for QII LE to all current Nios customers.

- Quartus II v1.1 enabled through October 31, 2001

- Quartus II Limited Edition enabled to eternity

- The QII LE shipment also includes explicit instructions how to obtain a license online.

NOTE: LogicLock is not enabled in QII LE

May affect customers with high performance needs

- "Where do I download a copy of OI LE?

- Answer: You don't.

Quartus II LE is shipped with the Nios Development Kit or upgrades only

System-On-a-Programmable-Chip Solutions

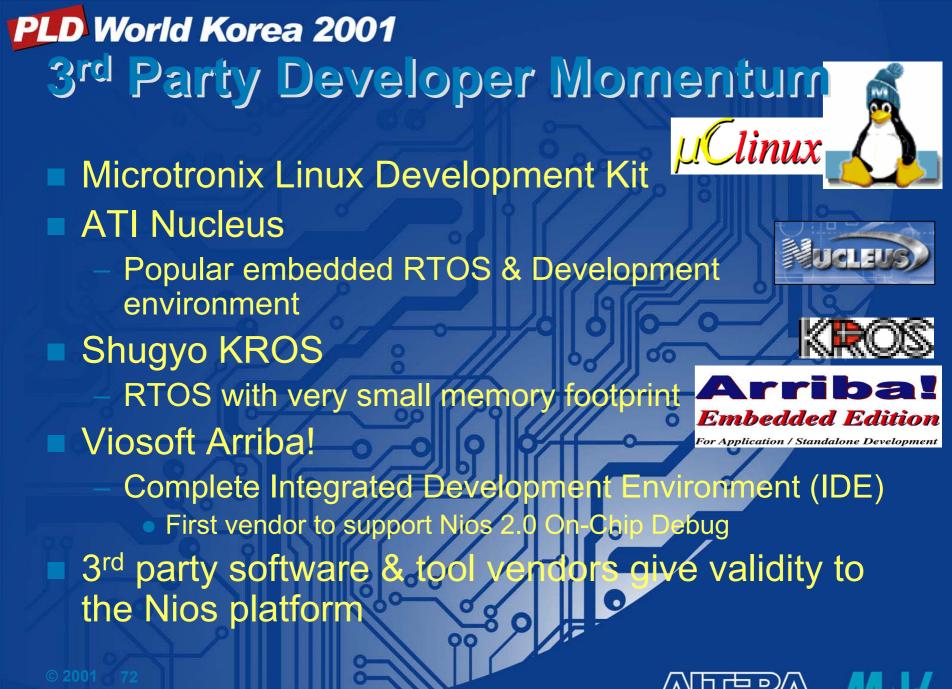

# PLD World Korea 2001 Nucleus PLUS by ATI

**Nucleus PLUS Evaluation CD included in** Quartus II LE shipment Popular embedded RTOS Used in thousands of applications Small memory footprint and minimal CPU overhead Source code No royalties More information: www.acceleratedtechnolo

PLD World Korea 2001 KROS by Shugyo Design Technologies KROS "Preview" CD included in Quartus II LE shipment Full release in October Embedded RTOS Supports POSIX API Very small memory footprint Source code No royalties \$5000 Per-product license More information: www.shugyodesign.com

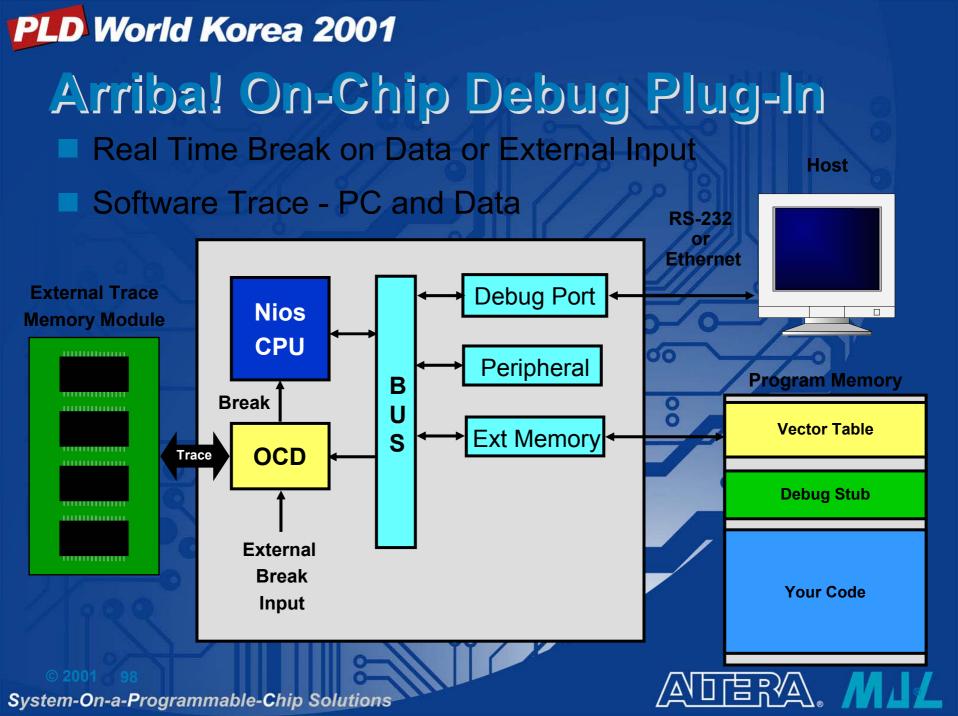

# PLD World Korea 2001 Arriba! By Viosoft

or Application / Standalone Development

- Evaluation CD included in Quartus II LE shipment

- Complete Integrated Development Environment (IDE)

- Edit, Compile, Download, Run ,Debug

- Fully integrated mixed-mode, source-level C/C++ debugger

- First vendor to support Nios 2.0 On-Chip Debug

- For more information:

- www.viosoft.com

© 2001

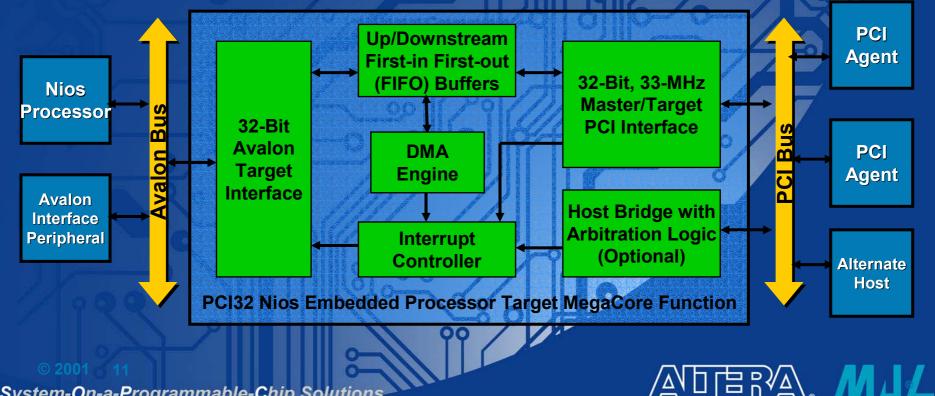

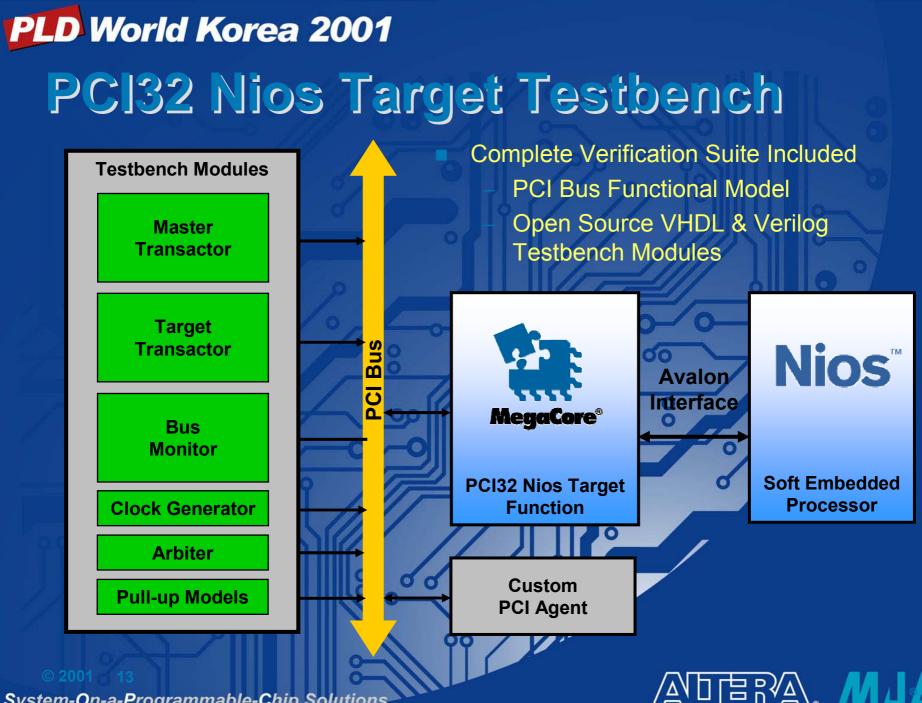

# PCI32 Nios Target MegaCore Function

PLD World Korea 2001 PCI32 Nios Target MegaCore® Function PCI Interface to Nios via Avalon™ Bus Bridge **Nios System Builder Interface Behavioral Simulation Models** PCI Testbench for PCI32 Nios Target Core Low-Level Driver Routines in C Source Code for Nios **Embedded Processor Reference Design for Use with Nios Embedded** Processor **Complete Documentation** List Price: \$2,495 Available: Oct 2001

## PLD World Korea 2001 PCI32 Nios Target Architecture

- Simple, Integrated Bridge Solution

- **Includes Optional PCI Host Bridge Capability**

- Implemented as External Peripheral to Nios Processor

- Approximately 3,000 Logic Elements (LEs)

## PLD World Korea 2001 Nios System Builder

- Simple, Integrated Design Entry

Steps to Instantiate PCI32 Nios Target

- Download the PCI32 Nios Target From the IP MegaStore™ Site

- http://www.altera.com/IPmegastore

- Start the Nios System Builder

- Select PCI32 Nios Bridge from Drop-Down Menu

- Parameterize PCI Bridge Options

- Specify Avalon Address Space & Interrupts

- Connect Core to Avalon System Block

- Compile Project in Quartus<sup>®</sup> I Software

#### Peripheral Name unnamed\_peripheral Type of peripheral C Inside Nios System Module Select a peripheral to instantiate inside the system module. Built-in peripheral library: Outside Nics System Module Add a set of interface signals for connecting a device which resides outside the system module. External peripheral library: selections ---- select one --User-Defined Interface 16-bit Flash (1Mbyte AM29LV800BB chip) 16-bit Flash (16Kbytes within an AM29LV800BB chip) 16-bit SRAM (32Kbytes within an IDT71V016 chip) 32-bit SRAM (256Kbytes in two IDT71V016 chips) Altera NIOS to PCI MT32 Bridge

🚯 Add New Peripheral To System Module

## PLD World Korea 2001 PCI32 Nios Target Add-On Kit

#### Kit Contents

- PCI32 Nios Target MegaCore Function

- PCI Daughter Card for Nios Development Board

- Universal 32-bit Edge Connector & 5V PCI Slot

- PMC Connectors to Nios Board

- Hardware Reference Design

- Price: \$2,795

Availability: Late Q4 2001

## PLD World Korea 2001 PCI Core Comparison

#### PCI/MT32 (32-bit, 66-Mhz PCI)

- Fully compliant "general purpose" PCI core

- Master/Target PCI

- Parameterizable

- Host bridge functionality

- Testbench included

- Behavioral models included

- Support for up to five (5) base

- address registers (BARs)

- Complete access to all local-side signals \$8,995

PCI32 Nios Target (32-bit, 33-Mhz PCI)

Fully compliant "Nios-only" PCI core

Master/Target PCI

Parameterizable

Host bridge functionality

Testbench included

Behavioral models included

Support for one (1) base address register (BAR)

Access to PCI through Avalon bus

© 2001

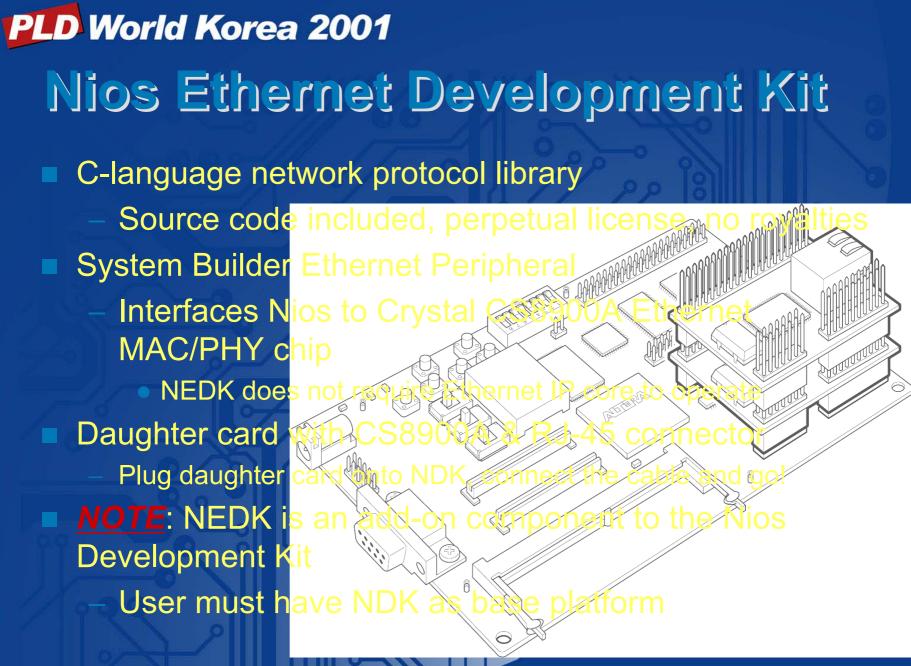

# Nios Ethernet Development Kit (NEDK)

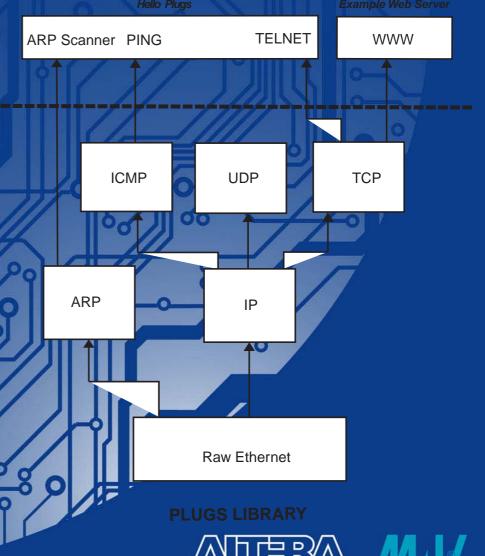

# PLD World Korea 2001 Features - Basics • C libraries to implement network protocols for embedded systems

- OS not required

- Compact memory and processor requirements

- 20KB of memory for code

- 8KB of memory for data

- Nios timer peripheral

#### Parameters to easily configure network feature set

00

- Optimize code size

- Optimize run-time memory requirements

## Features – Protocol Support

- Support for the following protocols:

- Raw Ethernet

- Address resolution protocol (ARP)

- Internet protocol (IP)

- Internet control message protocol (ICMP)

- User datagram protocol (UDP)

- Transmission control protocol (TCP)

Similar functionality to UNIX "sockets" C routines

User can open connections and send data with only a

2001 few lines of C code

System-On-a-Programmable-Chip Solutions

# PLD World Korea 2001 Plugs

"Plugs" is the library of C network functions that ships with NEDK Very similar to UNIX "Sockets" functions Provides all the necessary tools to communicate data over Ethernet There is not a one-to-one relationship between Plugs and Sockets function These functions are not compatible with any other Ethernet protocol

# What do you get in the box?

- Hardware:

- NEDK Daughter Card. Mounts on NDK Dev Board.

- Ethernet cable & cross-over adapter

- Support for both NEDK-to-LAN and NEDK-to-PC connection

Installer CD-ROM

- Software tools: System Builder Nios Ethernet Peripheral

- Embedded software: Network Protocol Libraries

- C Source Code

- Software reference application: Web Server

- Hardware reference design: Nios CPU platform

- Networked Nios platform functions straight out of the box

Protocols

- **Documentation:**

- Nios Ethernet Development Kit User Guide http://www.altera.com/literature/ug/ug\_niosedk.pdf

- System-On-a-Programmable-Chip Solutions

#### PLD World Korea 2001 **Potential NEDK customers** Designers of simple, networked devices Want network connectivity, but don't want the overhead of Linux for network functions OS not required NEDK is perfect to enable a Nios system to communicate system data over a network Systems that require remote programming over network Reprogram flash (including Nios design!) and MAX devices in the Altera can give out reference design & source code Systems that require a faster interface than a standard serial cable In general, Ethernet is a means a communication lows much faster data download Ex: GERMS monitor over Ethernet to the Nios Development Board System-On-a-Programmable-Chip Solutions

PLD World Korea 2001 **troggues & noitemnotal pairebro NIOS-EDKX** \$495 Available **NOW** For support: **Altera Applications** Apps is first point of contact. May be referred to Excalibur Apps Provides install & basic "getting started" support Design support for Altera device 0 **Excalibur** Applications Support for in-depth Nios dep e n ssues with Ethernet

© 2001

# Linux Development Kit, by Microtronix

- Nios Linux Development Kit (LDK)

Linux for Nios!

- µCLinux ported to the Nios processor

- Complete hardware and software platform that enables Linux development straight out of the box

A Linux prompt in 30 minutes, or the source code is free!

Not a "Linux for

- Dummies" platform Designed & Produced by Microtronix

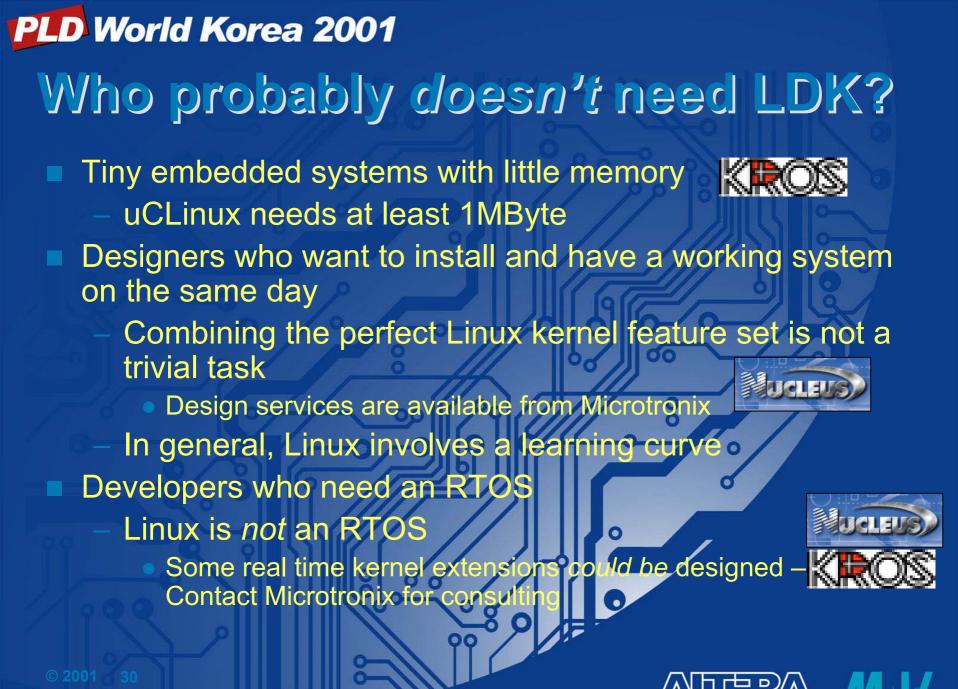

## uCLinux ("You See Linux") Derivative of the Linux 2.0 kernel Developed for microcontrollers without Memory Management Units (MMUs) Offers the traditional benefits of Linux: Stability, built-in network capability, file system support, large community of Linux developers

Small memory footprint (...for a Linux system)

- **Runtime memory required for Kernel + Application**

- As low as 1 MByte

- Large compared to typical embedded applications, but small for Linux

- Internet-ready embedded OS

- Network protocols built in

- Open Source. No licensing fees Royalties.

PLD World Korea 2001 Microtronix

- Established design and consulting firm for software and hardware

- ACAP Partner

- Extensive experience in telecom hardware design and embedded Linux

- Provide in depth support and consulting

- Device driver development

- PLD design, specializing in Altera

- Embedded Linux development

- Kernel level development

- Application design and development

Offer flexible support program

Real-time embedded support Telephony voice and data Analog and Digital expertise Legacy systems integration VOIP convergence, XDSL, Sonet

## What do you get in the LDK box?

Memory Expansion Board

crotromb

Getting Started Guide

- uCLinux kernel source code

- Three daughter boards to enable Linux development on NDK board

- Memory Expansion: SDRAM & flash

- **OS Support**: Real-time Clock & IDE interface (IDE interface support coming soon)

- Ethernet Connectivity: Same card as NEDK daughter card with CS8900A & RJ-45

- Serial Y-cable for debug

- **NOTE:** LDK *Requires* NDK dev board as base platform!

- Software & reference application

- Web server

- Linux command shell

- uCLibC & Kernel open source

- Hardware reference design

Linux works out of the box, r

2001 Quartus compile necessary

System-On-a-Programmable-Chip Solutions

Icrotronb

Linux Development Kit

#### PLD World Korea 2001 Potential LDK Customers Embedded Linux system developers Customers creating network-enabled products Customers who traditionally use a home-grown OS They probably *don't* want to keep supporting a proprietary OS They're used to having access to source code Won't get it with VxWorks or other closed-source OS They're used to bugs being fixed immediately "Penny pinchers" VxWorks is expensive stuff No Royalties for Linux Mention Nios & uCLinux to anyone who asks "We can do Linux" is a strong va Nios platform Not everyone needs to do Linux, everyone wants to know you can System-On-a-Programmable-Chip Solutions

PLD World Korea 2001

Ordering Information

NIOS-LINUX-KIT

\$2,495

Shipping NOW

00

╘श∕े∖

# Support

#### Altera Applications

- Apps is the front line of support for LDK

- Apps will provide install & basic "getting started" support

- Altera supports LDK to the point a user gets a Linux prompt

- Support for Altera devices

#### Microtronix

- 30 days install support

- Go through Altera Applications first. May be referred to Microtronix.

- Microtronix supports Linux design & development

\$4750 for 12 months of Standard Support

\$4000 if purchase within 30 days of LDK

Unlimited email support, next business day response

Six phone support incidents, next business day response

GNUPro Support

Upgrade Subscription – Linux and driver upgrades/patches

2001 Other support options available

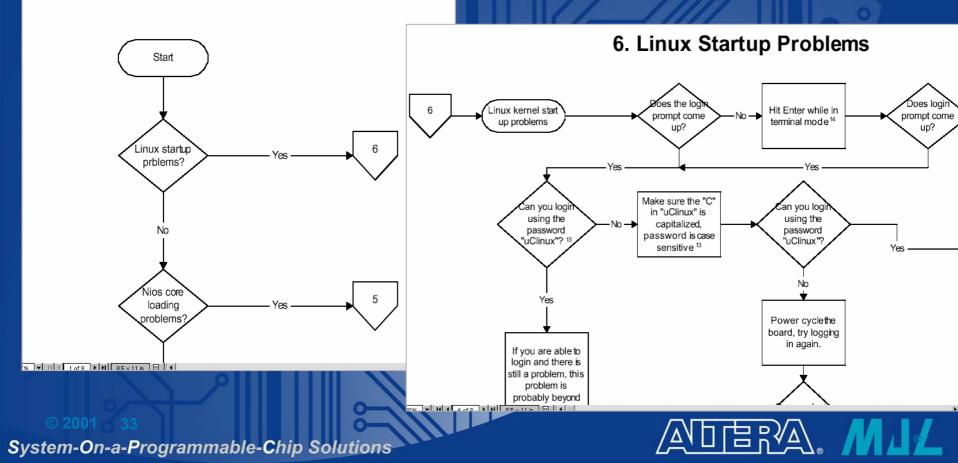

# PLD World Korea 2001 Support Flow

There is a detailed support flow to guide Apps Engineers to a proper solution, or to pass customer on to Microtronix

#### **Diagnose Problem Category**

# PLD World Korea 2001 uCLinux / Linux Resources

#### www.linuxdevices.com

- Up-to-date, embedded-focused Linux info

- www.uclinux.org

- Official uCLinux homepage, but a little out-of-date

#### www.oreilly.com

Offers a full range of Linux-related books

Embedded Linux by John Lombardo - Good intro to

embedded Linux issues for beginners

"Three reasons why Linux will trounce the embedded market"

Article released on IBM developerWorks web

http://www-106.ibm.com/developervoics/Impx/lip

Embedded Linux

html?dwzone=linux

## PLD World Korea 2001 Simple OS Comparison

|                        | ATI Nucleus                                                              | uCLinux                                                                                                               | KROS                                                      |

|------------------------|--------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|

| Price                  | \$12,000 for Basic<br>OS; Accessories<br>(networking, etc)<br>cost more. | \$2,495 for LDK & source                                                                                              | \$5,000                                                   |

| Business<br>Model      | Per-product license<br>fee. Source code.<br>No royalties.                | Open source. No royalties. Cost<br>of LDK is not for the OS. Linux<br>profit model is based on service &<br>support.  | Per-product license<br>fee. Source code.<br>No royalties. |

| Real Time              | Yes                                                                      | No                                                                                                                    | Yes                                                       |

| Memory<br>Requirements | 20 KB and up                                                             | 1 MB and up                                                                                                           | 7 KB and up                                               |

| Support                | Accelerated<br>Technology Inc                                            | Altera for install support only.<br>Microtronix or 3rd party Linux<br>Consulting for Linux design &<br>devel support. | Shugyo Design<br>Technologies                             |

|                        |                                                                          |                                                                                                                       |                                                           |

## Glossary

#### <u>MMU</u> – Memory Management Unit

- A hardware block in complex microprocessors. Helps the CPU manage complex memory addressing schemes (Mapping virtual memory addresses to physical addresses)

- Enables multiple programs to execute at the same time, and protects against illegal memory accesses. Especially helpful in OS-based systems.

- Nios doesn't have an MMU. uCLinux is developed for MMU-less architectures.

#### **<u>RTOS</u>** – Real Time Operating System

- An operating system that can process "mission critical" tasks within a guaranteed maximum turn around time. (VxWorks)

- Ex application: Car braking system, or industrial machinery motor control

#### Kernel – "Linux kernel"

- The lowest level software that runs on a processor. Interfaces directly with the hardware. Implementation is hardware dependent.

- Provides a consistent, platform-independent interface to higher-level software

- Ex: The application programmer doesn't have to think about how to operate a display device, a file system, or a network interface. They just work, thanks to the OS kernel.

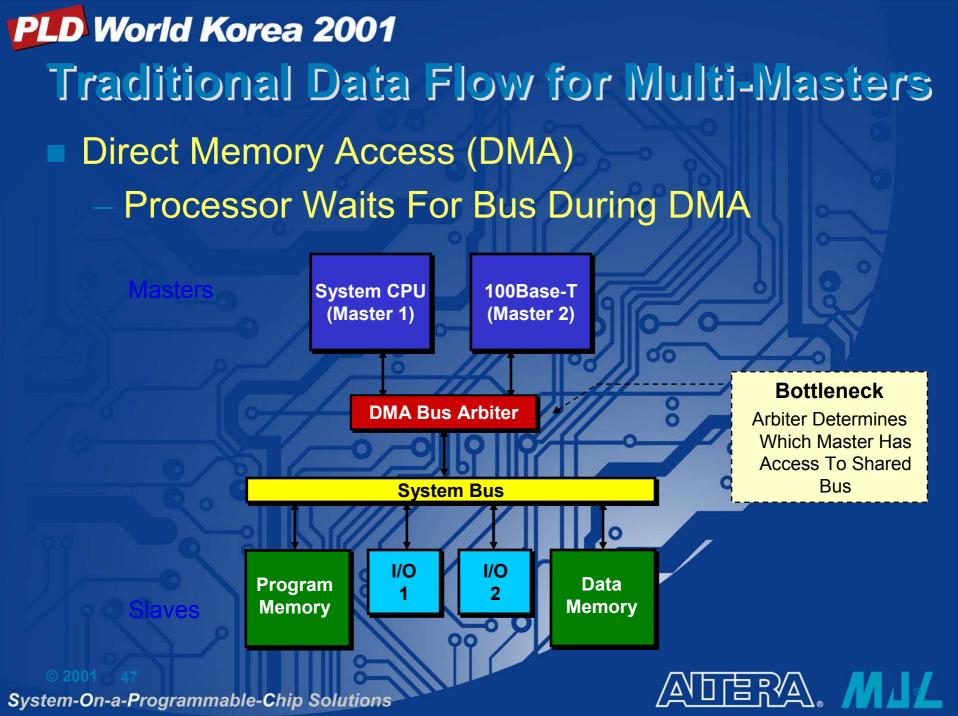

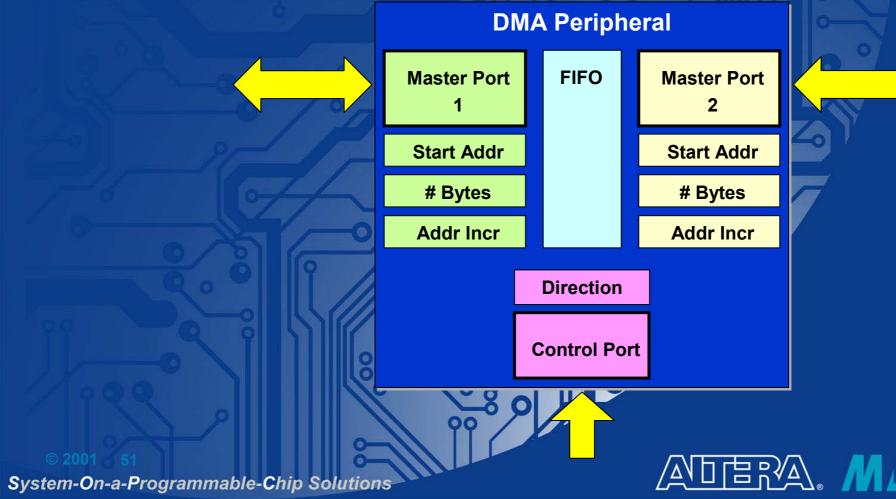

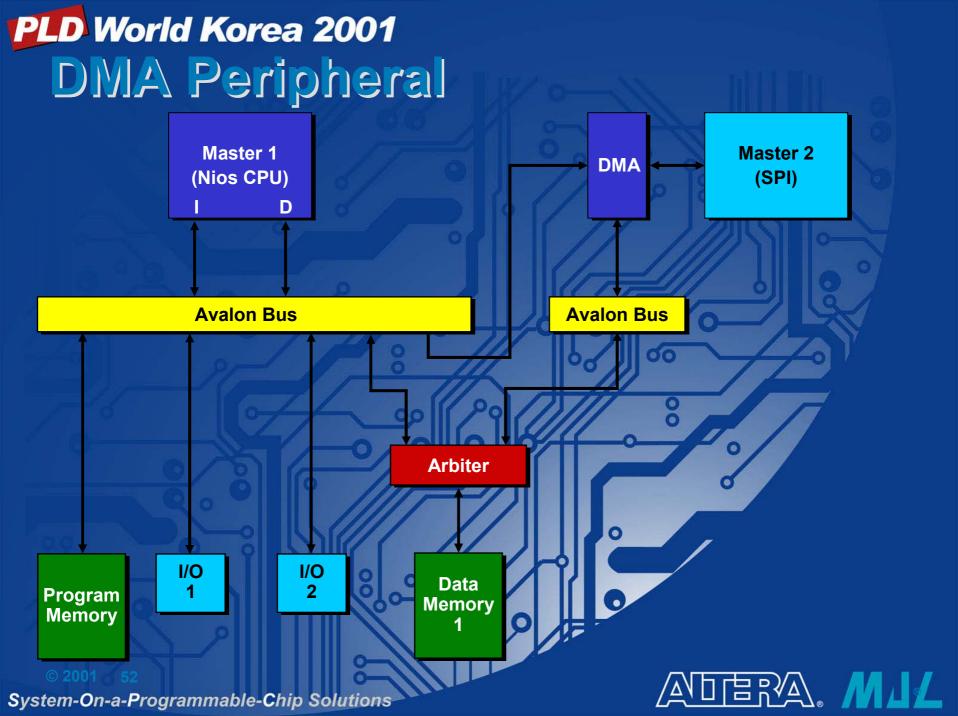

#### **DMA** – Direct Memory Access

Specialized circuitry or a dedicated microprocessor that transfers data from memory to memory (or from memory to a peripheral) without using the CPU. DMA may periodically "steal" cycles from the CPU, because both the CPU and the DMA cannot access the evolution bus at the same time. However, data is transferred much faster than using the CPU for every byte of transfer.

#### <u>Nios</u> –

Nios is not an acronym. Gotchal.

© 2001 30

## **Nios 2.0**

PLD World Korea 2001 Nios 2.0**Optimized Data Processing Custom CPU Instructions** >2X Acceleration (e.g. MAC, MP3, Bit Swap) **Optimized Data Flow** Simultaneous Multi-master Bus Capability **Gbps Throughput On-chip Debug & Hardware Trace** Smaller, Faster Nios CPU All existing Nios customers will get Nos 2 "Thank you" to our Nios ear 01 Vios For all users present and futu voar subscription starts from Nios Please

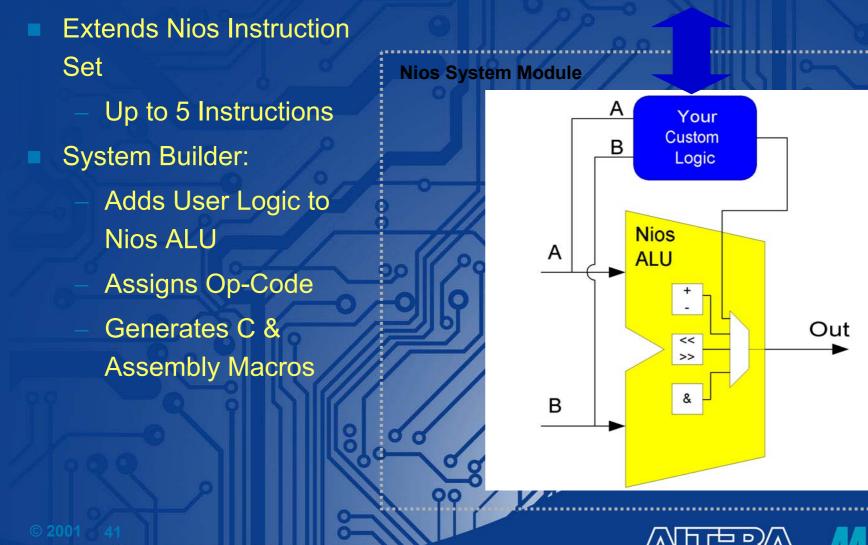

# **Custom Instructions**

**Optimized Data Processing**

© 2001

PLD World Korea 2001 **Custom Instructions Custom Instructions Augment Nios Instruction Set** Integrated Into Nios Development Tools System Builder Design Tool Handles Op-code Assignment Generates C and Assembly-language Macros **Application Examples** 0 Data Stream Processing (E.G. Network Applications) **Application Specific Processing** MP3 Audio Decode) Software Inner Loop Optimization

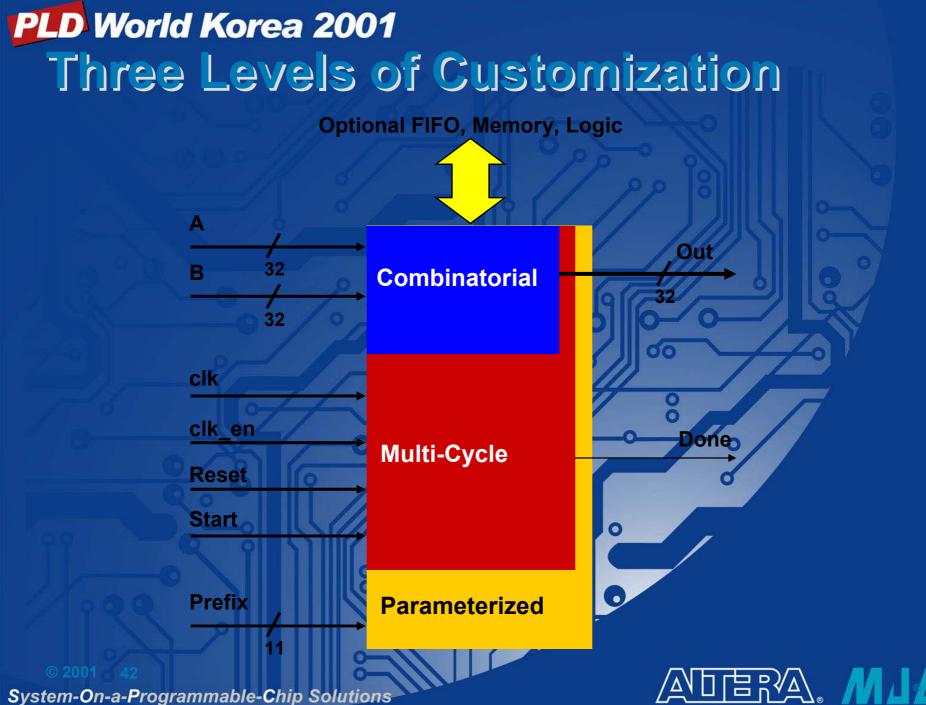

## PLD World Korea 2001 Custom Instruction Block Diagram

#### **Optional FIFO, Memory, Other Logic**

#### PLD World Korea 2001 **Real Custom Instruction Examples** MP3 Audio Decode Nios MP3 reference application implemented a crucial MP3 multiply-shift function in Custom Instruction Enabled real-time MP3 decode at 33MHz Achieved >2x increase in actual performance at 33MHz **Endian Conversion** Swaps byte order in 32-bit word [DD CC BB AA] to [AA BB CC DD] 0 Commonly required when transferring data between systems 1 cycle using custom instruction, 20-40 cycles using normal RISC instructions Custom instruction can dramatically increase system Custom instruction always performance, regardless reduces code size of Fmax

# Simultaneous Multi-Master Bus

**Optimizing Data Flow**

© 2001

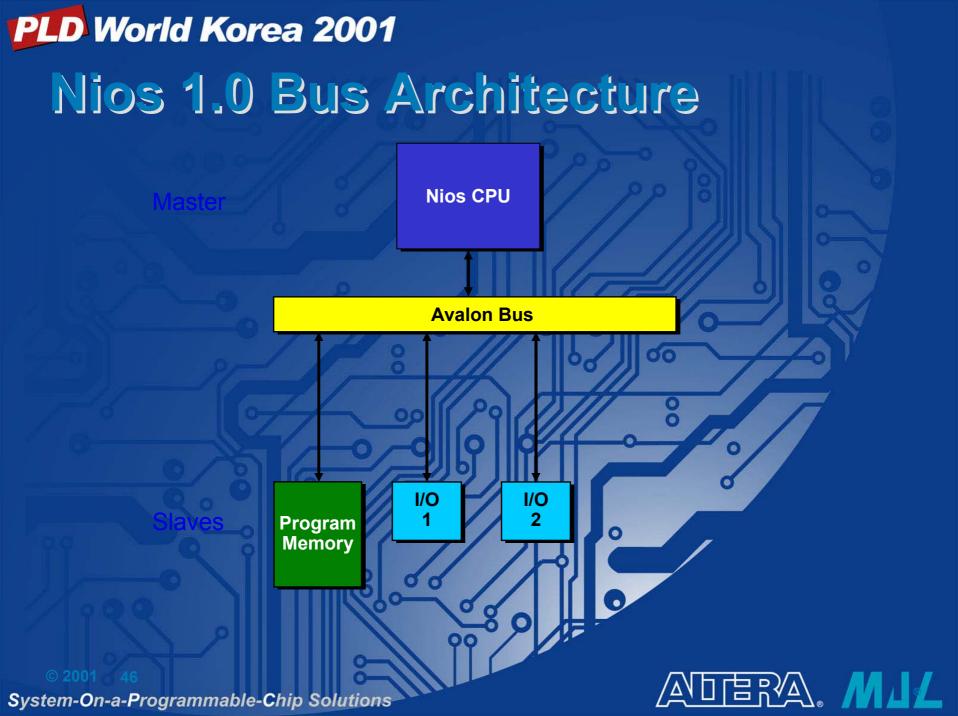

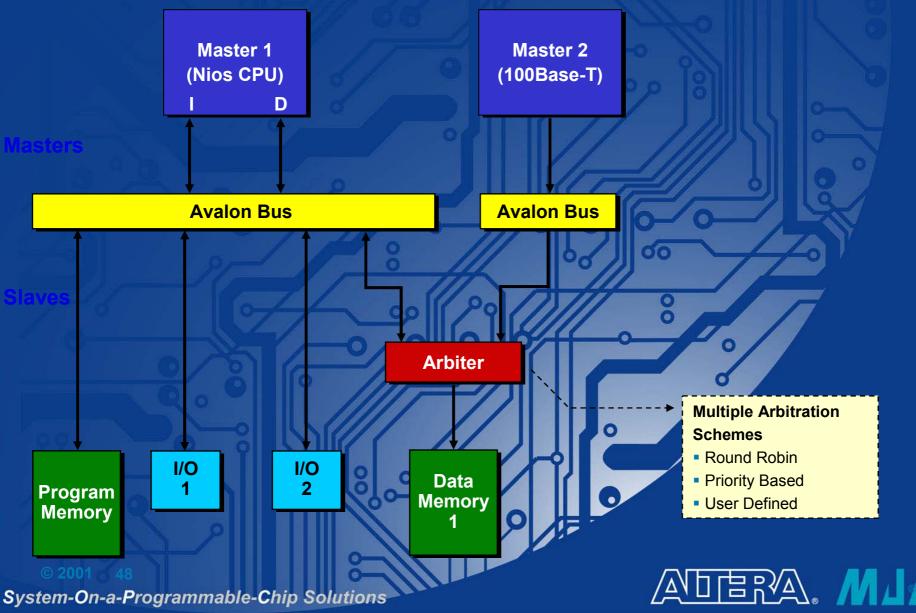

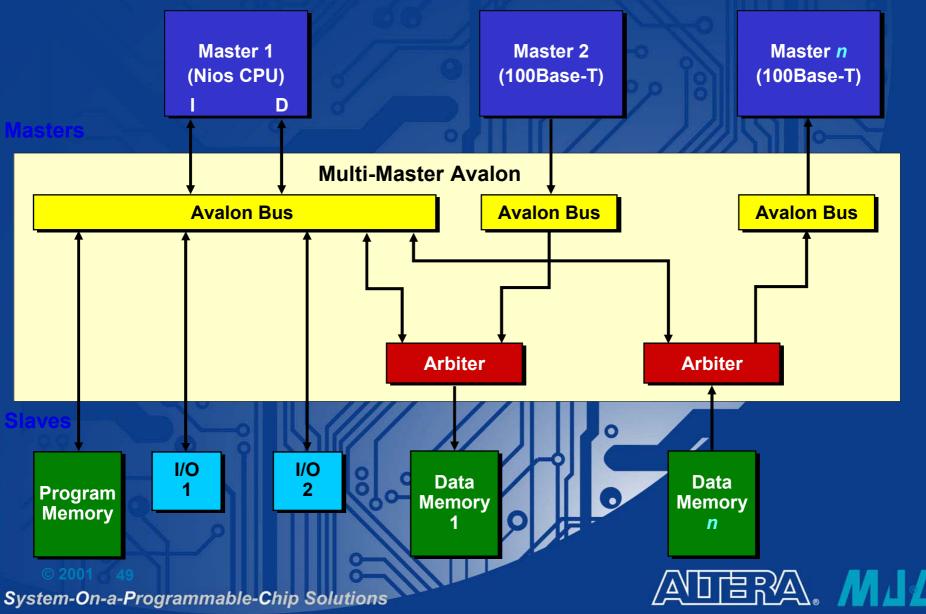

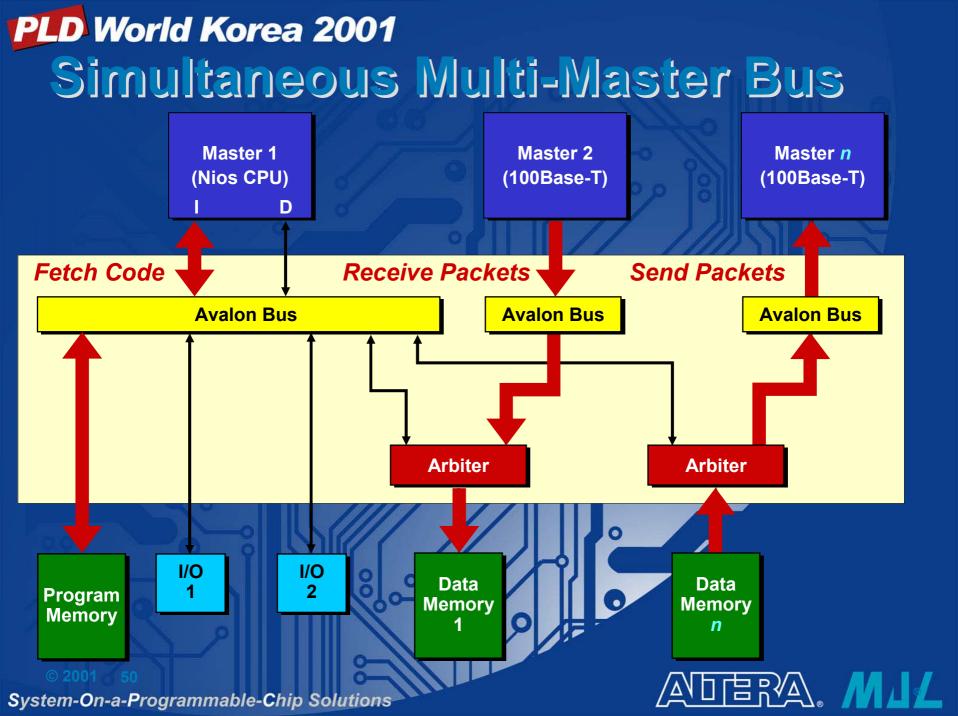

#### PLD World Korea 2001 Simultaneous Multi-Master Bus Allows multiple masters on a single Avalon bus "Unlimited" Number of Bus Masters Masters can be active simultaneously as long as they don't access the same slave - "Slave side arbitration" Only possible in PLD processors! "DMA on Steroids" Simultaneous CPU & DMA Operation 0 New DMA Peripheral Converts Slaves To Masters **High-Performance Data Flow** Peripherals Get Direct Access to **Nios Performs Traffic Management** Easy to Build System Builder Generates Multi-Master Bus

## PLD World Korea 2001 Simultaneous Multi-Master Avalon Bus

## PLD World Korea 2001 Simultaneous Multi-Master Bus

# PLD World Korea 2001 DMA Peripheral Provide Bus Master Capability to Any Nios Peripheral

PLD World Korea 2001 System Builder Tool **Automatically Configures System** Processor Peripherals Memory System Bus Witch Components 🗄 🕨 Bridges **Builds Custom Bus** Avalor 🗄 - 🕨 Peripherals Master / Slave **Arbitration Priorities** AHB **Unlimited Number** 🗄 - 🕨 Perinherals of Bus Masters Add **Generates System VHDL** or Verilog

- 🗆 × Modules Global Settings System Generation You have created an Avalon bus. System clock is 33330000 Hz 👰 Avalon Tristate Bus ext ram hus Altera Nios(TM) CPU 🦓 Base Addre ... End Address IR Description 🚇 On-Chip Memory () 1 nios1 Altera Nios(TM) CPU PIO (Parallel I/O) 2 hoot rom On-Chip Memory (RAM or ROM  $0 \times 200$ Interval timer UART (RS-232 serial port) 3 uart HART (RS-232 ser Interval timer Dx11010 4 time 11 5 ext ram 32-bit SRAM (256Kbytes in two IDT71V016 chips) 0x200 0x10200 N/A 6\_hit Elesh (1Mhy 6 pio PIO (Parallel I/O) 16-bit Flash (16Kbv 7 ext\_ram\_bus Avalon Tristate Bus 16-bit SRAM (32Kb On-Chip Memory (RAM or ROM) bx30100 8 onchip ram N/A 32-bit SRAM (256K 9 firewire co User-Defined Interface <30100 Altera Nios(TM) CPU 🔏 Altera ARM CPU Rename Delete Edit.. Generate Cancel < Prev Next >

PLD World Korea 2001 Price & Availability Price: All Nios Users Get Upgrade at No Cost Nios 2.0 Features Included in \$995 Kit Availability: Alpha (to FAEs) - October 2 **Beta (to Limited Customers** November 21 Upgrade Posted on FTP te - December 6 S ber 17 Upgrade to Customers

© 2001

# **Competitive Comparison**

PLD World Korea 2001 **Microcontroller** Competition **Companies Now Using Nios Formerly Used Products Such as:** Motorola (68000, 683XX, MPC8XX, 68HCXX) Intel (i960, StrongARM) do Hitachi (SHX, HX) Philips (XA) Zilog (Z80) Many (8051)

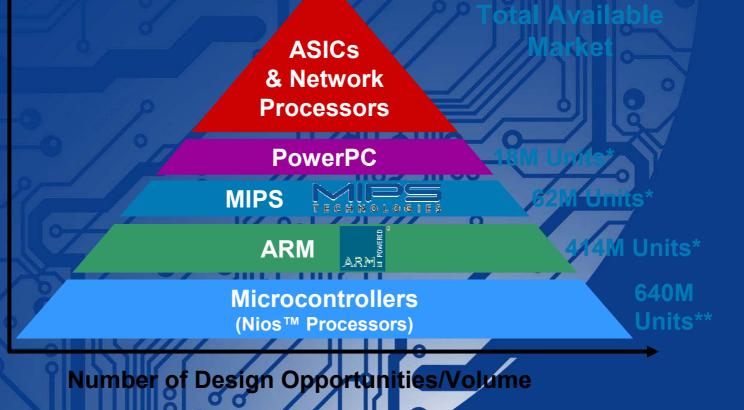

# PLD World Korea 2001 Embedded Market Overview

Performance

\*2000 Shipments, Microprocessor Report \*\*2000 16-Bit & 32-Bit MCU Shipments, Instat

System-On-a-Programmable-Chip Solutions

A sumates 30M to 40Mu of Year 2000 shipments will be in networking / telecom applications

PLD World Korea 2001 Microcontroller Market Drivers

> Microcontrollers (Nios™ Processors)

In rank order \*

Software Development Tools

Price

Available I/O (Peripherals)

Speed

\* 2000 Embedded Systems Programming Subscriber Study

#### **PLD** World Korea 2001

## Microcontroller Landscape

|                    | 32-Bit Microcontrollers |                |               |                   |                    |                         |  |  |  |  |  |

|--------------------|-------------------------|----------------|---------------|-------------------|--------------------|-------------------------|--|--|--|--|--|

|                    | Nios -32                | Hitachi<br>SHX | Intel<br>i960 | Motorola<br>683XX | Motorola<br>M-CORE | Motorola<br>PowerPC 8XX |  |  |  |  |  |

|                    | \$4 - \$42              | \$25-\$100     | \$10-\$50     | \$5-\$100         | \$10-\$25          | \$50-\$100              |  |  |  |  |  |

| 32 Bit             | 33 to 80                | 60 to 200      | 10 to 100     | 33                | 10 to 33           | 40 to 80                |  |  |  |  |  |

| 7 <b>743</b> P.I.L |                         |                |               |                   | 5                  | 87 01 B                 |  |  |  |  |  |

|        | 16-Bit Microcontrollers |                |                    |                    |               |                       |  |  |  |  |  |  |

|--------|-------------------------|----------------|--------------------|--------------------|---------------|-----------------------|--|--|--|--|--|--|

| 2),    | Nios -16                | Hitachi<br>H8S | Motorola<br>68HC12 | Motorola<br>68HC16 | Philips<br>XA | Siemens<br>80C166/167 |  |  |  |  |  |  |

| 16 D:4 | \$4 - \$42              | \$10-\$25      | \$10-\$25          | \$5-\$50           | \$2.5-\$10    | \$2.5 to \$25         |  |  |  |  |  |  |

| 16 Bit | 33 to 80                | 20 to 25       | 8.5                | 16 to 25           | 33            | 26 to 25              |  |  |  |  |  |  |

|       |            | 8-Bit Microcontrollers |                     |                     |                    |                        |  |  |  |  |  |  |  |

|-------|------------|------------------------|---------------------|---------------------|--------------------|------------------------|--|--|--|--|--|--|--|

| 8 Bit | Nios -16   | Hitachi<br>H8          | Microchip<br>PIC 16 | Microchip<br>PIC 17 | Motorola<br>68HC11 | Philips<br>80XX, 80CXX |  |  |  |  |  |  |  |

|       | \$4 - \$42 | \$5-\$10               | \$1-\$5             | \$5-\$10            | \$2.5-\$10         | \$2.5-\$5              |  |  |  |  |  |  |  |

|       | 33 to 80   | 8 to 16                | 20                  | 33                  | 2 to 4             | 33                     |  |  |  |  |  |  |  |

## **PLD** World Korea 2001

S

## Microcontroller, Feature Set

|                                                    |                 | ¥ ' | 9 | 4   | $\mathbf{V}$ | $\mathbf{\nabla}^{-}$ | У            | <b>7</b> | Y ` | <b>y</b> ` | 1  | Y I | <b>Y</b> | y          | Y  | $\mathbf{Y}_{-}$ | <b>7</b> ' | y . | <b>Y</b> | Y Y | 1              | У  | <b>Y</b> | $\checkmark$ | Y | Y | ×.  | 4  | Y   |        |

|----------------------------------------------------|-----------------|-----|---|-----|--------------|-----------------------|--------------|----------|-----|------------|----|-----|----------|------------|----|------------------|------------|-----|----------|-----|----------------|----|----------|--------------|---|---|-----|----|-----|--------|

| Nios                                               | 32              | √   | √ | 1   | 1            | √                     | √            | 1        |     | V 1        | V  | N   | V        | V          | V  | V                | V          | √   | 1        | 1   | √ <sup>0</sup> | √  | 1        | 1            | / | ~ | V   | 1  | 1   | 7      |

| Hitachi SHX                                        | 32<br>√         | 1   | √ | 1   | 1            | 1                     | V            | V        | 1   | N          | C  | ĥ   |          |            |    | 1                | V          |     |          | V   |                | V  | K        |              |   | ~ | V   | V  | 1   | 1      |

| Intel 1960                                         | 32              | V   | √ | 1   | 1            | 1                     |              | 1        |     |            |    |     |          | V          |    | 1                | 6          |     |          | V   |                |    | 0        |              |   |   |     | V  | V   |        |

| Motorola 683XX                                     | _ <sup>32</sup> | V   | √ | 1   | V            | 1                     | 1            | 1        |     | N          | 0- |     |          | V          | 10 | V                | 0          |     |          |     | 0              | V  | 1        |              |   | ~ |     | V  | V   | 1      |

| Motorola M-Core                                    | 32<br>√         |     | 1 | 1   | √            |                       | V            | 1        | 000 | V          | _  |     | Z        | 1          |    | 6                | J          |     |          |     |                |    | X        | X            | Æ | 1 |     | V  | 1   | 1      |

| Motorola PPC                                       | 32              | V   | √ | 1   | 1            | 1                     | V            | 1        | Ó   | 0          |    | 5   | 90       | 1          | 2  | V                | N          |     |          | 1   |                | V  |          |              |   | 1 | 1   | 1  | 1   |        |

| Hitachi H8S                                        | 16              | √   |   |     | 1            | 1                     |              |          |     | 0          |    | Ģ   | X        | <b>√</b> ¢ | 1  | ff               | 1          |     |          |     |                | 6  | Y        |              |   |   | N   | V  |     | V      |

| Motorola 68HC12                                    | 16              |     | V |     | √            | $\checkmark$          | √            | 1        |     |            |    | 2   | 1        | IJ         |    |                  | 1          |     |          |     |                | 0  | V        |              |   | V |     | V  | V   | V      |

| Motorola 68HC16                                    | 16              |     | √ |     | V            | √                     | $\checkmark$ | 1        | /   | V          |    |     |          | 1          |    |                  | N          |     |          |     |                |    | V        | ,            | - | 1 | 1   | 1  | 1   | -<br>V |

| Philips XA                                         | 16              | 1   | 1 | 1   | 1            | 1                     | $\checkmark$ | 1        |     |            |    |     |          |            |    | þ                | <b>v</b> ( |     |          |     | /              |    |          | 1            |   |   |     | V  | V   | 1      |

| Siemens 80C166                                     | 16              |     |   |     |              |                       | 1            | 1        | 07  | V          | 1  | 0   | Ø        | 6          |    |                  | ۲ (        |     |          |     |                |    | √        |              | 1 |   | 7   | 1  | √ . | √ ,    |

| 0                                                  |                 | P   | N | ler | nc           | ory                   | IF           |          |     |            | S  | P   | iął      | 1/0        | 0  | 1.               | F          | Pa  | ral      | lel | Ċ              | Sp | ec       | cia          |   | - | Tir | ne | ers |        |

| © 2001 60<br>stem-On-a-Programmable-Chip Solutions |                 |     |   |     |              |                       |              |          |     |            |    |     |          |            |    |                  |            |     |          |     |                |    |          |              |   |   |     |    |     |        |

## PLD World Korea 2001 Configurable Processor Comparison

ARC and Tensilica

Svstem-O

- Processors Optimized for ASIC Implementation

- Very Large and Slow When Implemented in PLDs

do

Nios Is Optimized for Use in Altera PLDs

Nios Is 2.5X to 7X Smaller

|                            | ARC Core<br>w/2KB I-cache<br>Altera EP20K400E | Tensilica core<br>w/cache/RAM/ROM<br>Altera EP20K400E | • Nios core<br>32-bit version<br>Altera EP20K400E |

|----------------------------|-----------------------------------------------|-------------------------------------------------------|---------------------------------------------------|

| Logic Elements (LE's)      | 3,400                                         | 9,000                                                 | 1,250                                             |

| % of Device                | 20%                                           | 54%                                                   | 7.6%                                              |

| ESB's/RAM                  | 26Kb                                          | 37Kb                                                  | -                                                 |

| Typ. Freq.                 | 35 MHz                                        | 40 MHz                                                | 42 MHz                                            |

|                            | 00000                                         | 80 1= 0                                               |                                                   |

| 61<br>n-a-Programmable-Chi | p Solutions                                   |                                                       |                                                   |

## PLD World Korea 2001 Other Competitive Soft Cores

## Leon 2

- Open source CPU

- Not PLD friendly

- No Megawizards

- Who supports it?

- Patent Issues?

- Based on Sun SPARC

- Info:

- www.gaisler.com/leon.html

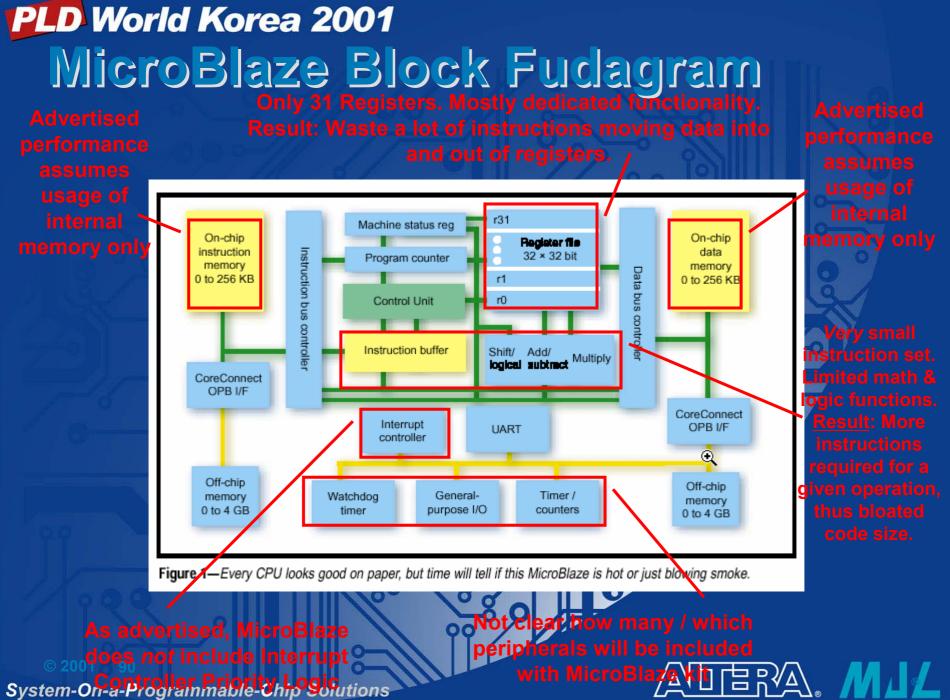

MicroBlaze – Xilinx – Beta Release

System-On-a-Programmable-Chip Solutions

| Technology               | Area     |

|--------------------------|----------|

| UMC 0.25 CMOS std-cell   | 35K gate |

| Atmel 0.25 CMOS std-cell | 33K gate |

| Atmel 0.35 CMOS std-cell | 2 mm2 +  |

| Xilinx XCV300E-8         | 4,800 LU |

| Xilinx XCV800-6          | 4,800 LU |

| Altera 20K200C-7         | 5,700 LC |

| Altera 20K200E-1X        | 6,700 LC |

|                | Timing              |

|----------------|---------------------|

| + RAM          | 130 MHz (pre-layout |

| + RAM          | 140 MHz (pre-layout |

| RAM            | 65 MHz (pre-layout, |

| + block RAM    | 45 MHz (post-layout |

| + block RAM    | 35 MHz (post-layout |

| ELLS + EAB RAM | 49 MHz (post-layout |

| LLs + ESB RAM  | 37 MHz (post-layou  |

0

log file

log file

log file

log file

log1, log2

PLD World Korea 2001 Example Design – A Typical CPU

## PLD World Korea 2001 Example Design - Peripherals

| Peripheral    | Configuration                   |

|---------------|---------------------------------|

| LCD           | PIO: 11-Bit Output              |

| LED           | PIO: 2-Bit Bi-Directional       |

| 7-Segment LED | PIO: 16-Bit Output              |

| Buttons       | PIO: 12-Bit Input               |

| Timer         | 32-Bit                          |

| UART          | Fixed Baud 115200               |

| Memory        | 32-Bit / 16-Bit SRAM (256K/32K) |

| Memory 8      | 16-Bit Flash (1MB / 16K)        |

| On-Chip ROM   | 1K with Boot Monitor            |

## PLD World Korea 2001 Example Design – Size / Speed

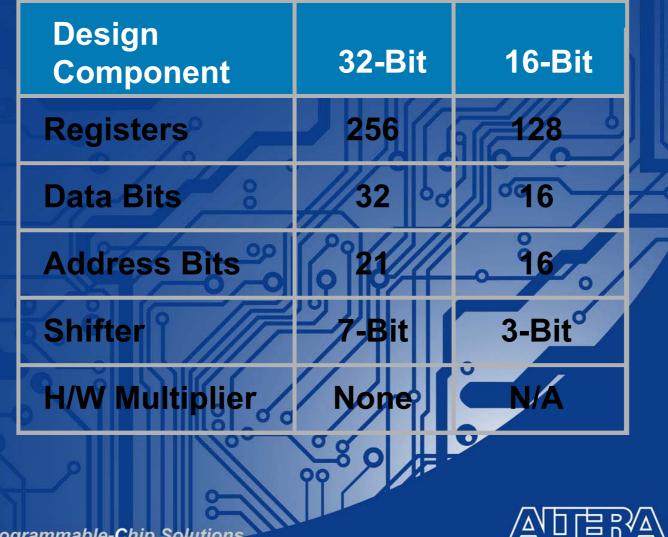

| Dovice Femily   | 32-    | Bit   | 16-Bit      |       |  |  |  |  |  |  |

|-----------------|--------|-------|-------------|-------|--|--|--|--|--|--|

| Device Family   | LE     | Fmax  | LE          | Fmax  |  |  |  |  |  |  |

| Mercury         | 2602   | 59.08 | 1784        | 70.51 |  |  |  |  |  |  |

| APEX II         | 3046   | 55.44 | 2144        | 59.34 |  |  |  |  |  |  |

| APEX 20KC       | 302200 | 53.15 | 2124        | 54.09 |  |  |  |  |  |  |

| APEX 20KE<br>XA | 3035   | 43.26 | 2151        | 44.50 |  |  |  |  |  |  |

| FLEX 10KE       | 3029   | 32.47 | <b>2103</b> | 38.82 |  |  |  |  |  |  |

| ACEX 1K         | 3042   | 31.35 | 2119        | 38.31 |  |  |  |  |  |  |

### PLD World Korea 2001

# xniliX - noititeqmo2 ero2-tito2

#### Nios

- 16-Bit Instruction Set

- Small Code Size

- Uses Popular 16-Bit Flash

Device Support

ACEX & FLEX 10KE

APEX, APEX 20KC, APEX II

- Mercury

- Excalibur ARM

ASIC License Available

System-On-a-Programmable-Chip Solutions

**MicroBlaze** 32-Bit Instruction Set Large Code Size **Requires two 16-Bit Flash** Devices **Device Support** √irtex-E, Virtex-II **Spartan-II** Joense?

#### PLD World Korea 2001

#### Soft-Core Competition - Xillinx Nios

Windowed Register File

Configurable to 512 Registers

Fast Context Switching

Interrupts

Integrated Controller

64 Vectored Interrupts

Peripherals:

UART SPI Ethernet Timer PWM PIO IDE User-I SRAM SDRA Flash Comp

PIO User-Defined SDRAM Compact Flash

System-On-a-Programmable-CDD Solutions

32 Registers

Stack Overhead for

Subroutine Calls

Interrupts External Add-On Peripheral Peripherals: UART Timer/Counter PIO Arbiter Flash, SRAM Interrupt Controller

## PLD World Korea 2001 Soft-Core Competition - Xilinx

#### Nios

- Customization Instruction

- Up to 5 Per Processor

- Combinatorial

- Sequential

- Parameterized

- Supports External Interface

- FIFO, Memory

- External Logic

- **Generates Software**

- Assembly Macro

- C Macro

System-On-a-Programmable-Chip Solutions

#### **MicroBlaze**

None

**Custom Instruction**

# PLD World Korea 2001 Soft-Core Competition - Xilinx

#### Nios

- Development Kit

- Complete Kit (\$995)

- Processor & Peripherals

- Development Board

- Compiler, Assembler

- Debugger

- Quartus II Limited Edition

- Download Cable

- Documentation

- Reference Designs

- Tutorial

System-On-a-Programmable-Chip Solutions

#### **MicroBlaze**

Development Kit Kit 1 (\$495) Processor & Peripherals Compiler, Assembler Debugger

> 2 (\$?) Processor & Peripherals Compiler, Assembler Debagger Levelopment Board Xilinx ISE

### PLD World Korea 2001

# xniliX - noititeqmo2 ero2-tito2

#### Nios

- Operating System Support

- ATI Nucleus

- Linux

- KROS

- Software IDE

- Viosoft Arriba!

- Edit

- Compile

- Download

- Run

- Debug

- Hardware Breakpoints

- Software Trace

System-On-a-Programmable-Chip Solutions

MicroBlaze

Operating System Support

None

Software IDE

PLD World Korea 2001 Customer Feedback - MicroBlaze **Competitive Situation** XA10 With Four 32-Bit Nios I/O Processors **Evaluating MicroBlaze**  Excited About 125MHz Spec **Customer Comments Disappointed in MicroBlaze Nios Has Better Complier Solution Realized Xilinx Speed C** ms Are Marketing Hype 125MHz Requires Internal Program Memory

## Nios is in 2<sup>nd</sup> generation, and **1 year** in the lead

- Xilinx MicroSmoke is just out of the starting gate (not even)

- Hardware alone does not a system make

- Peripherals, documentation & reference designs are crucial pieces of a microprocessor solution – And Altera has it

#### Custom instruction capability

- Even a mid-performance 32-bit Nios can be a processing powerhouse

- MIPS & Fmax become meaningless

- Nios now offers "advanced configurable processor" features

- Look out Arc and Tensilica

- And we can license for ASIC too

- Simultaneous Multi-Master Avalon Bu

- Even a mid-performance 32-bit Nios can be a Gbps throughput powerhouse

- MIPS & Fmax become meaningless

- Traditional PLD features (configurable routing) offer real advantages

© 2001 73 in embedding a processor in an SOPC

### PLD World Korea 2001 Summary Quartus II Limited Edition is shipping to all Nios customers PCI32 Nios Target ships in October 2001 Ethernet Development Kit is shipping today Linux Development Kit is shipping today Custom Instruction enables optimized data processing >2x performance and smaller code Simultaneous Multi-master enables optimized data flow Nios becomes a throughput powerhouse regardless of Fmax Nios' primary competition is standard microcontrollers Nios has a 1 year lead on MicroBlaze 3rd party software & tools moment eference applications, documentation, experience MicroBlaze is nothing but MicroSmoke until it releases Preliminary analysis suggests MicroBlaze will have no ficant advantage over Nios

## **Design Examples**

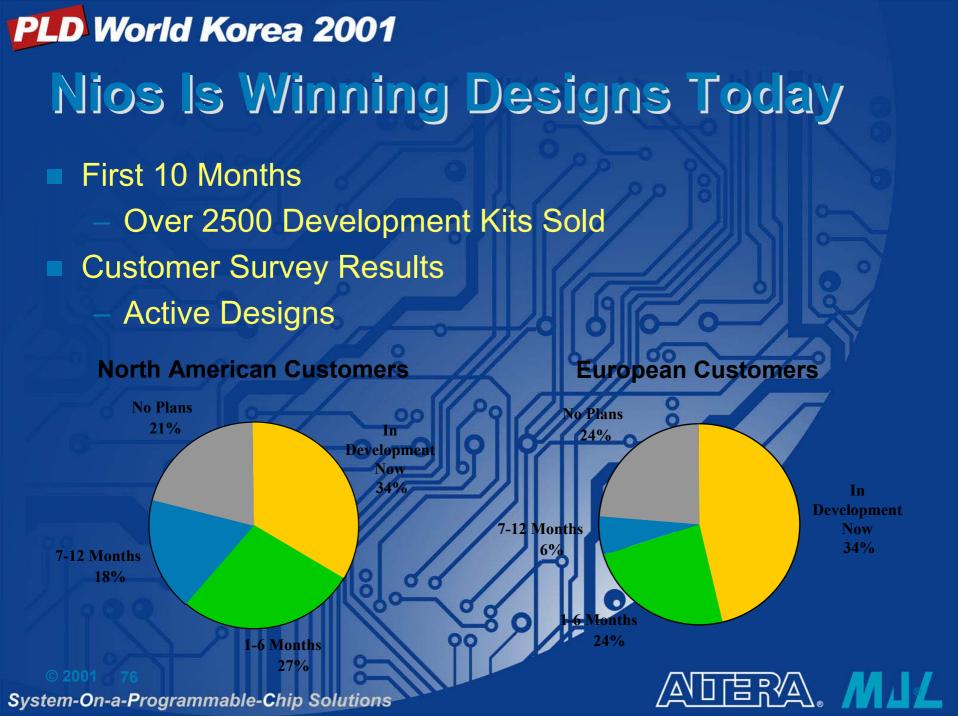

# Nios Kit Customers (Partial List)

Siemens

- Boeing

- Bosch

- Canon

- Casio

- **Cisco Systems**

- Eastman Kodak

- EMC

- Fujitsu

- **General Instrument**

- **Hewlett Packard**

- Hitachi

- IBM

- LM Ericsson

- Lucent Technologies SAS

- Matsushita

- Matsushita Communications

**Motorola Communications** NEC Nintendo Nokia Telecommunications Nortel Philips Research Philips Business Communications Philips Multimedia Rockwell Sanyo Sharr

& Communications Inform

## Why Customers Use Nios

- Technical Issues

- Easy to Implement Complex State-Machine

- Provide General Housekeeping/Management Functions

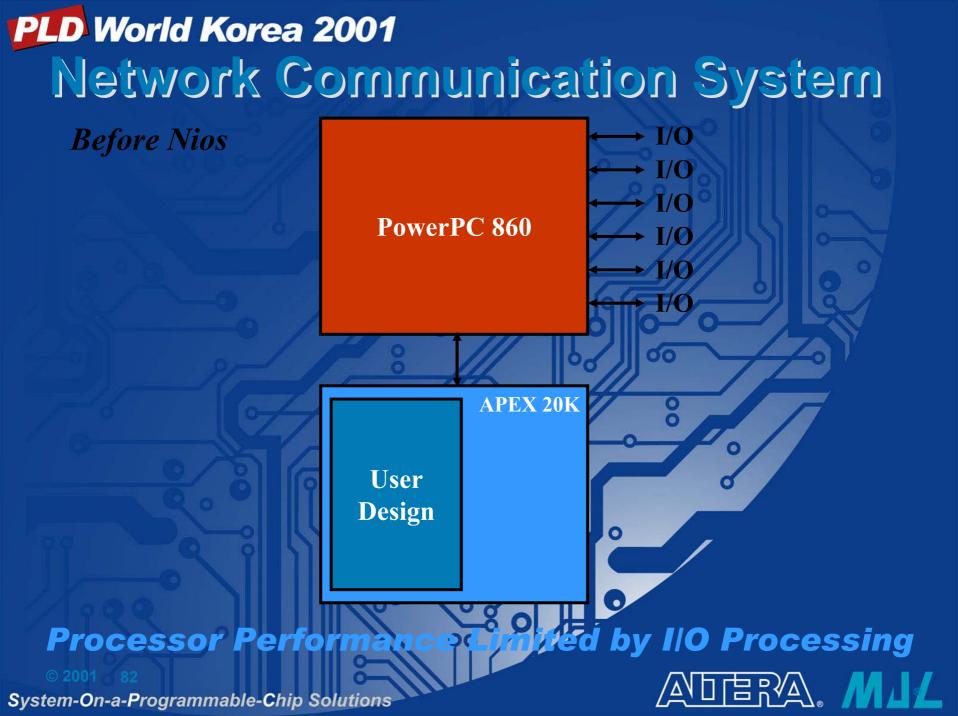

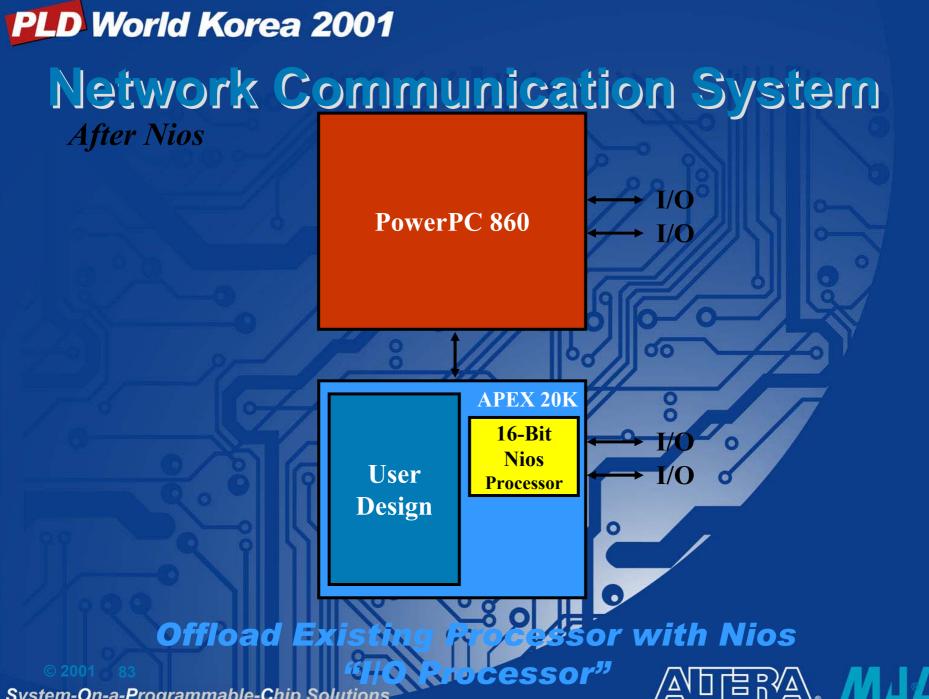

- I/O Processing

- Off-Load Existing Processor

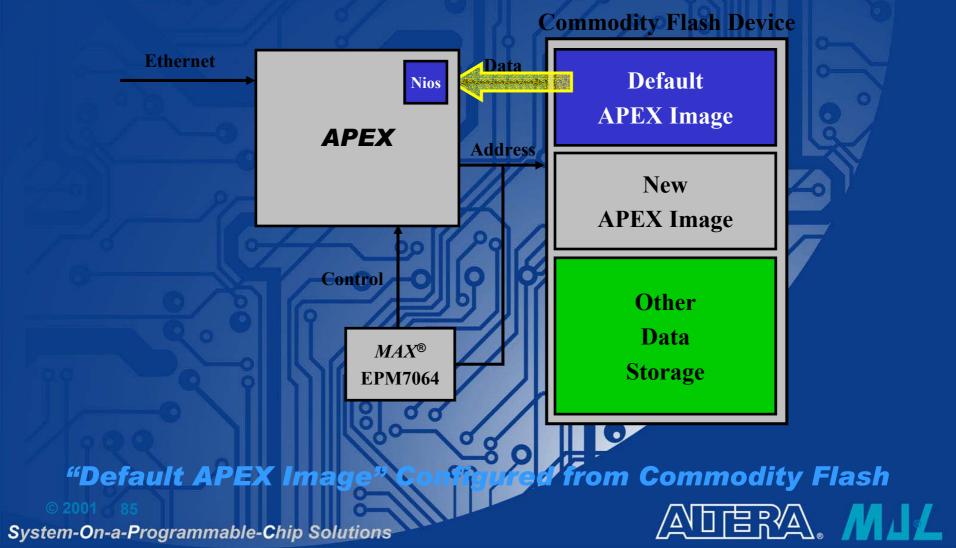

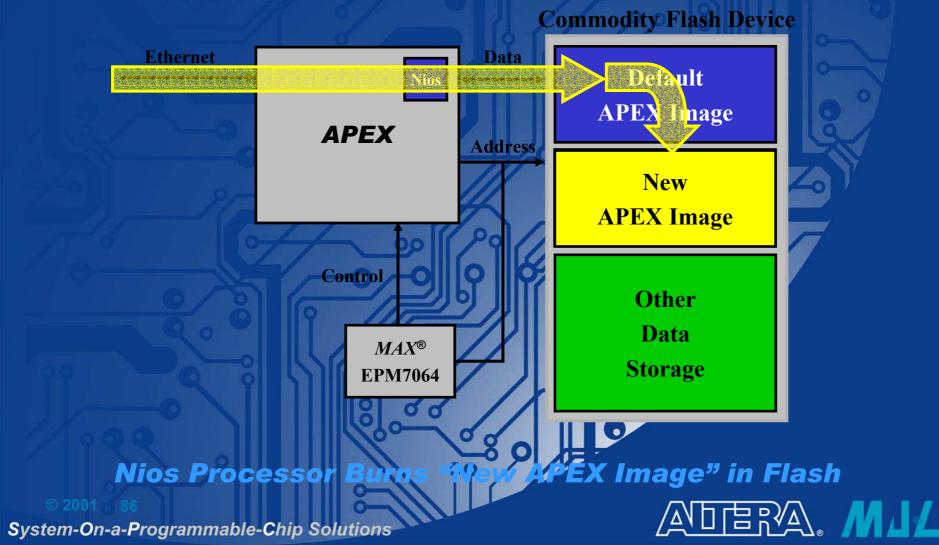

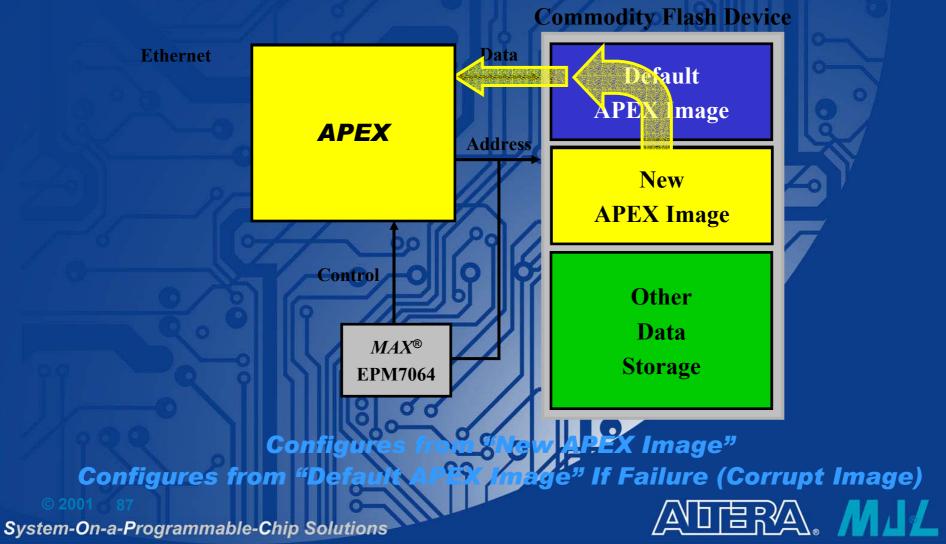

- Remote PLD Configuration (e.g. Internet Reconfiguration)

**Business Issues**

- Save Cost by Reducing System Chip Count (System-on-a-Programmable Chip)

- Allocation-Proof Processor

- Feature Upgrades Extend Product

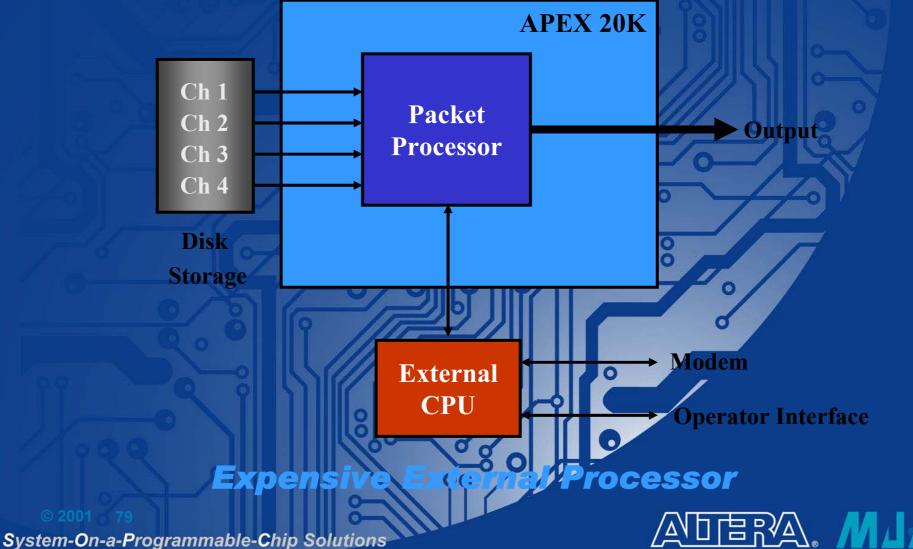

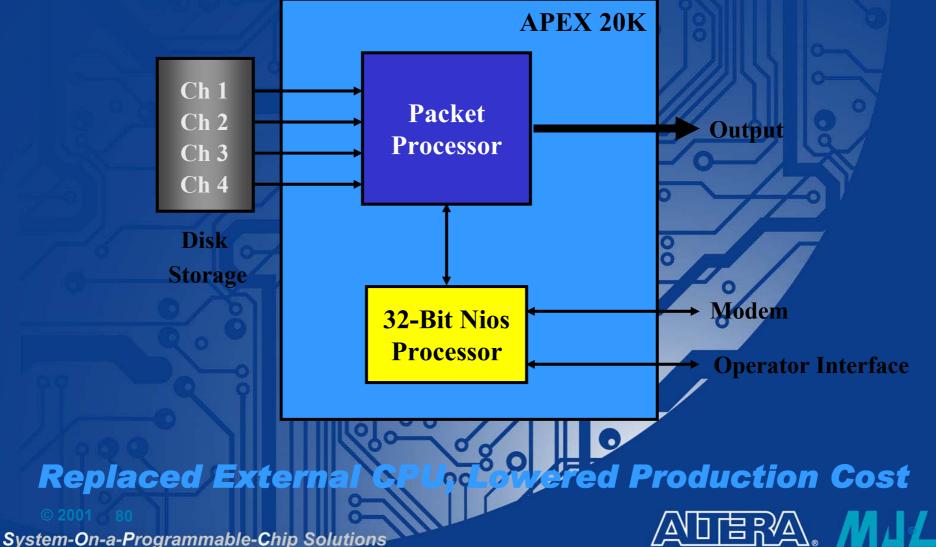

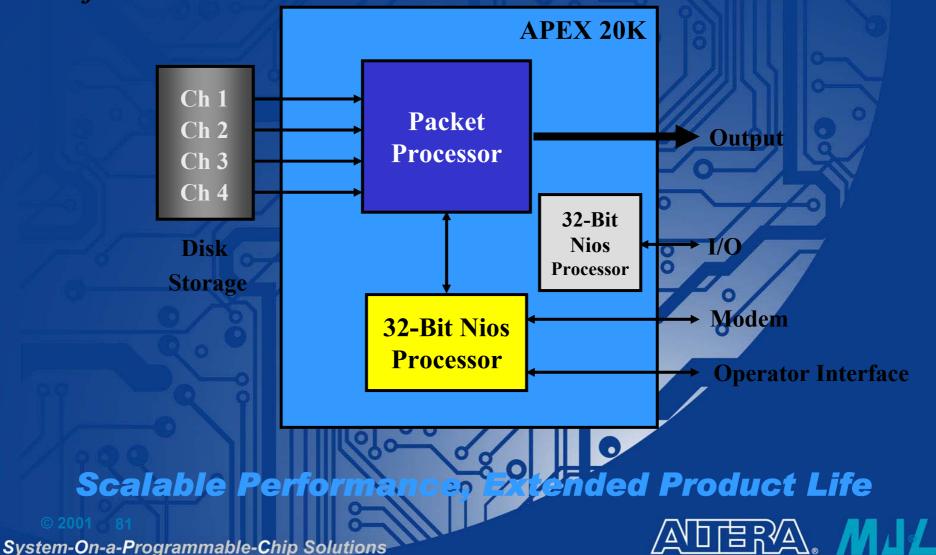

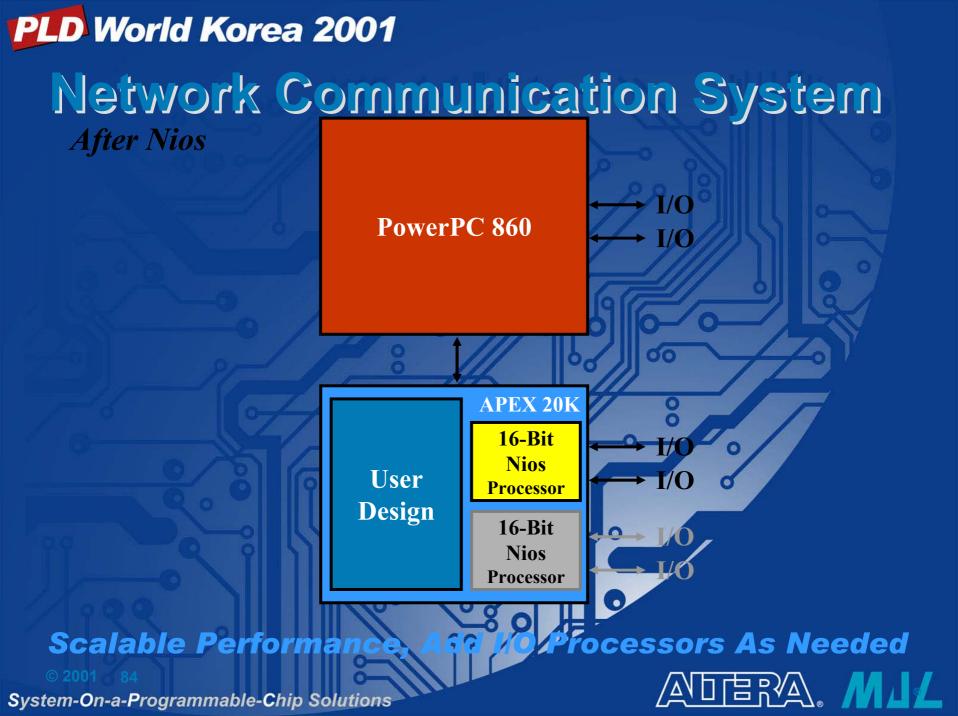

### PLD World Korea 2001 Commercial Entertainment System Before Nios

## PLD World Korea 2001 Commercial Entertainment System After Nios

### **Commercial Entertainment System** After Nios

### PLD World Korea 2001 Remote Reconfiguration On Power Up

### PLD World Korea 2001 Remote Reconfiguration Download New Configuration

### PLD World Korea 2001 Remote Reconfiguration Nios Initiated Reconfiguration

© 2001

## Early Look at Xilinx MicroBlaze

PLD World Korea 2001

Source Material

Xilinx Homepage

Not much help. No details (and no CPU!) available

Circuit Cellar online article

Early look at MicroBlaze Architecture & Instruction Set

## CIRCUIT CELLAR ONLINE

#### SILICON UPDATE

Tom Cantrell

#### Core War

© 2001 89 System-On-a-P hether it's in the courtroom or in the selected areas

key, I suppose.

Sometimes I wonder if either party really has any interest in finally settling the matter. After all, as we saw in the good old days of the Cold War, while the heavyweights are circling, the lightweights (i.e., anyone else who dares to stick their hand into the programmable gate array cookie jar) keep their heads down.

#### GUNS BLAZING

Naturally, the Xilinx and Altera titfor-tat extends beyond the courtroom to the product front. The religious war over who has the better FPGA architecture rivals the RISC versus CISC hyperbole of yore. Following the analogy, it's no surprise that as progress marches on, both sides' parts look more alike, calling for more finely parsed nit-picking by each camp's well-entrenched troops.

### PLD World Korea 2001 MicroBlaze Instruction Set

- 32-bit only microprocessor

- Requires larger, wider RAM

- Very few, simple instructions

- More instructions required per operation

- Instruction variants (e.g. ADD, ADDC, ADDK, ADDKC, ADDI) require a setup instruction

- One bit per shift only; No left shift operator

- Requires more cycles for multi-bit shift operations

- Use ADD for 1-bit left shift

- Could use full multiplier circuit for multi-bit shift

- Eats hardware resources

- Device specific optimization

- No Custom Instruction

System-On-a-Programmable-Chip Solutions

| Opcode      | Destination register      | Source register A       | Source register B     | 0 0 0 0 0 0 0 0 | 0 0 0 0 |

|-------------|---------------------------|-------------------------|-----------------------|-----------------|---------|

| 0           | 6                         | 11                      | 16                    | 21              | 31      |

| Opcode<br>0 | Destination register<br>6 | Source register A<br>11 | Immediate value<br>16 |                 | 31      |

Table 2—With only two opcode formats, MicroBlaze pays more than lip service to the concept of a reduced instruction set.

| Addition St                                       | ubtract                                              | Multiplicatior | n Sign<br>extend | Logic                                            | Condition<br>branch                                                                                                                                    | Uncondition<br>branch                                                                                 | Load/Store                                              | Special    |

|---------------------------------------------------|------------------------------------------------------|----------------|------------------|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------|------------|

| ADDC R                                            | RSUB<br>RSUBC<br>MFS                                 | MUL<br>MULI    | SEXT8<br>SEXT    | AND<br>16 ANDI                                   | BEQ                                                                                                                                                    | BR                                                                                                    | LBU<br>BEQD                                             | IMM<br>BRA |

| ADDK R<br>ADDKC R<br>ADDI R<br>ADDIC R<br>ADDIC R | NFS<br>RSUBK<br>RSUBKC<br>RSUBIC<br>RSUBIC<br>RSUBIC |                |                  | ANDN<br>ANDNI<br>OR<br>XORI<br>SRA<br>SRC<br>SRL | BEQI<br>BEQID<br>BGED<br>BGEI<br>BGTD<br>BGTI<br>BGTID<br>BLE<br>BLED<br>BLEI<br>BLEID<br>BLT<br>BLTD<br>BLTI<br>BLTID<br>BNE<br>BNED<br>BNEI<br>BNEID | BRD<br>BRLD<br>BRLD<br>BRI<br>BRAI<br>BRAI<br>BRAID<br>BRAID<br>BRALID<br>BRK<br>BRKI<br>RTID<br>RTSD | LHU<br>LHUI<br>LW<br>SB<br>SBI<br>SH<br>SH<br>SW<br>SWI | MTS        |

Table 3—The MicroBlaze instruction set is even simpler than it looks, with multiple variants of a single instruction. For instance, the Branch Greater Than instruction (BGT) has delayed (BGTD), immediate (BGTI), and delayed immediate (BGTID) versions.

## PLD World Korea 2001 MicroBlaze Register File

#### **Only 31 registers**

- C compiler uses most registers for dedicated function

- R0 is all zeroes

- Extra instructions are needed to store/load registers to memo

| gisters to memoryo      | iully reachabl |

|-------------------------|----------------|

| Required when all spare |                |

| registers fill up       |                |

| Slows execution         | ノト             |

| Bloats code size        |                |

|                         | OLH            |

| Register | Туре        | Purpose                             |

|----------|-------------|-------------------------------------|

| R0       | Dedicated   | Value 0                             |

| R1       | Dedicated   | Stack pointer                       |

| R2       | Dedicated   | Read-only small data pointer        |

| R3–R4    | Volatile    | Return values                       |

| R5–R10   | Volatile    | Passing parameters/temporaries      |

| R11–R12  | Volatile    | Temporaries                         |

| R13      | Dedicated   | Read-write small data pointer       |

| R14      | Dedicated   | Return address for interrupt        |

| R15      | Dedicated   | Return address for sub-routine      |

| R16      | Dedicated   | Return address for trap (debug)     |

| R17      | Dedicated   | Return address for exceptions       |

| R18      | Dedicated   | Reserved for assembler              |

| R19–R31  | Nonvolatile | Must be saved across function calls |

Table 1-The GNU C compiler maps certain conventions on top of the general-purpose registers. Note the use of R2 and R13 to point at a small (64-KB) data area, fully reachable by the 16-bit offset accommodated in the 32-bit instructions.

## **MicroBlaze FUD Busting**

- FUD: "MicroBlaze is faster"

- Fmax is higher, but so is the number of instructions required for a given operation (side effect = Big code & lower performance)

- Advertised performance assumes memory is on-chip unrealistic for real systems

- They're using Virtex II's fastest speed grade

- FUD: "MicroBlaze is smaller"

- MicroBlaze's advertised size is probably for the CPU logic only

- Nios LE count includes the Avalon bus, Interrupt Generation Logic

- LE count is all FUD until Xilinx releases the product

Strict RISC core may be smaller, but at the expense of code size

FUD: "MicroBlaze is a full 32-bit processor. Nios has 16-bit instructions"

So?

Wider instructions require more memory to store them Most microcontroller applications don't want big memory

## How we see it

Our Real Competition is Microcontroller Market (33MHz – 80MHz)

- Motorola, Hitachi, Intel, Philips, etc.

#### Xilinx MicroBlaze

- Large Code Requirements

- 32-bit Instructions

- Few General Purpose Registers

- Simplistic Instruction Set

- Fmax Based on On-Chip Memory

- Expensive, Impractical

- No Synchronous External Memory Interface

- They will Achieve 50MHz-66MHz Access

- What is Their Total System Size

- CPU, Peripherals, Memory I/F, Memory

- System Builder Megawizards are a Significant Competitive Advantage

00

Nios has 1-year head start on documentation, applications &

20 reference designs

## **Software Tools**

© 2001

Accelerating Software Development

PLD World Korea 2001 Software Developer Needs **Integrated Development Environment** Edit, Compile, Run, Download, Debug Real-Time Debug **Stop on Condition** Hardware Break Points **Software Trace** Capture Program Informatio **During Execution Reconstruct to a Source**

PLD World Korea 2001 Software Debugger **On-Chip Debug (OCD) Peripheral** Real-Time Debug (Hardware Breakpoints) Software Trace Viosoft Arriba! IDE Arriba! Embedded Edition for Altera NIOS Edit View Project Build Tools Target Debug Help 🖻 🖬 🕷 🛍 🥵 🕒 🧶 📲 🕷 🖬 🕷 🖓 ni ni 🕸 👗 🖓 🔍 Supports Nios OCD disassembly dhry\_1.c dhry\_2.c 🖻 😁 🔄 General Register 72: Int Par Ref becomes 18 g0: 0x00000020 One\_Fifty 73: Int 1 Par Val; a1: 0x00000011 One Fifty Int 2 Par Val; 74: q2: 0x0000000 75: One\_Fifty \*Int Par Ref; a3: 0x0004b704 Edit, Compile 76: a4: 0x80808080 77: One\_Fifty Int\_Loc; a5: 0xfefefeff 78: q6: 0x00000004 79: Int\_Loc = Int\_l\_Par\_Val + 2; q7: 0x00024df2 \*Int Par Ref = Int 2 Par Val + Int Loc; 80 off: 0x00040fd8 /\* Proc 7 \*/ o1: 0x000493be > 81: Download o2: 0x0004fe9c 82 o3: 0x00000000 83 o4: 0x00000000 84: Proc 8 (Arr 1 Par Ref, Arr 2 Par Ref, Int 1 Par Val, Int o5: 0x00000000 85 sp: 0x0007fdec 86: executed once \*/ 87 Run, Debug 🖶 Browse 🙀 Workspace Debug Build 🗸 Debug 🗸 Find 🗸 Info Proc\_7; 81; /arriba-nios/demo/dhrystone/dł Variables :58:25 PMI Starting C:\Arriba-Nic Proc\_3; 401; /arriba-nios/demo/dhrystone/d Int\_Loc = 12 -01 6:58:26 PM] <DBG> GNU gdb 4.1 Int\_1\_Par\_Val = 10 Jul-01 6:58:26 PM] <DBG> Copyright 200 Int 2 Par Val = 5 4-Jul-01 6:58:26 PMI <DBG> Copyright 199 🗄 💼 Int\_Par\_Ref = 0x4df64 24-Jul-01 6:58:53 PM] Loading program syn lul-01 6:59:02 PMI Starting target...<TA Target hit a breakpoint Ln 1, Col 1, Ch REC MOD INS REAL

- 🗆 🗡