## FPGA Co-Processing for DSP

- Applications of FPGA-Based Co-Processors for DSP

- Development Tools & Methodologies Available from Altera to Build Co-Processors

- SOPC Builder

- DSP Builder

- FPGA Co-Processor Development Examples

- QAM Modulator

- FIR Filter

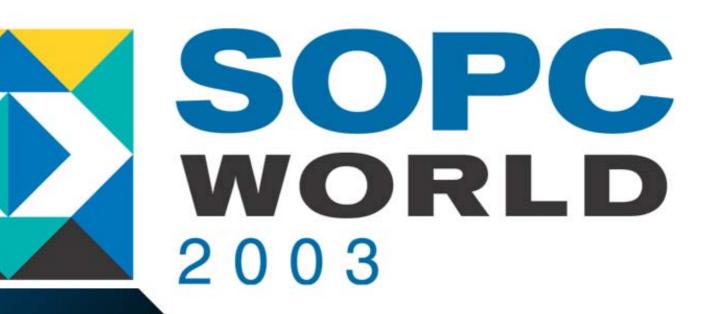

### **Growing Demand for MIPS & Memory Bandwidth**

**Digital Signal**

Time

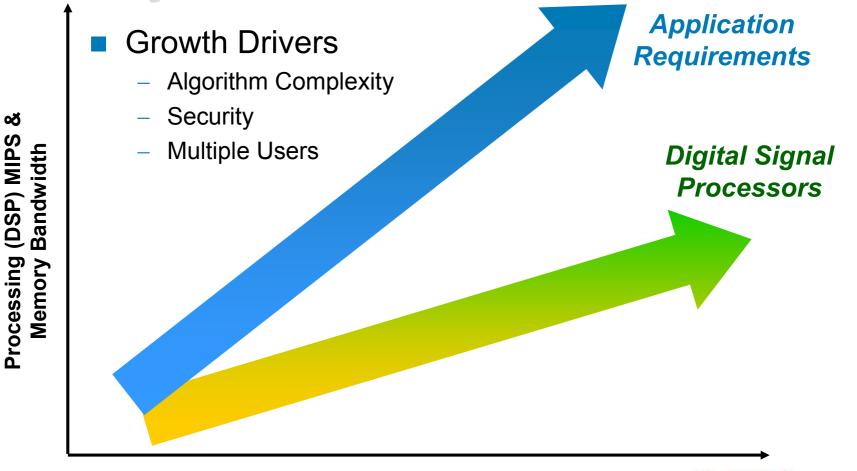

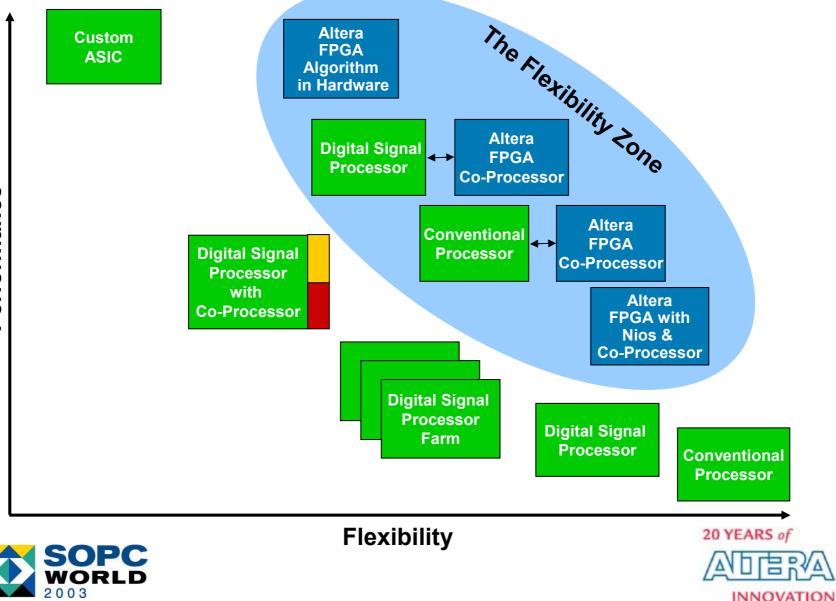

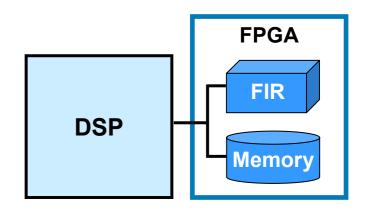

#### **DSP System Architecture Options**

Stand-Alone Processor Processor Array

Processor + Co-Processor Dedicated Hardware Architecture

#### **Exploring the DSP Design Space**

Performance

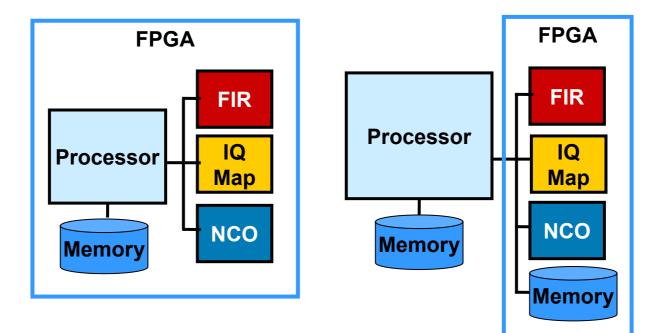

## **Co-Processing on FPGAs**

Processor on FPGA

Processor External to FPGA

### When Do FPGA Co-Processors Reduce System Cost?

Off-Loading Algorithms to Co-Processor Reduces Number or Cost of Digital Signal Processors

#### Applications

Algorithms with Large Amount of Digital Signal Processing & Small Amount of Control Processing

# **FPGA Co-Processor Applications**

#### Wireless

- 2.5-G EDGE Equalization

- 3-G Baseband Processing

- HSDPA

- 1xEVDV

- 3-G RF Linearization

- Consumer

- Broadcast Studio & Cable Plant

- Digital Entertainment MPEG2 & MPEG4

- Medical

- Imaging

- Wireline Communications

- Encryption

- Framer

- Traffic Management

- TCP/IP

- Computer & Storage

- Data Analysis & Routing Engine

- Digital Imaging

- Military & Aerospace

- Security

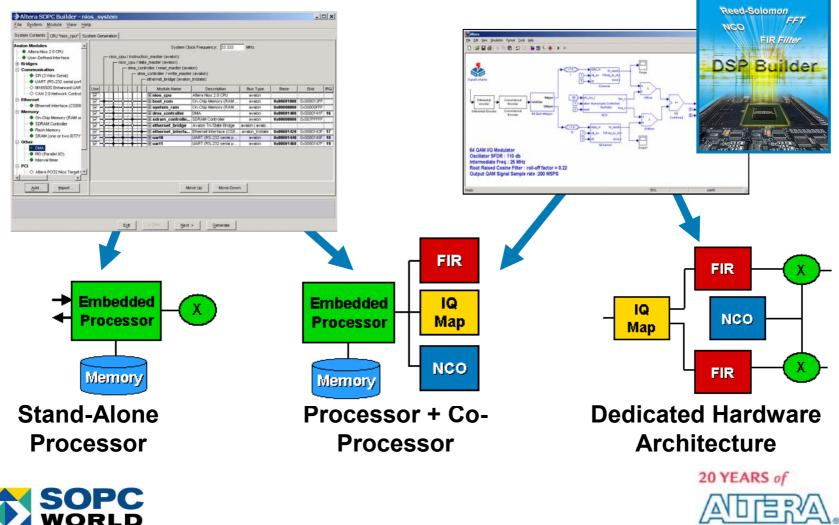

# DSP Development Tools & Design Methodology

## **FPGA Co-Processor Design Tools**

#### SOPC Builder

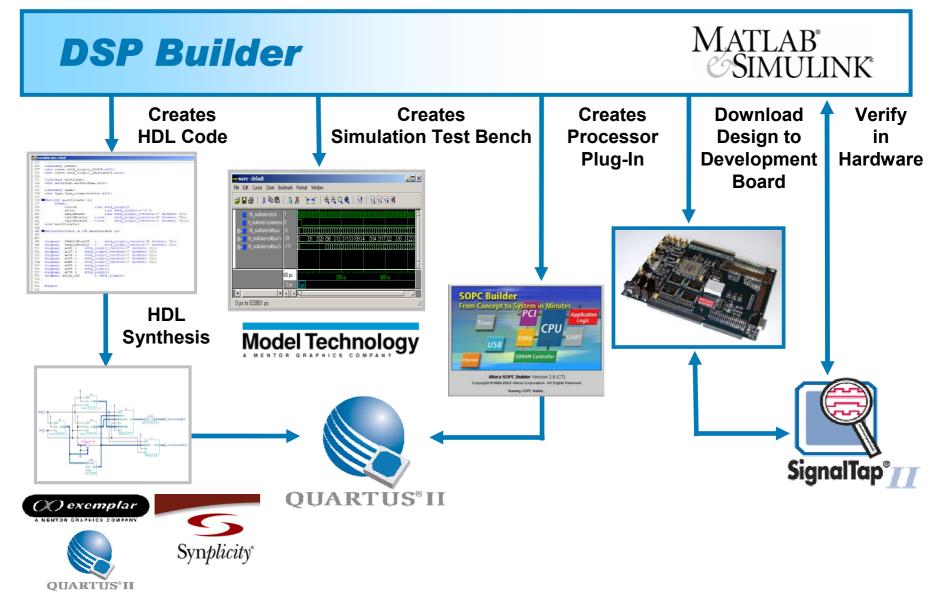

#### **DSP Builder**

INNOVATION

## **DSP Builder Overview**

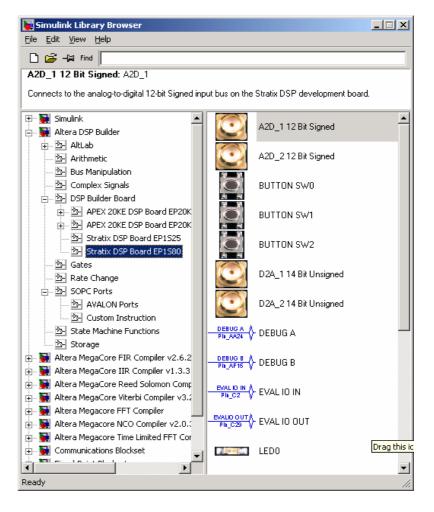

# **DSP Builder Library Components**

- Arithmetic

- Bus Manipulation

- Complex Signals

- Logical Components

- SOPC Ports

- Storage

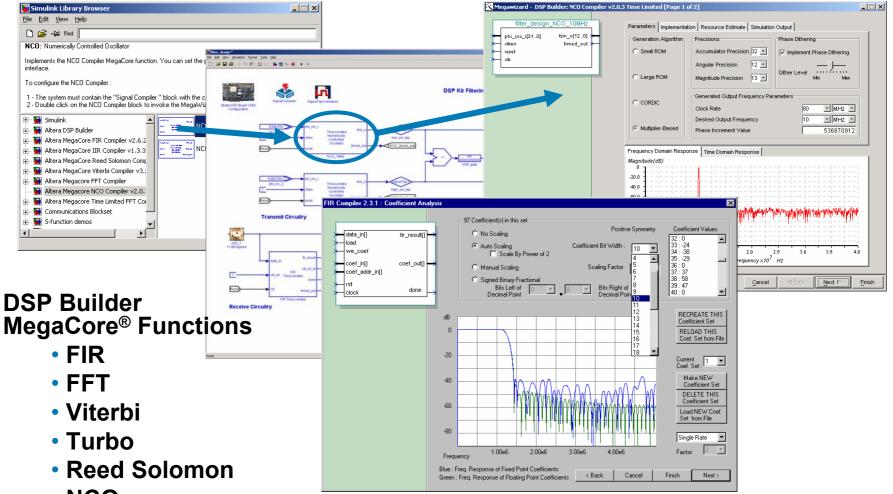

- MegaCore<sup>®</sup> IP

- Rate Change

- State Machine

- Altera Library

- DSP Board

#### **MegaCore IP in DSP Builder**

• NCO

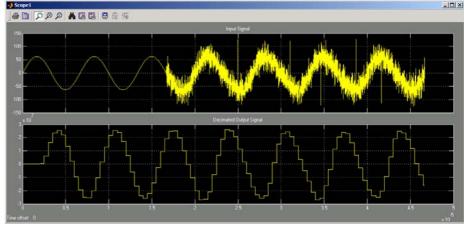

## DSP Builder Support for Multiple Clock Domains

- Inherit Sampling Frequency (FS)

- Adhere to Clock Design Rules

- All Sample Times Match One of Phase-Locked Loops (PLLs) Output Clock Periods

- Simplify Analysis & Implementation of Multi-Rate System

- Up Sampling

- Down Sampling

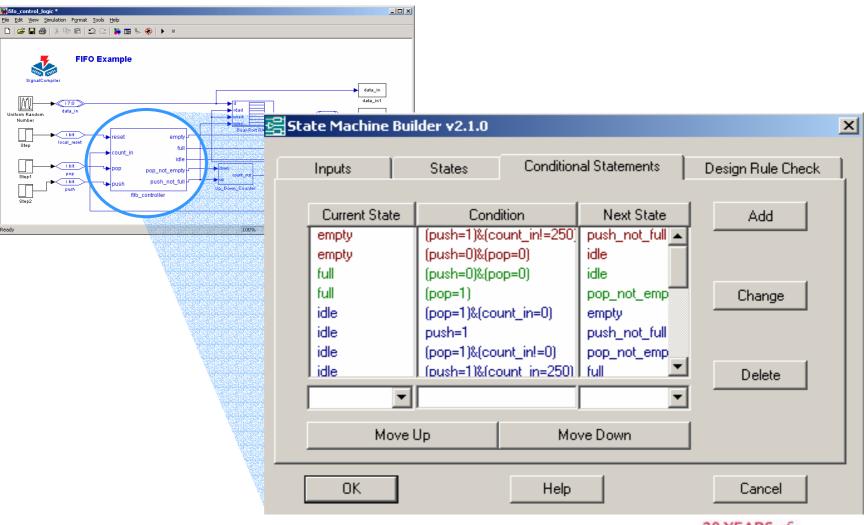

### **State Machine Builder**

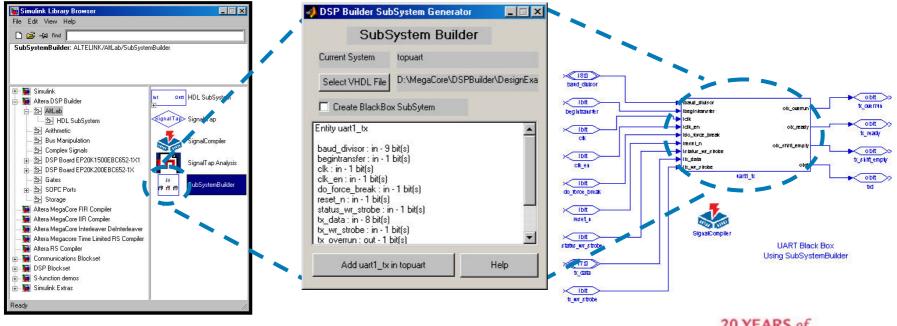

# **Sub-System Builder**

- Import Existing VHDL Design into Simulink

- Simulink Simulation Options

- Convert into DSP Builder Blocks or MATLAB Functions

- Treat VHDL Design as Black Box

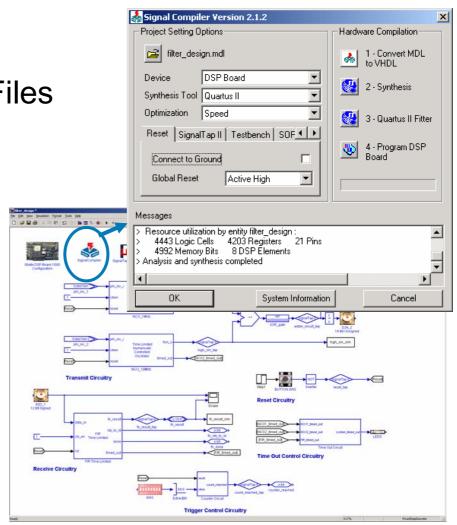

# **Signal Compiler**

- Generates VHDL Design Files

- Generates Tool

Command Language (Tcl) Scripts

- Generates Testbench

- Enables Parameterization of IP Blocks

- Launch Hardware

Compilation from

Simulink Cockpit

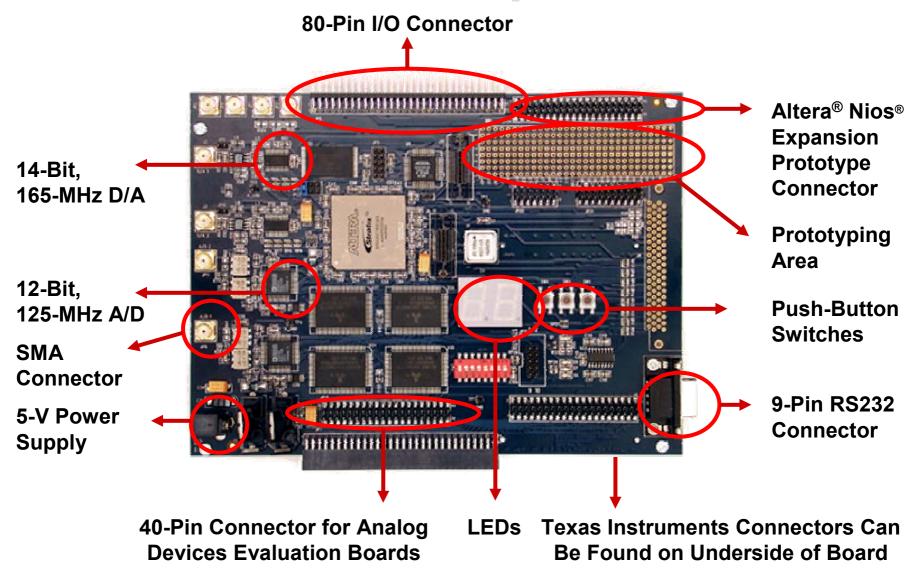

## **Stratix DSP Development Board**

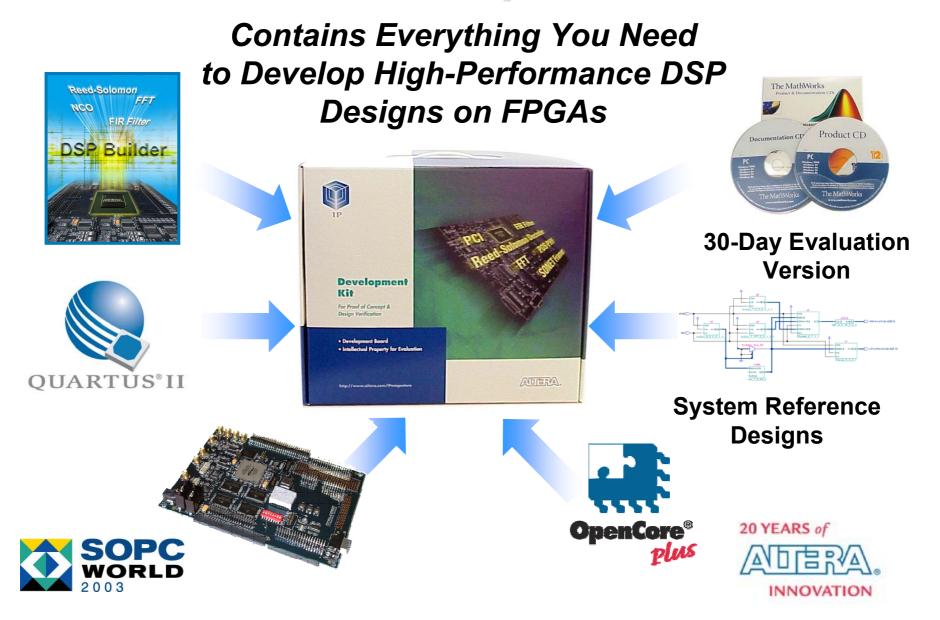

## **Altera DSP Development Kits**

## QAM Modulator Co-Processor Design Example

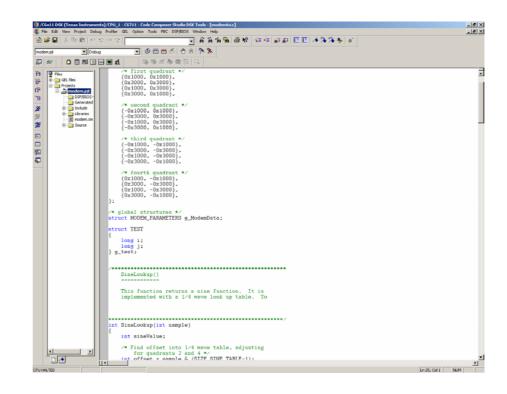

# **Modem Reference Design**

- Installed with Code Composer Studio As a Tutorial

- C:\ti\tutorial\dsk6711\modem

- Used to Demonstrate CCS Functionality

- 16 QAM TX Modem

## **Modem Design Code Profile**

|    | Functions                          | Code Size | Count | Incl. Total | Incl. Maximum | Incl. Minimum | Incl. Average | Exel. Total |

|----|------------------------------------|-----------|-------|-------------|---------------|---------------|---------------|-------------|

|    | ⊡ modem.out                        |           |       |             |               |               |               |             |

|    | 🖻 📄 modemtx.c                      |           |       |             |               |               |               |             |

| ¢∳ | 🚽 🙀 main                           | 548       | 1     | 4222002     | 0             | 0             | 4222002       | 23446       |

|    | 😡 Modem Transmitter                | 304       | 7     | 4038331     | 580782        | 579499        | 576904        | 83981       |

| C  | 🚽 🧹 😡 ShapingFilter                | 356       | 14    | 3610811     | 258438        | 257493        | 257915        | 361.0811    |

|    | 🚽 🥎 Modulation                     | 236       | 213   | 341498      | 1656          | 1584          | 1603          | 97649       |

| 1  | 🛛 🛶 💊 SineLookup                   | 148       | 490   | 264817      | 615           | 493           | 540           | 264817      |

| Β  | — 💊 Initialize                     | 636       | 1     | 117760      | 117760        | 117760        | 117760        | 117760      |

|    | 🚽 💊 CosineLookup                   | 56        | 245   | 143448      | 646           | 539           | 585           | 9065        |

| ζĦ | 🚽 🥎 ReadNextData                   | 40        | 7     | 5692        | 820           | 808           | 813           | 259         |

| Ĝ∎ | 🚽 🥎 ReadConstellation              | 40        | 7     | 5370        | 774           | 762           | 767           | 259         |

|    | 🛄 🧼 🔬 AddNoiseSignal               | 508       | 7     | 5048        | 728           | 716           | 721           | 5048        |

|    |                                    |           |       |             |               |               |               |             |

|    |                                    |           |       |             |               |               |               |             |

|    |                                    |           |       |             |               |               |               |             |

|    |                                    |           |       |             |               |               |               |             |

|    | 📄 Files 💆 Functions 🧵 Ranges Setup |           |       |             |               |               |               |             |

|    |                                    |           |       |             |               |               |               |             |

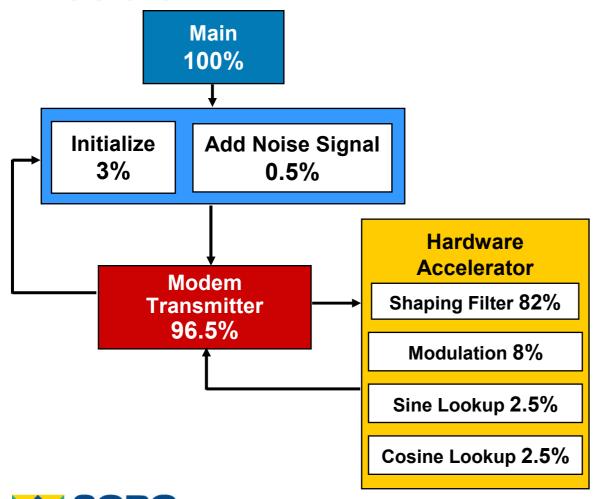

#### Modem Design Hardware/ Software Petition

### **Modulator Co-Processor**

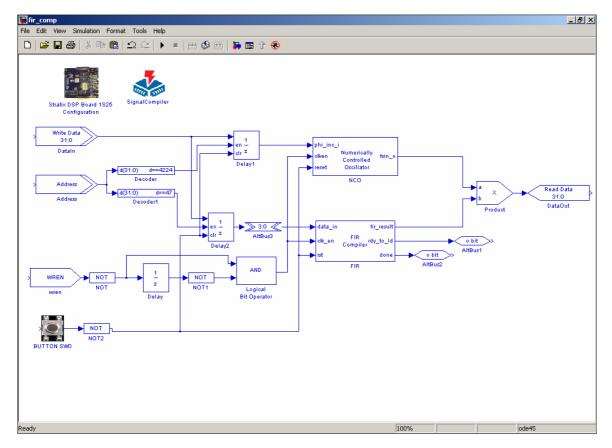

#### DSP Builder Used to Build Hardware DSP Data Path

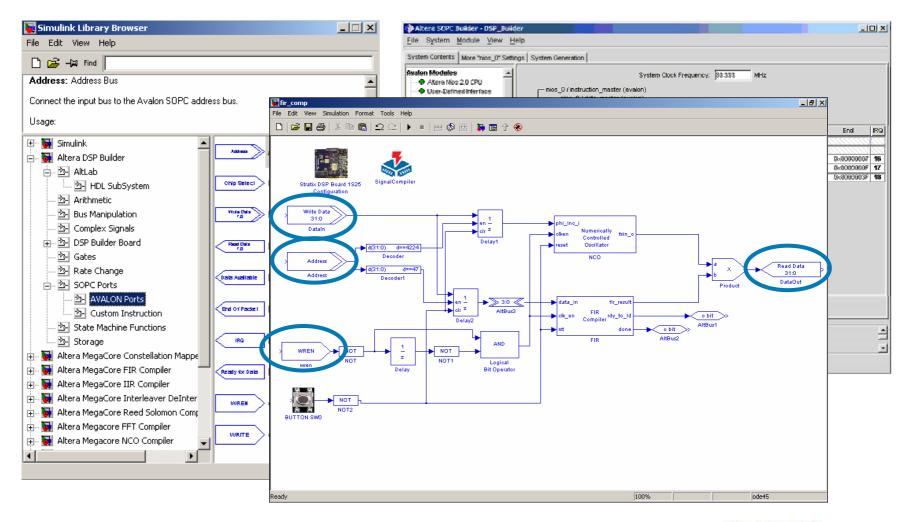

#### **Avalon™ Interface in SOPC Builder**

#### **DSP Builder— SOPC Builder Import**

#### Import DSP Builder Generated Co-Processor into SOPC Builder

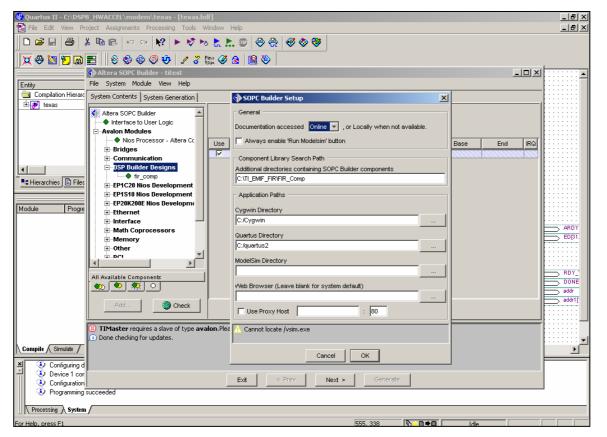

## **SOPC Builder Integration**

#### Modem Co-Processor (fir\_comp) Integrated with TI EMIF I/F (TIMaster)

| Interface to User Logic Avalon Modules Nos Processor - Altera Cc Bridges Communication DSP Builder Designs Finceomp EP1C20 Nios Development EP20K200E Nios Development Ethernet Halt Available Components Concerts Memory Module Components More Up Move Up Move Down                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Altera SOPC Builder - titest File System Module View Help System Contents System Generation |     |                   | System Clock Frequen | cy: 80 MHz             |            |           |     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-----|-------------------|----------------------|------------------------|------------|-----------|-----|

| Bridges       Use       Module Name       Description       EUs type       Base       End       Int         Communication       DSP Builder Designs       Image: Composition       Bit Master       Texas       avalon       0x00000020       0x0000020       0x0000020       0x00000020       0x0000020       0x0000020       0x0000020       0x0000020       0x0000020       0x0000020       0x0000020       0x0000020       0x0000020 <t< td=""><td>Interface to User Logic</td><td>г.</td><td>TIMaster (avalon)</td><td>System Clock Trequen</td><td>cy. <u>100</u> 1981 12</td><td></td><td></td><td></td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Interface to User Logic                                                                     | г.  | TIMaster (avalon) | System Clock Trequen | cy. <u>100</u> 1981 12 |            |           |     |

| Communication     DSP Builder Designs     FP1C20 Nios Development     EP20K200E Nios Development     Ethernet     Interface     Math Coprocessors     Memory     Other     Dor     Add     Creck     Move Up     Move Down                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                             | Use | Module Name       | Description          | Bus Type               | Base       | End       | IRQ |

| OSP Builder Designs     Frigeomp     fir_comp     fir_comp     sevalon     Ox00000020     Ox0000000     Ox0000000     Ox000000     Ox000000     Ox0000000     Ox000000     Ox000000     Ox00000     Ox00000     Ox000000     Ox000000     Ox000000     Ox00000     Ox00000     Ox00000     Ox00000     Ox00000     Ox00000     Ox00000     Ox00000     Ox00000     Ox000000     Ox000000     Ox000000     Ox00000     Ox00000     Ox00000     Ox00000     Ox00000     Ox00000     Ox00000     Ox00000     Ox0000     Ox0000     Ox0000     Ox0000     Ox0000     Ox0000     Ox0000     Ox0000     Ox000     Ox000     Ox0000     Ox000     Ox000     Ox000     Ox000     Ox000     Ox000     Ox000     Ox00     Ox00     Ox00     Ox000     Ox00     Ox00     Ox00     Ox00     Ox00     Ox00     Ox00     Ox00     Ox00 |                                                                                             |     | TIMaster          | Texas                | avalon                 | 1111111    |           | 777 |

| Image: Construction       Image: FP1C20 Nios Development       Image: FP20K200E Nios Development       Image: FP20K20E Nios Development       Image: FP2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                             |     | ⊞ fir_comp        | fir_comp             | avalon                 | 0x00000020 | 0x0000002 | 7   |

| Move Up     Move Down     Move Down                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | All Available Components                                                                    |     |                   | 1                    |                        |            |           |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Done checking for updates.                                                                  |     |                   |                      |                        |            |           |     |

| Exit < Prev Next > Generate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                             |     |                   |                      |                        |            |           |     |

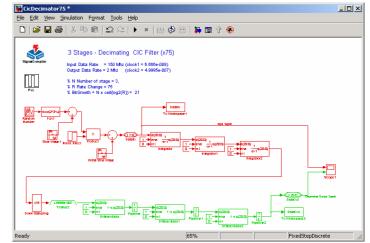

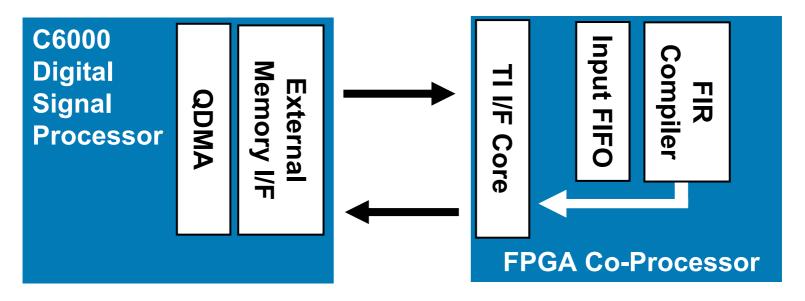

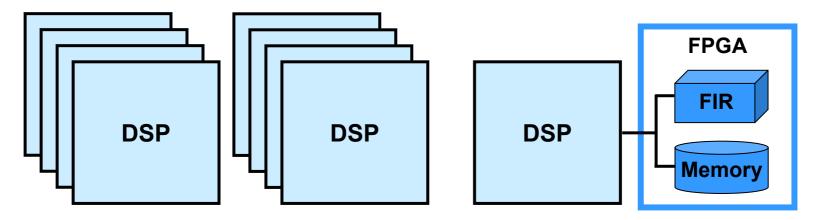

# FIR Filter Co-Processor Design Example

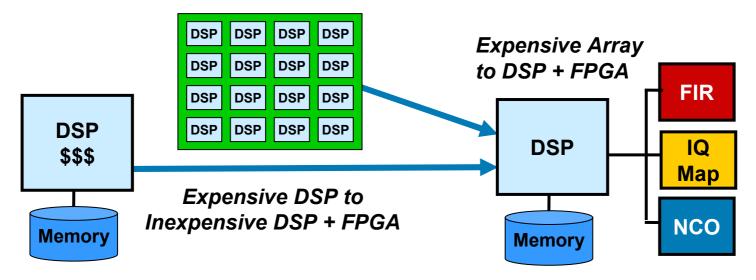

## **Driving Down System Costs**

Multi-Processing DSP

Digital Signal Processor + FPGA Co-Processor

# FIR Co-Processor Design Example

- FIR Parameters

- 128-Tap

- 16-Bit Data, 14-Bit Coefficients

Four FIR Implementations for Comparison

- TI C6711-Optimized TI DSPLib Function

- TI C6416-Optimized TI DSPLib Function

- Altera Eight-Cycle FIR Co-Processor

- Altera One-Cycle FIR Co-Processor

# **TI Filtering Library (DSP Lib)**

- C-Callable Optimized Assembly Routines

- TI C67x DSPLib: Fir Filter (Radix 8)

- Formula: Nh \* Nr /2 + 13

- Nh = Number of Coefficients

- Nr = Number of Samples

- -~1 Sample/ 64 Cycles (128 Tap Filter)

- TI C64x DSPLib: FIR Filter (Radix 8)

- Formula: Nh \* Nr/4 + 17

- -~ 1 Sample/ 32 Cycles (128 Tap Filter)

## Filter Co-Processor Design Example

- Current Implementation

- 100 MHz, 32-Bit, Asynchronous EMIF on DSK

- TI Writes 300 Samples to Co-Processor (Input Data)

- Filter & Send Output to TI

#### FIR Filter Example\* – 16X Cost/Performance Improvement

| Device             | Solution                  | FIR Performance<br>(MHz) | Device<br>Cost**** | Cost per<br>FIR MHz |

|--------------------|---------------------------|--------------------------|--------------------|---------------------|

| TI C6713-200       | 64-Cycles**<br>at 200 MHz | 3.125                    | \$24.59            | \$7.87              |

| TI C6416-600       | 32-Cycles**<br>at 600 MHz | 18.75                    | \$160              | \$8.53              |

| Altera<br>EP1C3-8  | 7-Cycles***<br>at 200 MHz | 28                       | \$14               | \$0.50              |

| Altera<br>EP1C12-8 | 1-Cycle***<br>at 170 MHz  | 170                      | \$84               | \$0.49              |

- \* FIR 128 Tap, 16-Bit Data, 14-Bit Coefficients

- \*\* DSPLib Optimized Assembly Libraries from Texas Instruments

- \*\*\* Optimized MegaCore FIR Compiler from Altera

- \*\*\*\* Pricing in Quantity of 100 at Arrow 6/25/03

## **14X Reduction in System Costs**

| Architecture                        | FIR<br>Performance<br>(MHz) | Total FIR<br>Performance<br>(MHz) | Device<br>Costs | Total<br>Cost |

|-------------------------------------|-----------------------------|-----------------------------------|-----------------|---------------|

| 9 * TI C6416-600                    | 9 * 18.75                   | 167                               | 9 *<br>\$160    | \$1,440       |

| Altera EP1C12-8 +<br>1 TI c6713-200 | 170 + 3                     | 173                               | \$84 +<br>\$25  | \$110         |

## Summary

#### FPGA Co-Processors for DSP Offer Many Advantages

- 10X Performance Boost

- More Channels

- More Complex Algorithms

- Increased System Throughput

- 10X Cost Reduction

- Fewer Components

- Complementary to DSP-Based Systems

- Offloads Existing DSP

- Integrates Into Existing DSP IDE

- Evolution Not Revolution

## **Altera Code: DSP Solutions**

FPGAs

- Stratix, Stratix GX, Cyclone

- Development Tools

- DSP Builder, SOPC Builder

- Intellectual Property

- FIR, FFT, Viterbi, Turbo, Reed Solomon, NCO

- AMPP Third-Party Partners

- Development Kits

- Altera

- Third-Parties

- Design Services

- ACAP Third-Party Partners

- Training