# Implementing Video and Image Processing Designs Using FPGAs

Click to add subtitle

## **Agenda**

- Key trends in video and image processing

- Video and Image Processing Suite

- Model-based design for video processing

- Tutorial

## Video and Imaging With FPGAs

**Broadcast Infrastructure**

**HDTV Videoconferencing**

**HDTV** Display

Security DVR

**Document Imaging**

**Medical Imaging**

**HD Security Camera**

Military Imaging

Consumer/Auto Display

## Key Trends in Video and Imaging

- Higher resolutions

- 3,000 x 3,000 (and higher): medical imaging, military, machine vision

- 4,096 x 1,714: digital cinema

- 1,920 x 1,080: HDTV, broadcast

- 1,280 x 720: video surveillance, videoconferencing

- Advanced video compression

- H.264, JPEG2000, VC1

## **Current Solutions Do Not Deliver**

Video/ Imaging ASSPs

Not optimized for target applications Risk of obsolescence

**DSP**

Cannot achieve high definition in single device

**ASIC**

High development cost

Cannot keep up with fast-evolving applications

#### **Altera's FPGA Solution**

- High performance in a single device

- Fast time-to-market

- Easy to upgrade

- Low development cost

- Obsolescence proof

- Lower unit costs at high volumes

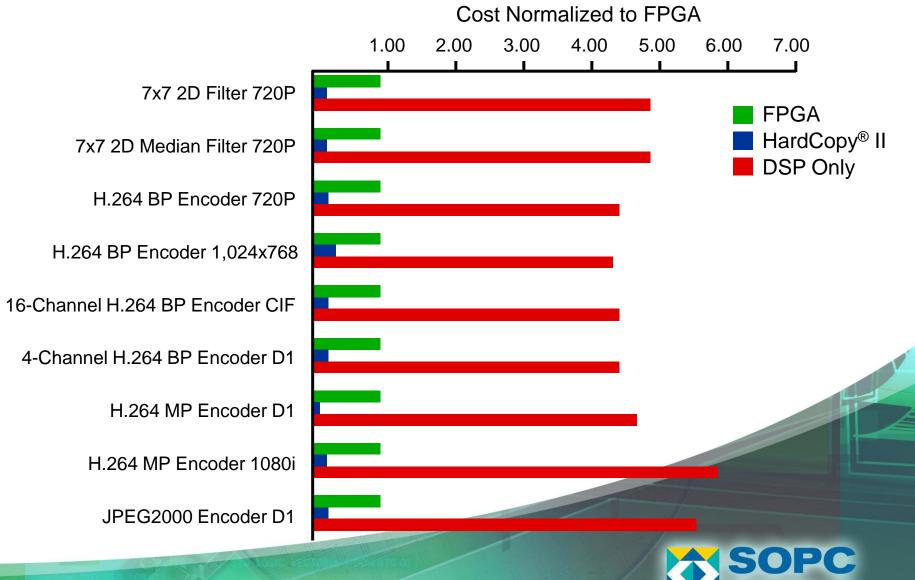

#### **Video Benchmarks**

## Altera Video and Image Processing Solutions Overview

DSP Algorithm Design Flow

VHDL/Verilog

MATLAB/ Simulink DSP Builder Synplicity

**'C' to Hardware**Mentor

Celoxica

Intellectual Property (IP)

Altera® Baseline Processing Functions

Third-Party Compression and Processing Functions

Altera and Third-Party Video I/O and Interface IP

System Integration

**SOPC Builder, VHDL/Verilog**

Devices and Dev. Kits

Cyclone® II, Stratix® II, HardCopy II

Video Reference Design

## IP Examples – Video

#### I/O and System

- PCI Express

- Serial Rapid I/O

- EMIF Interface

- ASI

- SDI

- ATA HDD (Nuvation)

- MPEG2 Transport

- 10/100/1000 Ethernet

- DDR/DDR2 Controller

Video and Image Processing Suite

#### **Pre-/Post-Processing**

- Scaler

- Deinterlacer

- 2D FIR Filter

- 2D Median Filter

- Color Space Converter

- Chroma Resampler

- Gamma Corrector

- Alpha Blender

- Highest Quality HDTV Upconversion (Let It Wave)

- AES/DES/Sha-1 Encryption (CAST)

#### Compression

- H.264 MP, HP (ATEME)

- H.264 BP (4i2i, CAST, W&W)

- H.264 CABAC/CAVLC (ATEME)

- H.264 Loop Filter (ATEME)

- MPEG4 SP/ASP (CAST, Barco)

- JPEG (CAST, Barco)

- JPEG2000 (CAST, Barco, Broadmotion)

## **HDTV Upconversion – Let It Wave**

- Breakthrough super-resolution Bandlet technology for HDTV upconversion

- Broadcasting equipment

- Upconverter implemented on cost-effective Altera FPGA

- Main features

- Standard definition (SD) to high definition (HD) up to 1080P

- 2-frame delay

- Color conversion

- Per pixel automatic film mode and cadence detection

- Aspect ratio conversion

- Additional features

- Cross conversion 720P to 1080I

- HD to SD down conversion

- Video enhancement

- Board reference design available

# Altera Video and Image Processing Suite

- Baseline set of IP with standard interfaces and protocols that allow users to easily add their own proprietary algorithms

- Optimized for Altera FPGAs

- Works with any design flow

- RTL, model-based design, C-based design

## Video and Image Processing Suite

| Core                  | Function                                                                                                                                      |  |  |  |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Deinterlacer          | Converts interlaced video formats to progressive video format                                                                                 |  |  |  |

| Color space converter | Converts image data between a variety of different color spaces                                                                               |  |  |  |

| Scaler                | Resizes and clips image frames                                                                                                                |  |  |  |

| Gamma corrector       | Performs gamma correction on a color space                                                                                                    |  |  |  |

| Alpha blending mixer  | Mixes and blends multiple image streams, including picture-in-picture (PIP)                                                                   |  |  |  |

| Chroma resampler      | Changes the sampling rate of the chroma data for image frames                                                                                 |  |  |  |

| 2D filter             | Implements a 3x3, 5x5, or 7x7 finite impulse response (FIR) filter on an image data stream to smooth or sharpen images                        |  |  |  |

| 2D median filter      | Implements a 3x3, 5x5, or 7x7 filter that removes noise in an image by replacing each pixel value with the median of neighboring pixel values |  |  |  |

| Line buffer compiler  | Efficiently maps image line buffers to Altera on-chip memory                                                                                  |  |  |  |

## **2D Filtering**

- 2D FIR filter and 2D median filter

- 3x3, 5x5 or 7x7 filter sizes

- Useful for noise reduction and smoothing filters

- Supports symmetric optimization

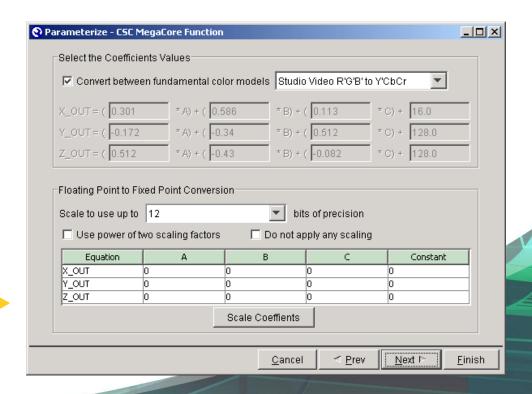

## **Color Format Conversion**

- Supplied as three separate cores

- Color space converter

- Chroma resampler

- Gamma corrector

- Supports

- RGB (computer and studio formats)

- YIQ/YUV (NTSC, PAL, SECAM)

- YCbCr (4:4:4, 4:2:2, 4:2:0)

# Image Blending and Picture-in-Picture Mixing

- Multi-layer mixing (2 to 8 layers)

- Per-pixel alpha blending

- Run-time control of picture-in-picture location

## **Scaling**

D1/SDTV: 720 x 480

HDTV 1080p: 1920 x 1080

- Supports standard-resolution conversions

- Nearest neighbor or bilinear filtering

- Clipping

## Deinterlacing

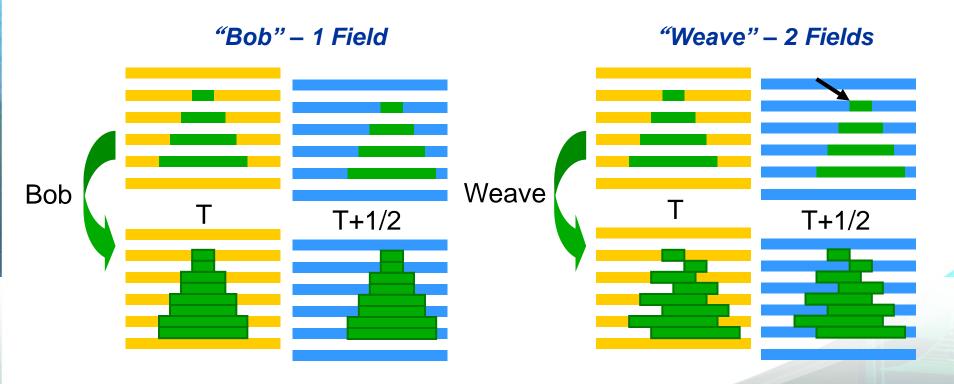

■ "Bob" and "Weave" supported

## Line Buffer Compiler

- Provides line buffers, making efficient use of FPGA internal memories

- Optimized for typical SD and HD resolutions

- Any number of bits per color plane

- Choose line length, width, number of lines

# Design Flow Starting with Model-Based Design

- DSP Builder for data path

- Design

- Simulation

- Creation of an SOPC Builder component

- SOPC Builder for system integration

- External RAM controllers

- Sources and sinks

- Processor integration

- Nios<sup>®</sup> II or external processor

- Compile in Quartus® II software

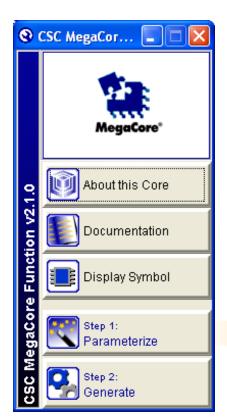

## Configure Blocks with GUI

- IP Toolbench

- Launched from Quartus II software or directly in DSP Builder

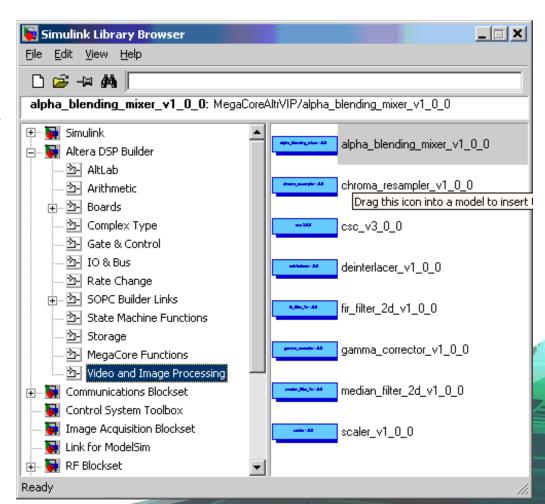

## **DSP Builder Video Library**

- Alpha blending mixer

- Chroma resampler

- Color space converter

- Gamma corrector

- Deinterlacer

- 2D FIR filter

- 2D median filter

- Scaler

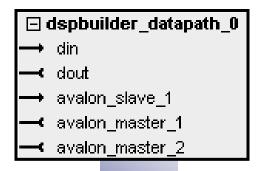

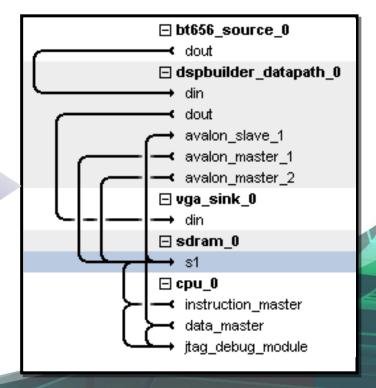

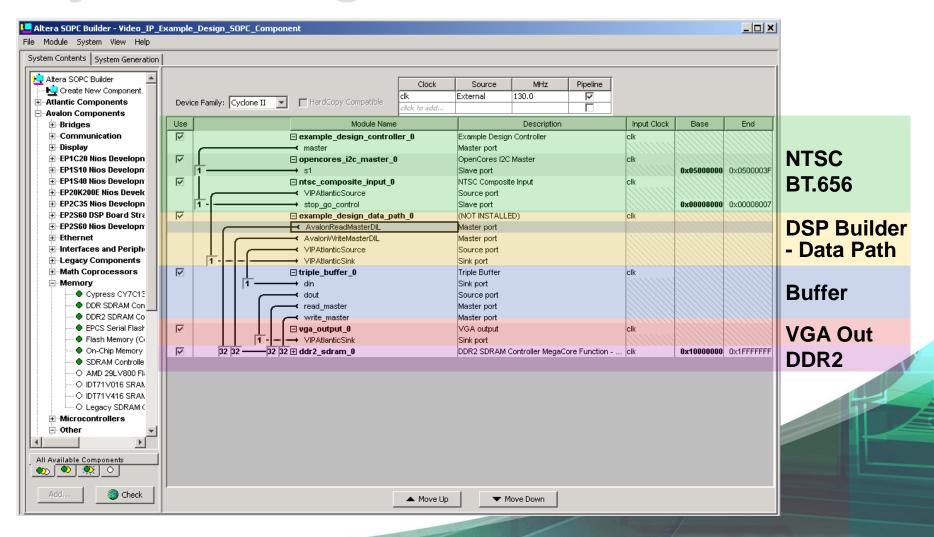

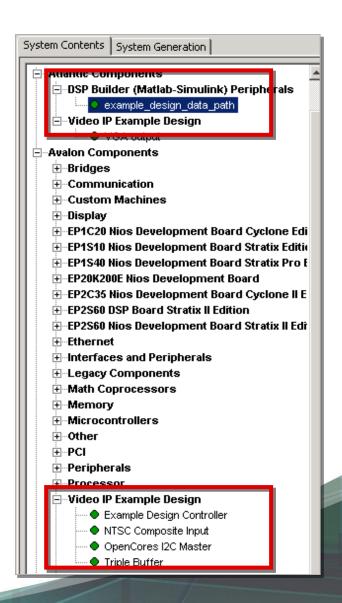

## **SOPC Builder System Integration**

#### **DSP Builder Data Path**

#### Add

- Sources

- Sinks

- Arbitrated DDR, SDR

- Control

#### SOPC Builder System

## **Example 1: Single Input Video Channel**

- Composite video input

- VGA output

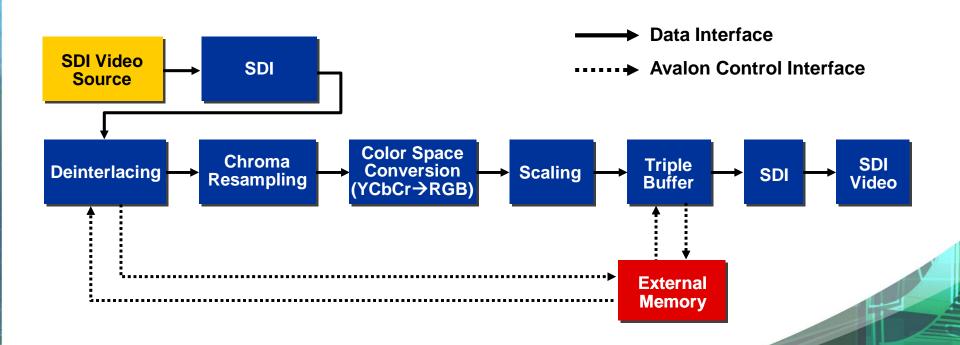

## **Example 2: Single Input Video Channel**

SDI video input/output

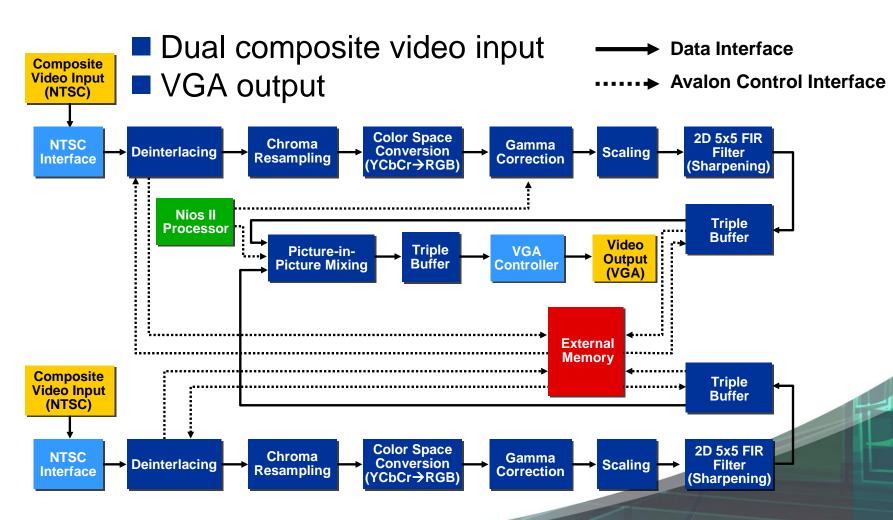

## **Example 3: Multiple Video Channel Input**

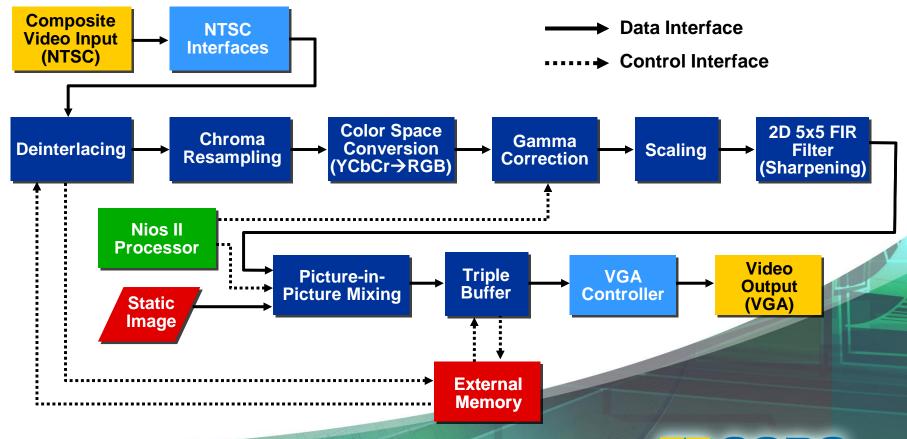

# Video and Image Processing (VIP) Example Design

## **Example of a Video System**

- System block diagram

- DSP Builder

- Implementation

- Simulation

- Conversion to HDL

- SOPC Builder integration

- Program hardware platform

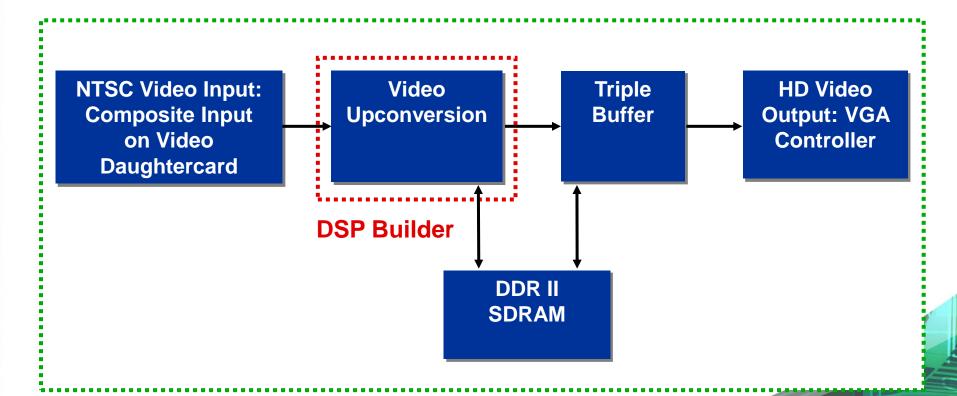

## **VIP Upconversion System**

**SOPC Builder**

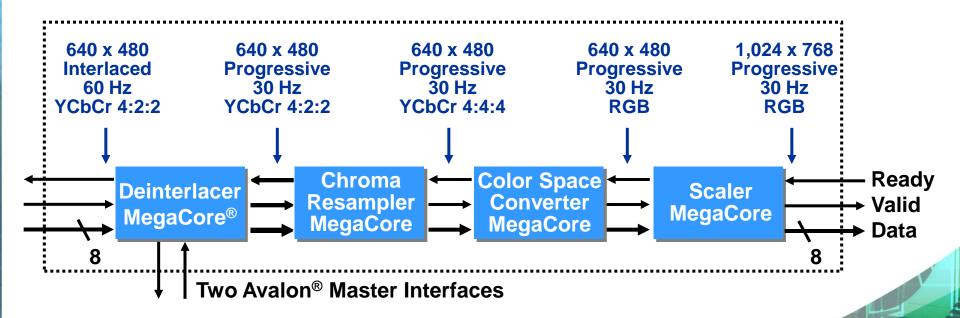

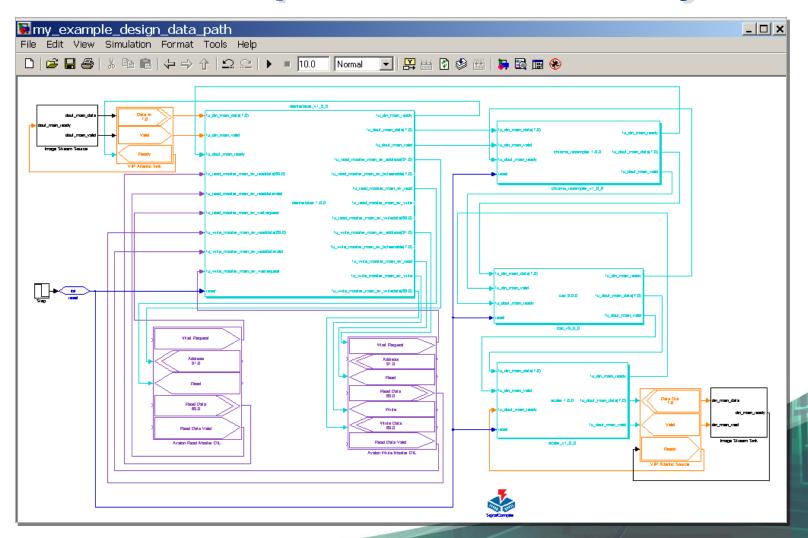

## Video Upconversion Data Path

Entire data path is assembled in DSP Builder

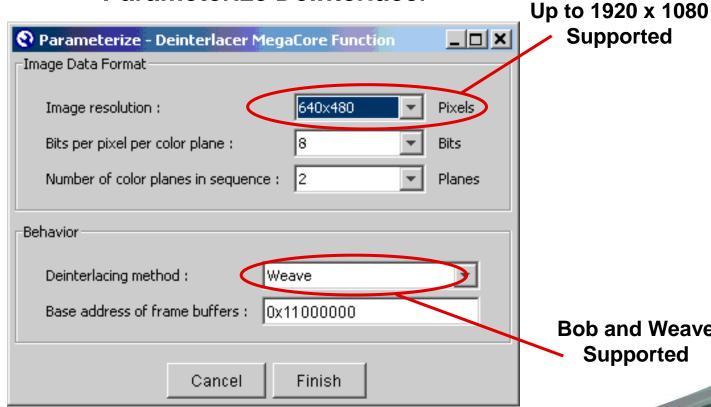

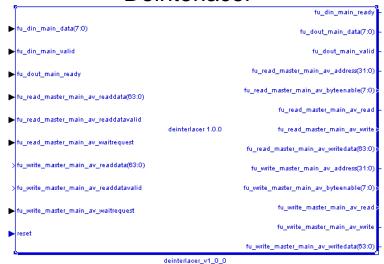

## **DSP Builder Implementation - Deinterlacer**

Parameterize Deinterlacer

**Bob and Weave Supported**

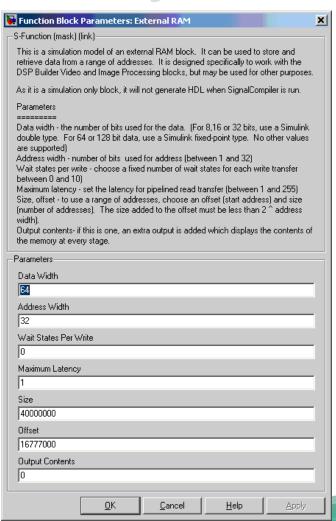

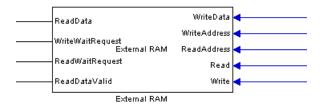

## DSP Builder Implementation: External Memory for Deinterlacer

Parameterize External Memory (Simulation-Only Model)

# DSP Builder Implementation: Chroma Resampler

| Parameterize - Chroma Resampler MegaCore Function         |                |          |      |        |  |  |

|-----------------------------------------------------------|----------------|----------|------|--------|--|--|

| Image Data Format                                         |                |          |      |        |  |  |

| Image resolution :                                        |                | 640×480  | ₹    | Pixels |  |  |

| Bits per pixel per color plane :                          | 8              | <b>T</b> | Bits |        |  |  |

| Color Plane Configuration: Three color planes in sequence |                |          |      |        |  |  |

| Behavior                                                  |                |          |      |        |  |  |

| Conversion format :                                       | 4:2:2 to 4:4:4 |          |      |        |  |  |

| Horizontal interpolation :                                | 2D Linear      |          |      |        |  |  |

| Vertical interpolation :                                  | 2D Linear      |          |      |        |  |  |

|                                                           |                |          |      |        |  |  |

|                                                           |                |          |      |        |  |  |

|                                                           | - 1            | 1        |      |        |  |  |

| Cancel Finish                                             |                |          |      |        |  |  |

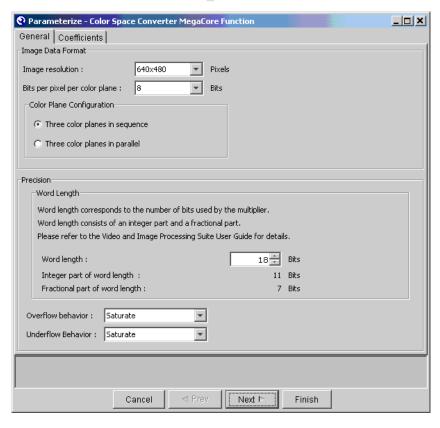

## DSP Builder Implementation: Color Space Converter

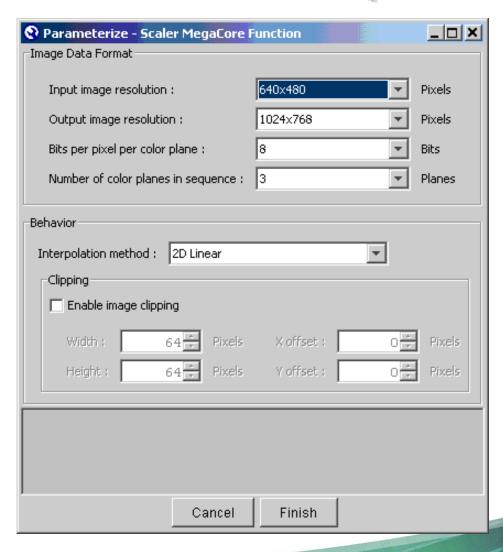

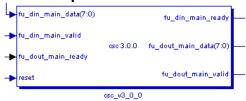

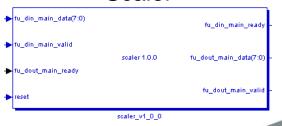

## **DSP Builder Implementation: Scaler**

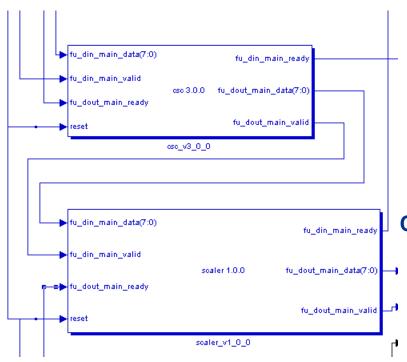

# DSP Builder Implementation: Libraries Generated Color Space C

#### Deinterlacer

#### **External Memory (Simulation)**

#### Color Space Converter

#### Chroma Resampler

#### Scaler

# DSP Builder Implementation: Connecting Functions

Connecting library functions is simple due to standard interface and protocol

**Connections Between the Color Space Converter and Scaler**

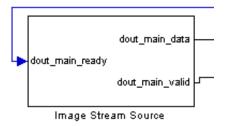

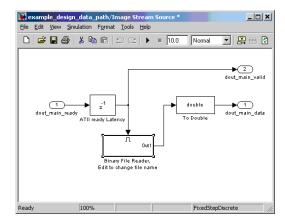

# Simulation: Video Input

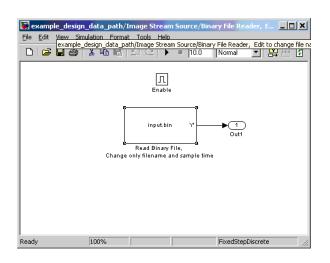

| Read Binary Fil<br>Read binary vi | deo data from file in | Source B<br>the specified for | lock Parameters:<br>mat. |

|-----------------------------------|-----------------------|-------------------------------|--------------------------|

| Parameters—                       |                       |                               |                          |

| File name: r\f                    | ull_basic_reference\  | data\input.bin                | Browse                   |

| <b>✓</b> Loop                     |                       |                               |                          |

| Number of tim                     | es to play file: 1    |                               |                          |

| Video format:                     | Four character cod    | es                            | ▼                        |

| Four characte                     | r code: GREY          |                               | ▼                        |

| Frame size                        | Rows: 1               | Cols: 1                       |                          |

| Line ordering:                    | Top line first        |                               | •                        |

| Sample time:                      | 1/(1024*768*3)        |                               |                          |

### Simulation: Generate Video Binary File

- Command Line Utility converts AVI file to a binary file for use within DSP Builder environment

- Also converts binary output to an AVI file for convenient playback

```

Command Prompt

C:\data\UIP\Uideo_IP_Example_Design\avi-is-avi>avi-is-avi

Incorrect number of arguments specified

Terminating

Version 0.14

Usage: avi-is-avi "InputFile" "OutputFile" IS_width IS_height mode(AVItoIS¦IStoA

Optional Parameters:

-v Enable Video viewers

-c IS colourspace (RGB|YCbCr) default YCbCr

-s IS subsampling (444|422|420) default 444/off

-q IS channels in sequence (3|1) default 3

Enable IS interlace

Begin frame number

default 0

End frame number

default -1 (runs to end)

Frame advance

default 1

r Output AVI fps

default 15

Only used AVItoIS mode

Only used IStoAVI mode

C:\data\VIP\Video_IP_Example_Design\avi-is-avi>

```

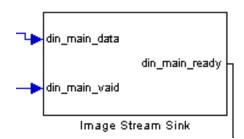

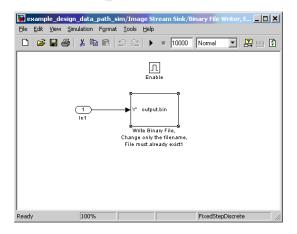

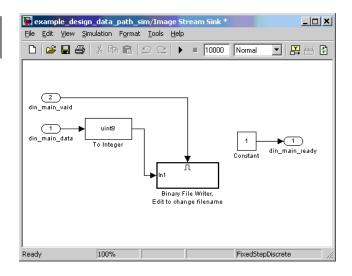

# Simulation: Video Output

| —Write Binary File—<br>Write binary video | o data into file in the specified format.    |

|-------------------------------------------|----------------------------------------------|

| -Parameters                               |                                              |

| File name: \\full_t                       | basic_reference_sim_2\data\output.bin Browse |

| Video format: Fo                          | our character codes                          |

| Four character co                         | ode: GREY                                    |

|                                           |                                              |

| Line ordering: To                         | op line first                                |

| Line ordering: T                          | op line first                                |

### Simulation: Upconversion Subsystem

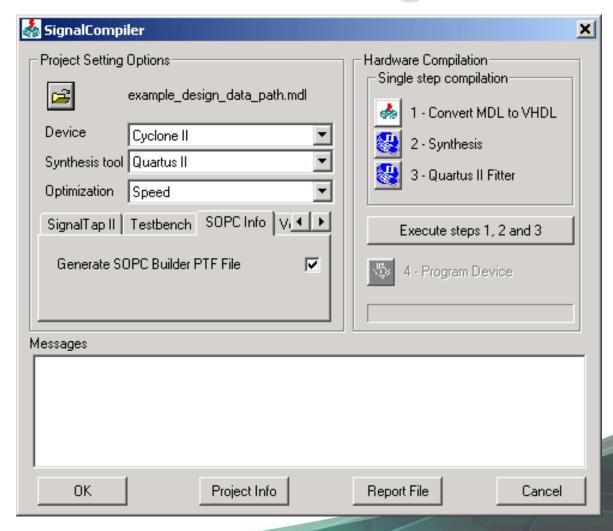

# **Convert to VHDL: Signal Compiler**

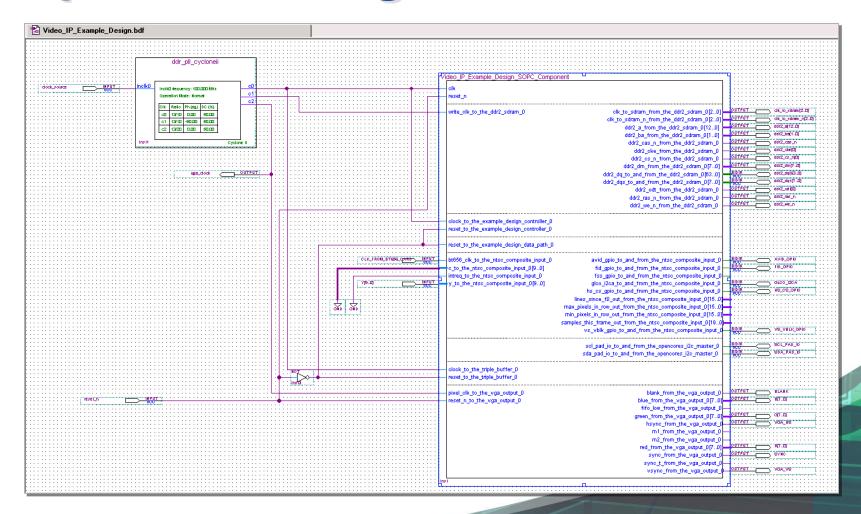

## Top-Level Design File in Quartus II

# System Integration: SOPC Builder

#### **Custom Hardware**

- Generated custom video interfaces IP

- Available within reference design package

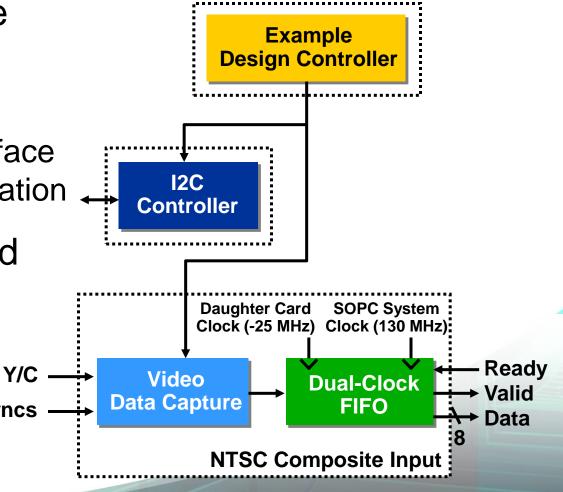

## NTSC Video Input

Video data capture with TI TVP5146 decoder

> I2C is control interface for device configuration

Controller designed in HDL

> Imported into **SOPC** Builder

**Syncs**

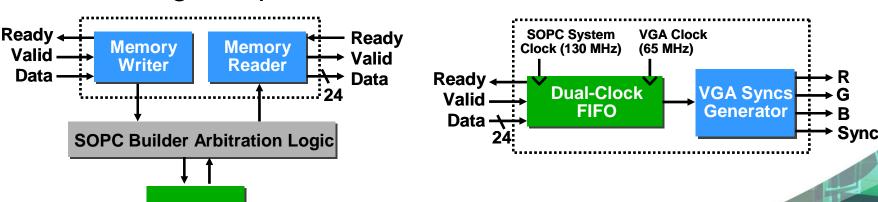

## **Triple Buffer and VGA Output**

- Allows inputs and output to run asynchronously and at different frame rates

- Video output: 1,024 x 768 progressive at 30 frame/s

- VGA output: must run at least 60 fps

- HDL design, imported into SOPC Builder

**DDR**

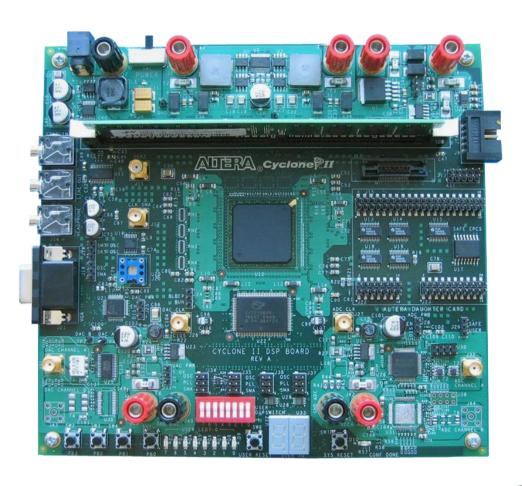

#### Video Development Kit, Cyclone II Edition

- Device: EP2C70

- Bundled software:

- Quartus II development kit edition

- DSP Builder

- MATLAB/Simulink evaluation software

- Altera OpenCore<sup>®</sup> Plus evaluation IP

- Includes video input daughter card

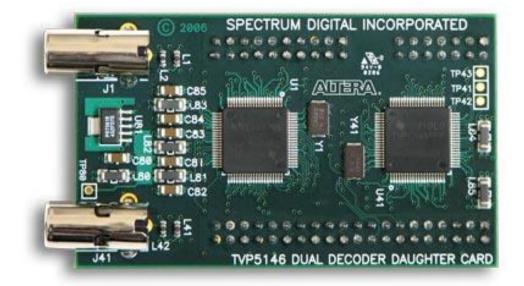

## Video Input Daughter Card

#### ■ Features:

- Dual composite video inputs (NTSC & PAL)

- Compatible with other Altera development boards that feature a Santa Cruz connector

#### **Download to Hardware**

- Resource utilization

- 9,500 logic elements, 48 M4K, 11 multipliers

- Fits in EP2C15 device

- Program Video Development Kit, Cyclone II Edition

- Hardware debug

- JTAG/SignalTap® logic analyzer

#### **Altera Video Solutions**

Design Software DSP Builder SOPC Builder

> Support Tools

Video IP Suite \$995

Intellectual Property (IP) Video Dev. Kits

- Daughter Card \$195

- •Cyclone II \$1,095

- •Stratix II GX \$4,995

Development Kits Video Processing

Reference Designs

Partner IP and Design Services

Altera Training

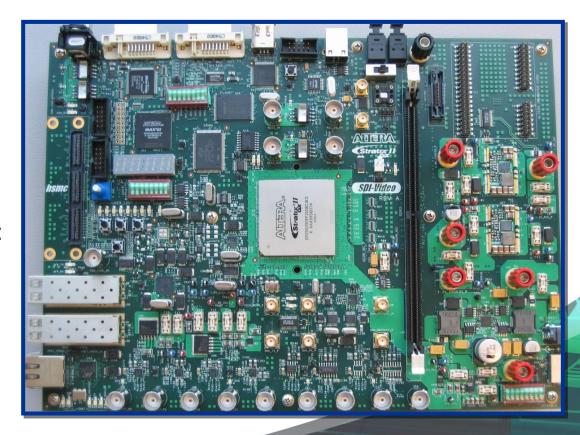

# Audio Video Development Kit, Stratix II GX Edition

- Device: EP2SGX90

- Video interfaces:

- 4 SDI/HD-SDI channels

- DVI

- Audio interfaces:

- AES3/EBU, SPDIF

- High-speed data interfaces:

- ASI

- FireWire (IEEE1394)

- USB 2.0

- 10/100/1000 Ethernet

- Bundled with SDI and video processing

reference design

### **Get Started Now**

| Product                                                     | Description                                                                                   | Ordering<br>Code      | Price   |

|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-----------------------|---------|

| Video and Image<br>Processing Suite                         | 9 video and image processing IP cores                                                         | IPS-VIDEO             | \$995   |

| Video<br>Development Kit,<br>Cyclone II Edition             | Cyclone II DSP board + video input daughtercard                                               | DK-VIDEO-<br>2C70N    | \$1,095 |

| Video Input<br>Daughter Card                                | 2 composite video inputs<br>(NTSC/PAL Support)                                                | DC-VIDEO-<br>TVP5146N | \$195   |

| Audio Video<br>Development Kit,<br>Stratix II GX<br>Edition | Stratix II GX video board with ASI, SDI, DVI, Gigabit Ethernet, FireWire, USB2.0, S/PDIF, AES | DK-VIDEO-<br>2SGX90N  | \$4,995 |