# Efficient System-Level DSP Design Flow with WiMAX DUC and DDC Case Study

# Agenda

- FPGA in digital signal processing (DSP) applications overview

- System-level design tools for Altera<sup>®</sup> FPGAs

- Overview

- Introduction to DSP Builder

- DSP Builder design flow walkthrough

- Case study: WiMAX digital upconverter (DUC) and digital downconverter (DDC) design

# **FPGA in DSP Applications**

Automotive

Communications

Consumer

Industrial

Test and Measurement Military

3

**Broadcast**

Medical

© 2006 Altera Corporation

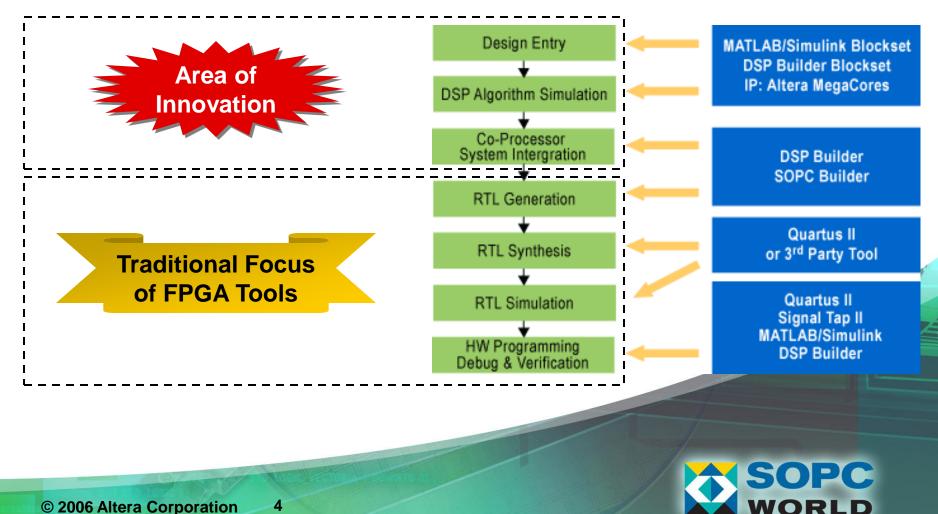

# **DSP Design Flow in FPGA**

# **Altera System-Level Design Tools**

**IP Integration**

System Integration

Software Development

# What is DSP Builder?

Start |

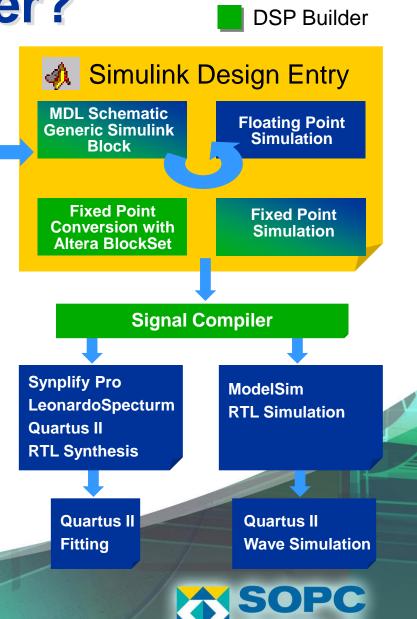

- Interface between Quartus II and MATLAB/Simulink

- Library add-on to Simulink

- Altera blockset

- Library of fixed-point Simulink functions

- Uses double precision

- Altera DSP IP

- OpenCore Plus

- SignalCompiler utility

- Converts between Simulink and Altera domain

- Hardware debug

- Hardware in the loop (HIL)/ SignalTap<sup>®</sup> logic analyzer

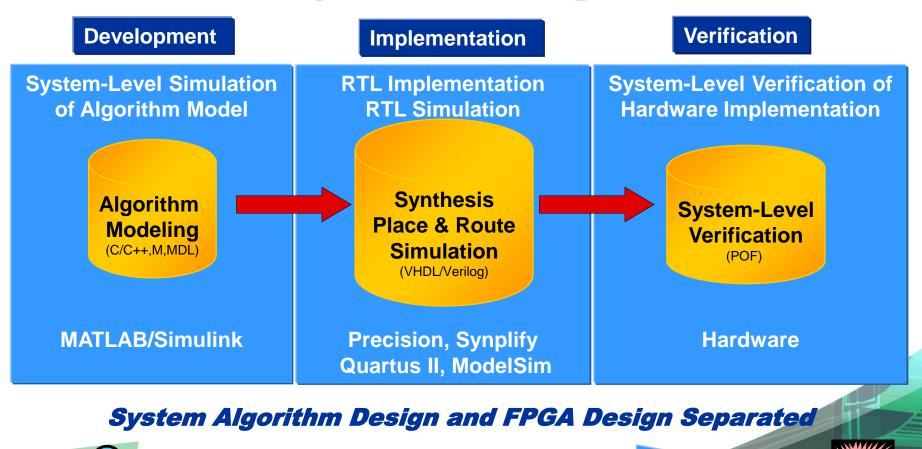

# **Traditional System Design Tool Flow**

© 2006 Altera Corporation

# **DSP Builder - Simulink Design Flow**

# **DSP Builder Features**

- Automatic generation of VHDL design from a MATLAB/Simulink representation

- Automatic generation of VHDL testbench

- Captures stimulus from Simulink, writes testbench

- HDL import

- Reads in design: Verilog or VHDL, or Quartus II project

- Creates Simulink simulation model

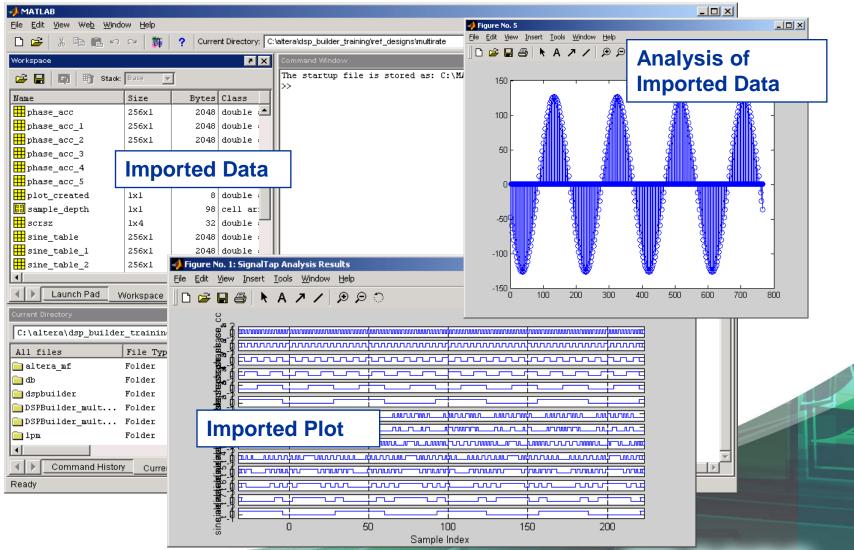

- SignalTap embedded logic analyzer

- Captures internal data and it into MATLAB

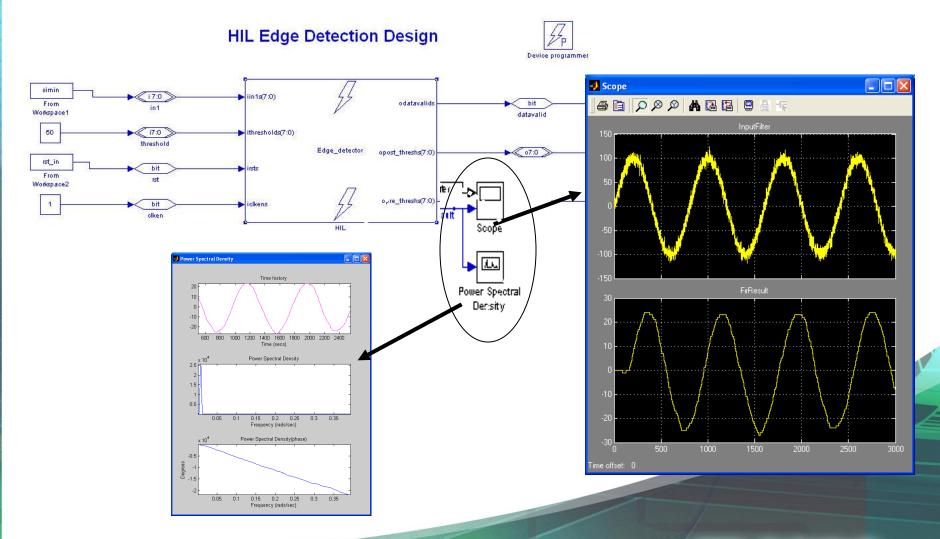

- HIL testing

- Pass vectors to/from board

# **DSP Builder Benefits**

For hardware engineer

- Extends RTL analysis and debug capabilities to systemlevel tool

- Access to MATLAB data formatting

- Access to a large library of Simulink models

- Speeds up simulation run time

- Enables IP evaluation at system level

- For system-level engineer

- Allows rapid prototyping with minimal PLD expertise

- Provides easy access to hardware evaluation

- Extends floating-point to fixed-point system analysis

# **DSP Builder Design Flow**

### Matlab/Simulink Domain (C+ System Analysis)

### VHDL Domain (Implementation/Simulation)

# **Design Flow Overview**

- 1) Create design in Simulink using Altera libraries

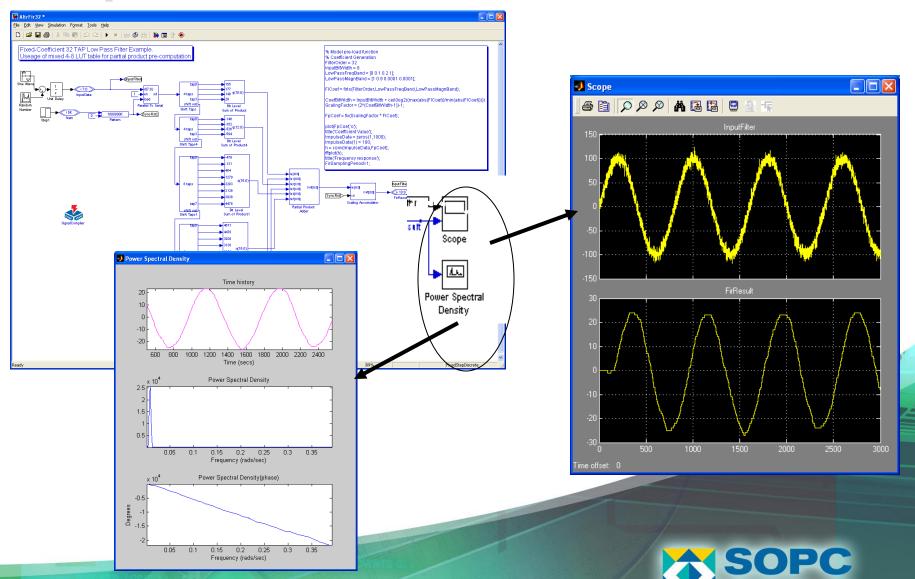

- 2) Simulate in Simulink

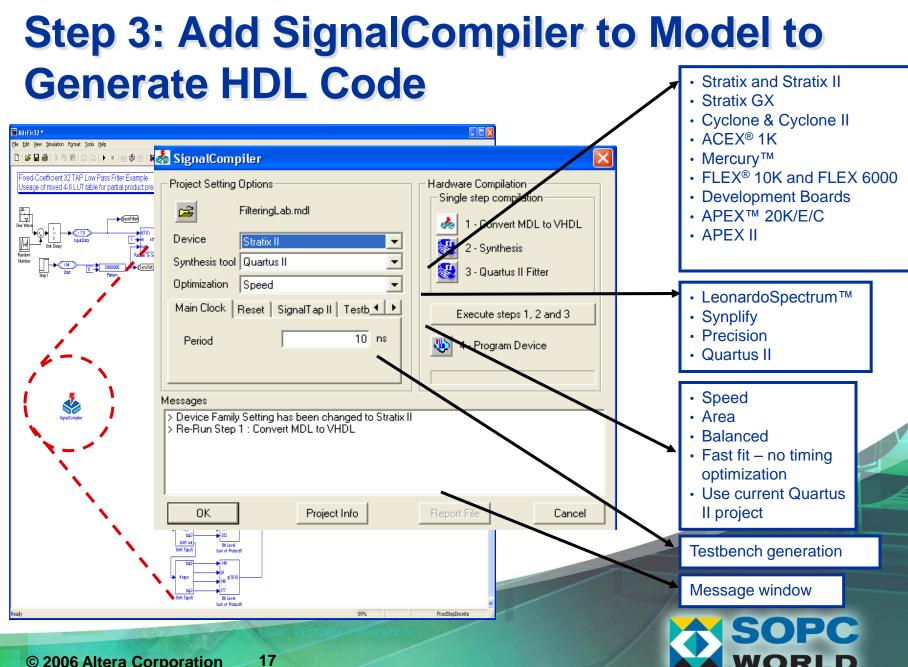

- 3) Add SignalCompiler to model

- 4) Create HDL code and generate testbench

- 5) Perform RTL simulation

- 6) Synthesize HDL code and place and route

- 7) Program device

- Verify hardware: SignalTap logic analyzer/HIL

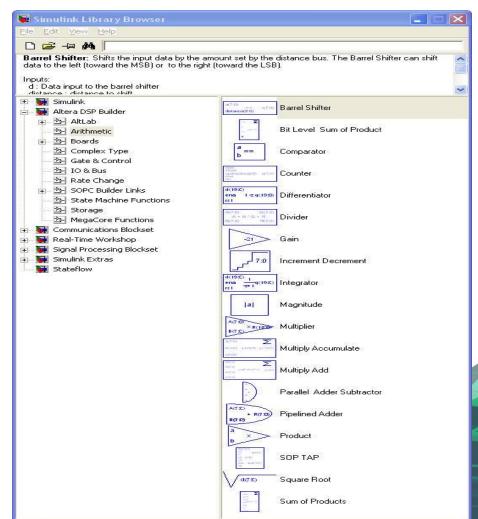

# **Altera DSP Builder Libraries**

Ready

- AltLab

- Arithmetic

- Boards

- Complex type

- Gate and control

- I/O and bus

- Rate change

- SOPC Builder links

- State machine functions

- Storage

- MegaCore functions

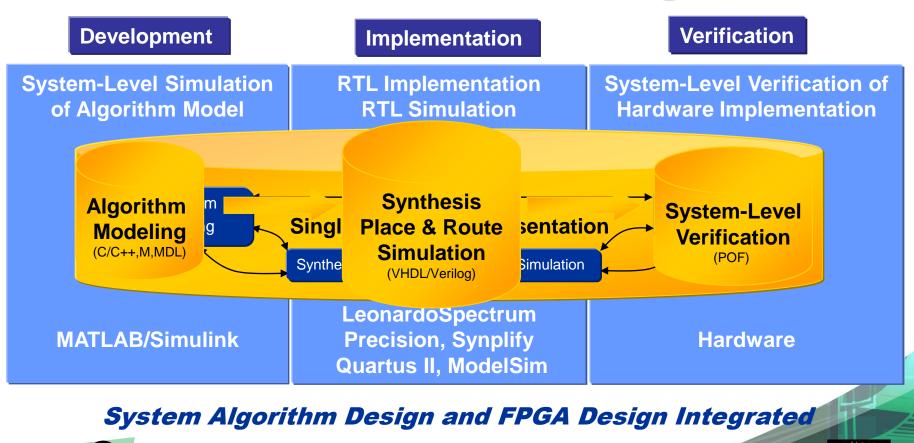

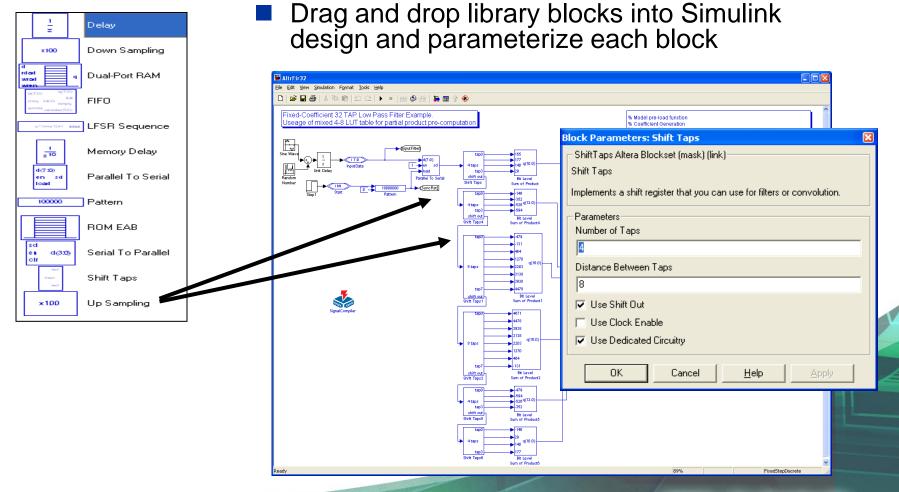

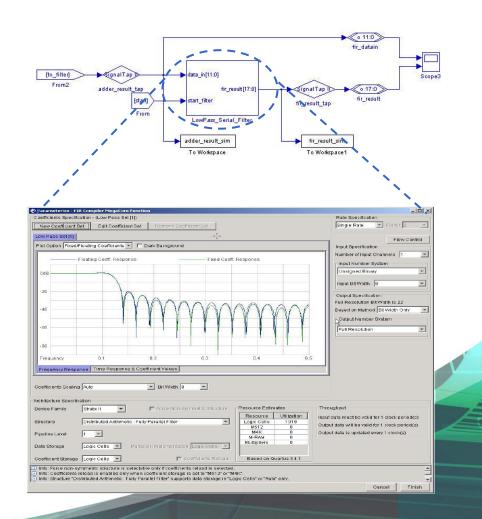

### Step 1: Create Design in Simulink Using Altera Libraries

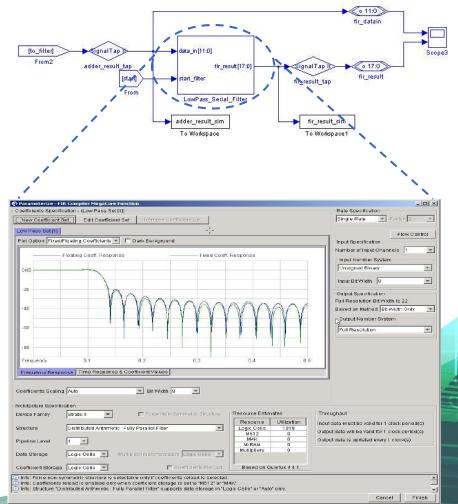

### Parameterization of IP MegaCore Functions

| 👿 Simulink Library Browser                                                 |              |                                                                                                                                        |

|----------------------------------------------------------------------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------|

| Eile Edit <u>View</u> Help                                                 |              |                                                                                                                                        |

| D 🚘 -14 🚧                                                                  |              | [to_filter] From2                                                                                                                      |

| fir_compiler: MegaCoreAltr/fir_compiler                                    |              | adder                                                                                                                                  |

| 🗈 🙀 Simulink<br>🖃 🙀 Altera DSP Builder                                     | csc          |                                                                                                                                        |

| ·····································                                      | fft          | Parameterize - FIR Compiler Mege     Coefficients Specification - d.ov/ Pasi     New Coefficient Set     Edit Coe     Low Pace Set [1] |

| ·····································                                      |              | Piol Option Fitzed # loading Coefficie                                                                                                 |

| ····· 참· IO & Bus<br>····································                  | nco          | -20                                                                                                                                    |

| → 公 SOPC Builder Links → State Machine Functions → Storage                 | Reed_Solomon | -00<br>-80<br>Frequency 0.1                                                                                                            |

| MegaCore Functions                                                         | viterbi      | Coefficients Scaling Auto                                                                                                              |

| <ul> <li>Real-Time Workshop</li> <li>Signal Processing Blockset</li> </ul> |              | Architecture Specification<br>Device Family Etrats II<br>Structure Distributed Arth                                                    |

| 💼 🙀 Simulink Extras                                                        |              | Pipeline Level 1<br>Data Storage Logic Cells                                                                                           |

| Stateflow                                                                  |              | Coempiont Storage Logic Cells                                                                                                          |

| Ready                                                                      |              |                                                                                                                                        |

# **Step 2: Simulate in Simulink**

WORLD

© 2006 Altera Corporation

© 2006 Altera Corporation

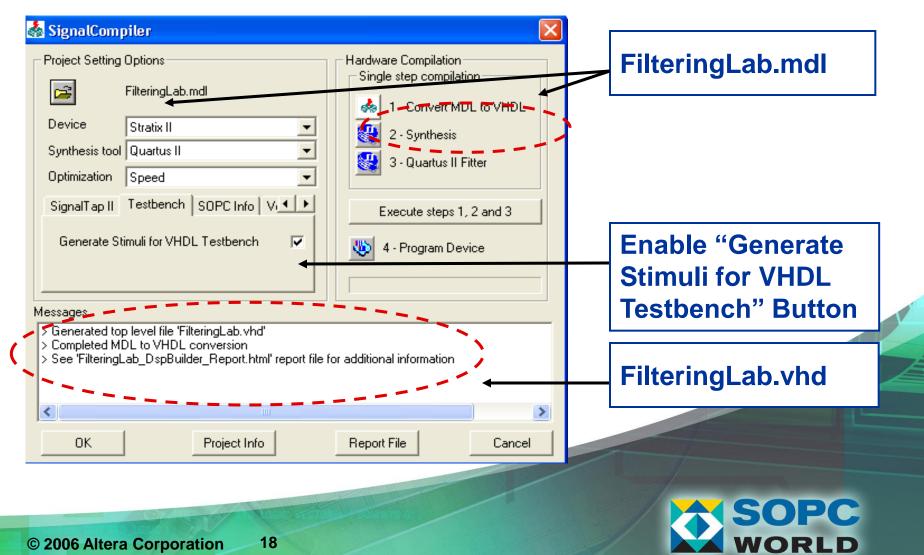

# Step 4: Create HDL Code and Generate Testbench

### **HDL Code Generation**

library ieee; use ieee.std\_logic\_1164.all; use ieee.std logic signed.all;

#### library dspbuilder; use dspbuilder.dspbuilderblock.all;

library lpm;

#### use lpm.lpm\_components.all;

#### Entity FilteringLab is Port(

| clock        |   | in std_logic;                      |

|--------------|---|------------------------------------|

| sclrp        |   | in std logic:='0';                 |

| iSW3s        | : | in std logic vector (7 downto 0);  |

| clk out1     |   | out std logic;                     |

| oLED1s       |   | out std logic;                     |

| ofir datains |   | out std logic vector(11 downto 0); |

| ofir_results | : | out std_logic_vector(17 downto 0)  |

|              |   |                                    |

#### ); end FilteringLab;

#### architecture aDspBuilder of FilteringLab is

signal SAfir\_datain0 : std\_logic\_vector(11 downto 0); signal sclr : std\_logic:="0';

#### --Using PLL to drive pin Y3 (DAC clock source)

| 77) | inclk0 |   | IN STD LOGIC ;  |

|-----|--------|---|-----------------|

|     | c0     | : | OUT STD_LOGIC); |

#### end component ;

signal board clk out int : std logic;

| signal | AOW         |   | :   | <pre>std_logic_vector(7 downto 0);</pre>  |

|--------|-------------|---|-----|-------------------------------------------|

| signal | A1W         |   |     | std_logic;                                |

| signal | A2W         |   | :   | std_logic;                                |

| signal | A3W         |   | :   | <pre>std_logic_vector(12 downto 0);</pre> |

| signal | A4W         |   |     | std_logic;                                |

| signal | ASW         |   | :   | <pre>std_logic_vector(13 downto 0);</pre> |

| signal | A6W         |   | :   | <pre>std_logic_vector(17 downto 0);</pre> |

| signal | A7W         |   | :   | <pre>std_logic_vector(12 downto 0);</pre> |

| signal | ASU         |   |     | <pre>std_logic_vector(12 downto 0);</pre> |

| signal | A9W         |   | :   | <pre>std_logic_vector(13 downto 0);</pre> |

| signal | A1OW        |   | :   | <pre>std_logic_vector(17 downto 0);</pre> |

| signal | A11W        |   | :   | <pre>std_logic_vector(12 downto 0);</pre> |

| signal | A12 U       |   |     | <pre>std_logic_vector(12 downto 0);</pre> |

| signal | A13 U       |   | :   | std_logic;                                |

| signal | A14W        |   | :   | std_logic;                                |

| signal | A15W        |   |     | std_logic;                                |

| signal | A16U        |   |     | std_logic;                                |

| signal | A170        |   | :   | std_logic;                                |

| signal | ExtExtract4 | : | std | logic vector (7 downto 0);                |

#### -- SubSystem Hierarchy - Simulink Block "LowPass\_Serial\_Filter" component LowPass Serial Filter

portí

| clock       | : | in std logic ;                     |

|-------------|---|------------------------------------|

| sclr        | : | in std logic ;                     |

| iInputDatas | : | in std logic vector(11 downto 0) ; |

| iStarts     | : | in std logic;                      |

| oFirResults | : | out std logic vector(17 downto 0)  |

| );          |   |                                    |

#### end component ;

#### -- SubSystem Hierarchy - Simulink Block "SineWave\_Generator" component SineWave\_Generator port (

| ort( |                 |   |                                                |

|------|-----------------|---|------------------------------------------------|

|      | clock           | : | in std_logic ;                                 |

|      | sclr            | : | in std_logic ;                                 |

|      | iStarts         | : | in std_logic ;                                 |

|      | osin_833_33kHzs | : | <pre>out std_logic_vector(12 downto 0) ;</pre> |

|      | osin_83_33kHzs  | ÷ | out std_logic_vector(12 downto 0)              |

|      | );              |   |                                                |

|      |                 |   |                                                |

#### end component ;

#### Begin

assert (1<0) report altversion severity Note;

#### -- Output - I/O assignment from Simulink Block "LED1" oLED1s <= &14W; ofir\_datains <= SAfir\_datainO;

-- Output - I/O assignment from Simulink Block "fir\_result" ofir\_results <= A10W; sclr <= sclrp;

-- Input - I/O assignment from Simulink Block "iSW3s" AOW <= iSW3s;

#### -- Bit Extraction - Simulink Block "ExtractBit"

| ExtExtract4 | <= | AOW;                       |

|-------------|----|----------------------------|

| A1W         | <= | <pre>ExtExtract4(0);</pre> |

| sclr u5     | <= | A16W or sclr;              |

| sclr u6     | <= | A17W or sclr;              |

| Simulin  | C Block "VCC" |      |

|----------|---------------|------|

| A15W     | <=            | '1'; |

| Simulini | C Block "GND" |      |

| A16W     | <=            | '0'; |

A100 \-

-- Simulink Block "GND1"

# **DSP Builder Report File**

| Lists all converted blocks                                                                                                    | Signal Compiler Report File                                                                                                             |

|-------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Port widths</li> </ul>                                                                                               | DSP Builder Report File for filter_ex_1_5.mdl                                                                                           |

| <ul> <li>Sampling frequencies</li> </ul>                                                                                      | Project Setting                                                                                                                         |

| <ul> <li>Warnings and messages</li> </ul>                                                                                     | Device Family Stratix II<br>Synthesis Tool Quartus II<br>Optimization Speed                                                             |

| Signal Compiler Report File                                                                                                   | Date         Tuesday, December 14, 2004           Time         16:54:55           Version         3.0.0 b23                             |

| Analysis & Synthesis report for filter_ex_1_5<br>Tue Dec 14 16:55:07 2004<br>Version 4.2 Build 156 11/29/2004 SJ Full Version | Compilation<br>Convert Mdl to VHDL : PASCED                                                                                             |

| Signal Compiler Report File                                                                                                   | Synthesis     : PASSED     filter     ex     1     5.map.rpt       Quartus II Fitter     : DASSED     filter     ex     1     5.fit.rpt |

| Fitter report for filter_ex_1_5<br>Tue Dec 14 16:55:36 2004<br>Version 4.2 Build 156 11/29/2004 SJ Full Version               | Timing Analyzer report : <u>filter ex 1 5.fit.tan</u>                                                                                   |

| Signal Compiler Report File                                                                                                   | Resource     Usage       Total combinational functions     105       ALUT usage by number of inputs     105                             |

| Timing Analyzer report for filter_ex_1_5<br>Tue Dec 14 16:55:41 2004<br>Version 4.2 Build 156 11/29/2004 SJ Full Version      | 7 input functions 0                                                                                                                     |

|                                                                                                                               | SOPC                                                                                                                                    |

| © 2006 Altera Corporation 20                                                                                                  | WORLD                                                                                                                                   |

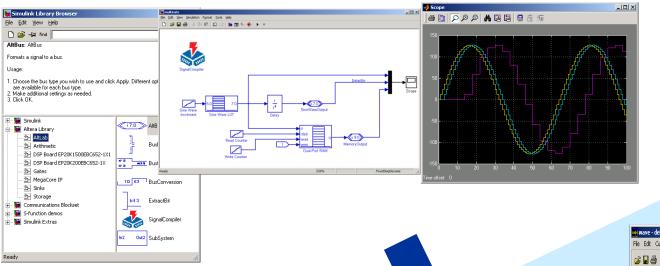

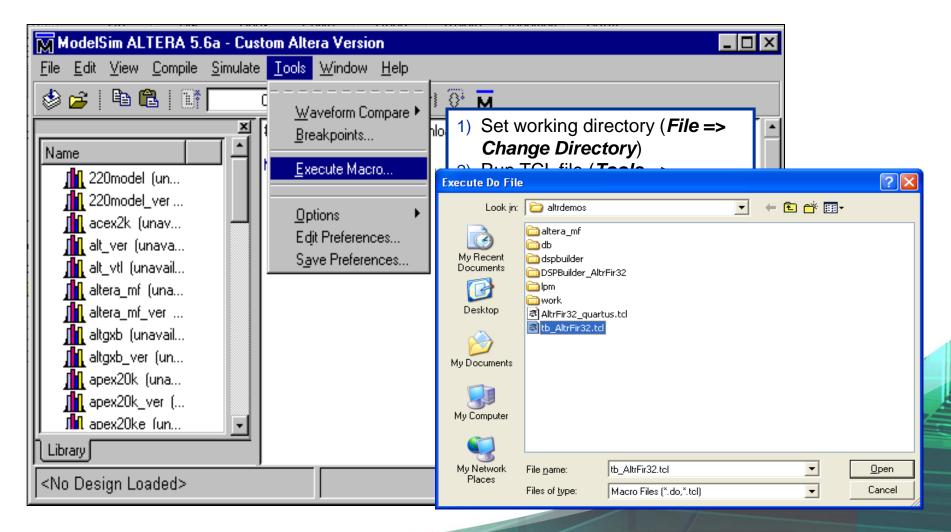

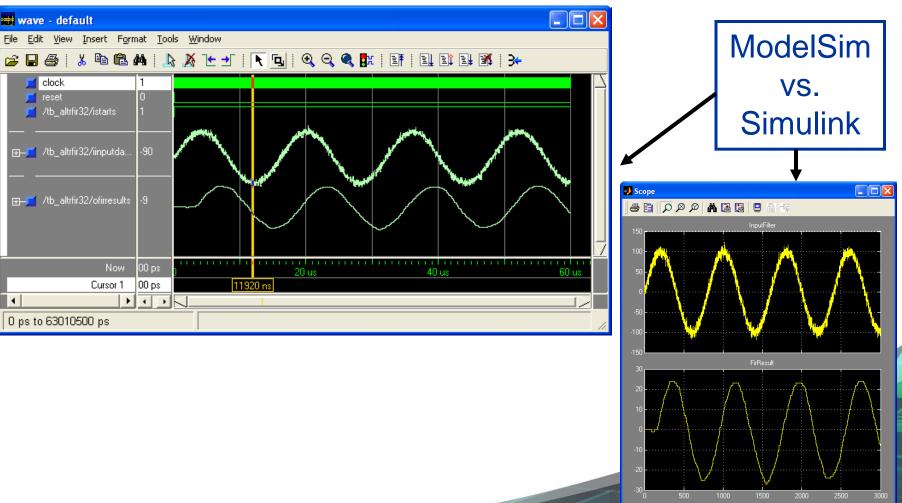

# Step 5: Perform RTL Simulation (ModelSim)

### **Perform Verification**

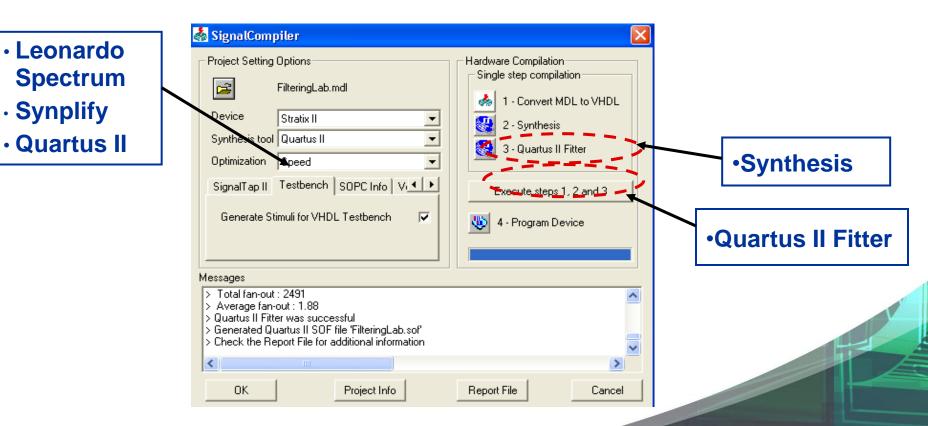

# Step 6: Synthesize HDL and Place and Route

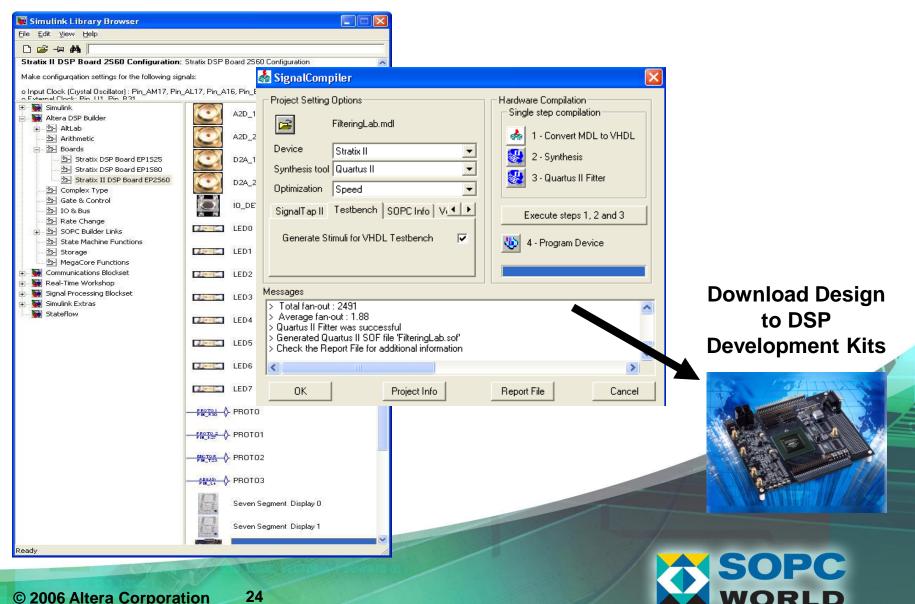

### **Step 7: Program Device**

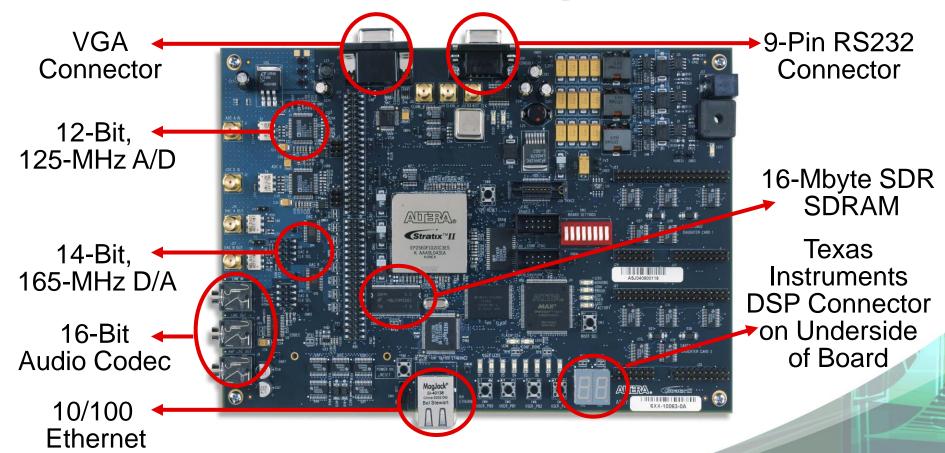

# **Stratix II DSP Development Board**

### Available with EP2S60 or EP2S180 Device

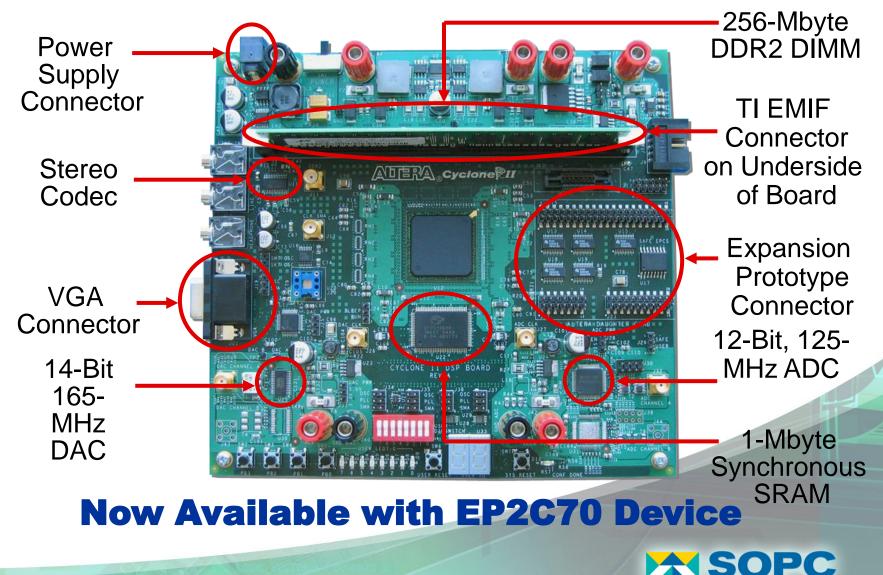

# **Cyclone II DSP Development Board**

VORLD

© 2006 Altera Corporation 26

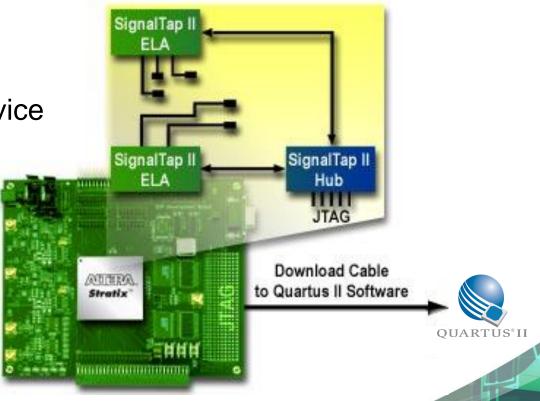

# Step 8: SignalTap II Logic Analyzer

- Embedded logic analyzer (ELA)

- Downloads into device with design

- Captures state of internal nodes

- Uses JTAG for communication

# SignalTap II Logic Analyzer

# Hardware in Loop (HIL)

# **Design Flow Review**

- 1) Create design in Simulink using Altera libraries

- 2) Simulate in Simulink

- 3) Add SignalCompiler to model

- 4) Create HDL code and generate testbench

- 5) Perform RTL simulation

- 6) Synthesize HDL code and place and route

- 7) Program device

- Verify hardware: SignalTap logic analyzer HIL

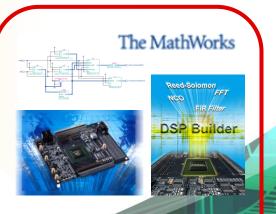

# **Altera DSP Development Kits**

Reed-Solomon

NCO

FFT

FIR Filter

DSP Builder

Version

# WiMAX DUC and DDC Design Case Study

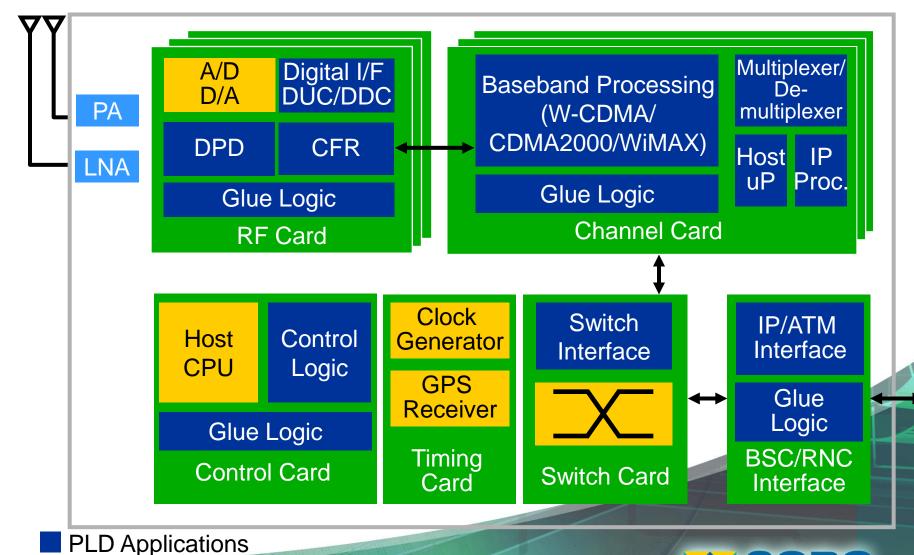

# **Base Station Architecture Overview**

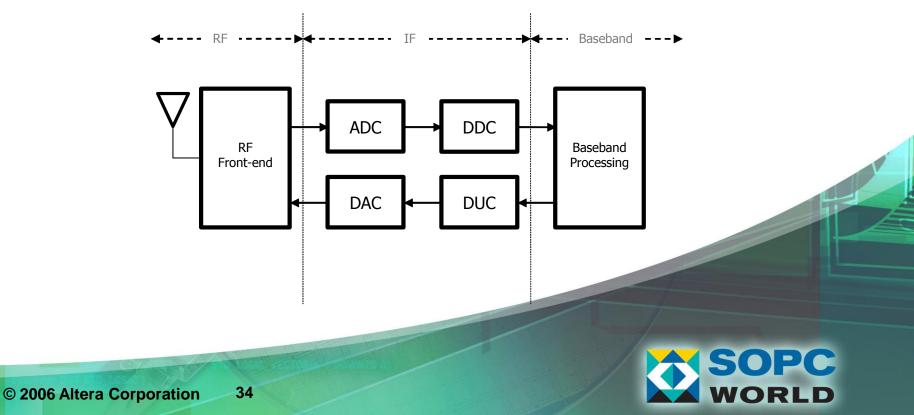

# **Reference Design Overview**

### DUC/DDC

- Provides the link between digital baseband and analog RF front end of generic transceiver

- High throughput signal processing required makes FPGA ideal platform

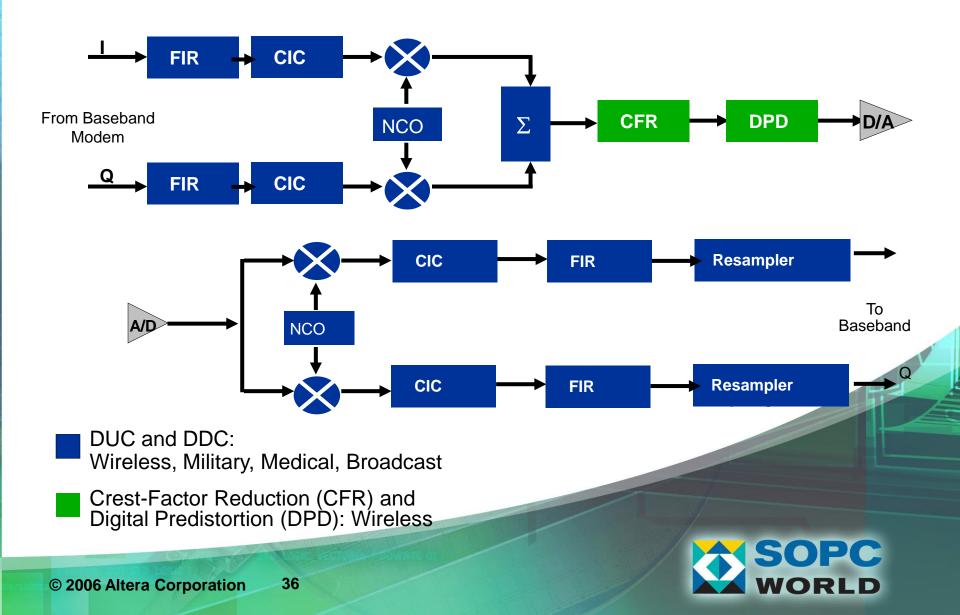

# WiMAX DUC and DDC Designs

- Compliant to the draft WiMAX standard (IEEE 802.16)

- Multi-channel filter design for low cost

- Support for multiple transmit and receive antenna configurations

- Easily modifiable to support scalable channel bandwidths

- Uses DSP Builder methodology

- Backed up by DSP Builder-ready, highly parameterizable IP MegaCore functions

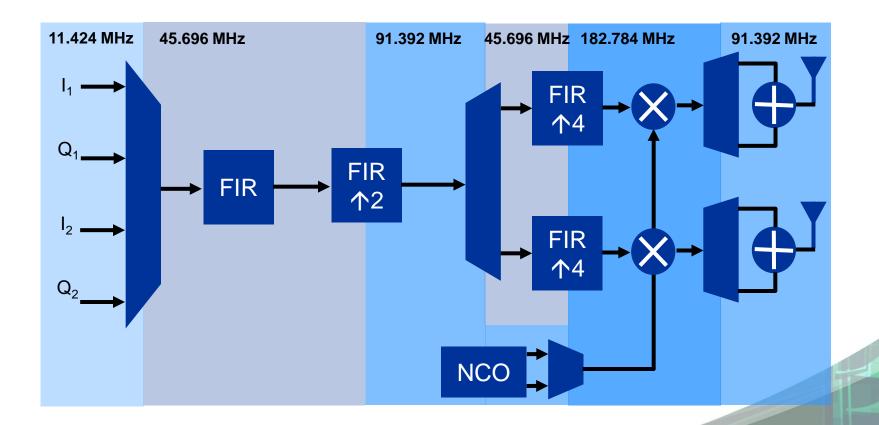

# **DUC and DDC High-Level Block Diagrams**

#### **DSP Builder Implementation: IP MegaCore Library**

| Compiler: MegaCoreAltr/fir compiler |              |

|-------------------------------------|--------------|

|                                     |              |

|                                     |              |

| 🙀 Simulink<br>🙀 Altera DSP Builder  | csc          |

| HILE Altera DSP Builder             |              |

| 2- Arithmetic                       | fft          |

| 🖅 🎰 Boards                          |              |

| Complex Type                        | fir_compiler |

| 🔤 🏧 Gate & Control                  |              |

| IO & Bus                            | nco          |

|                                     |              |

|                                     | Reed_Solomon |

|                                     |              |

| MegaCore Functions                  | viterbi      |

| Sommunications Blockset             |              |

| Deal-Time Workshop                  |              |

| Signal Processing Blockset          |              |

| - 🖬 Simulink Extras                 |              |

#### *IP Can Be Added to the Library Separately*

#### **DSP Builder Implementation: Digital Intermediate Frequency (IF) Library**

| 👿 Simulink Library Browser                                                                                                |                          |

|---------------------------------------------------------------------------------------------------------------------------|--------------------------|

| File Edit View Help                                                                                                       |                          |

|                                                                                                                           |                          |

| FFC: Frame Format Converter<br>Use a quoted string or a Matlab variable for each format fi<br>Example: 'Red, Green, Blue' | eld.                     |

|                                                                                                                           | FFC                      |

| Model Verification                                                                                                        | FrameFormatDecimation    |

|                                                                                                                           | FrameFormatInterpolation |

|                                                                                                                           | TwoChannelDemux          |

|                                                                                                                           | TwoChannelMux            |

| 🗈 🙀 Altera DSP Bailder                                                                                                    |                          |

| Multichannel                                                                                                              |                          |

| 🕂 🙀 Altera Wireless                                                                                                       |                          |

|                                                                                                                           |                          |

| District System Toolbox                                                                                                   |                          |

| Image Acquisition Toolbox                                                                                                 |                          |

|                                                                                                                           |                          |

| Ready                                                                                                                     |                          |

38

- Adapters

- Provide input/output interface to finite impulse response (FIR) filter

- Multichannel

- Frame format converter

- Decimation

- Interpolation

- Multiplexer

- Demultiplexer

- Rounding

### **DUC With 2 Antennas Design Architecture**

#### **Timeshare DUC Hardware Between Antennas**

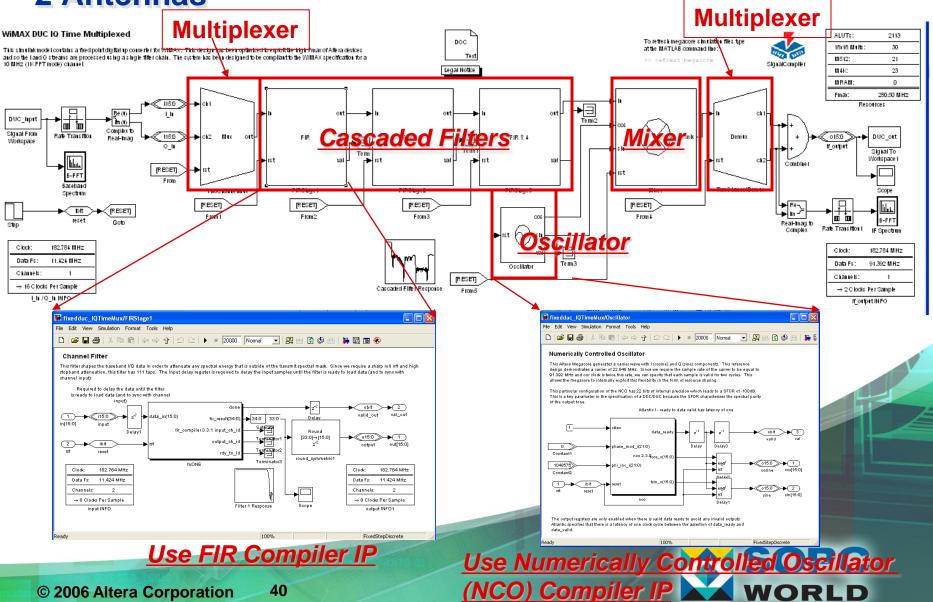

# DSP Builder Implementation: DUC Example Design With 2 Antennas

### Simulation

🛃 Figure 1

WORLD

41

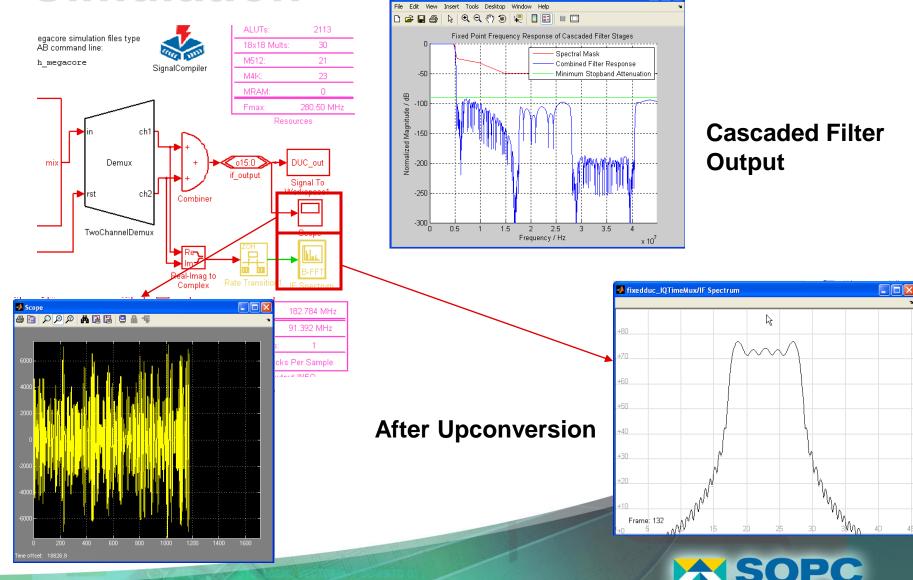

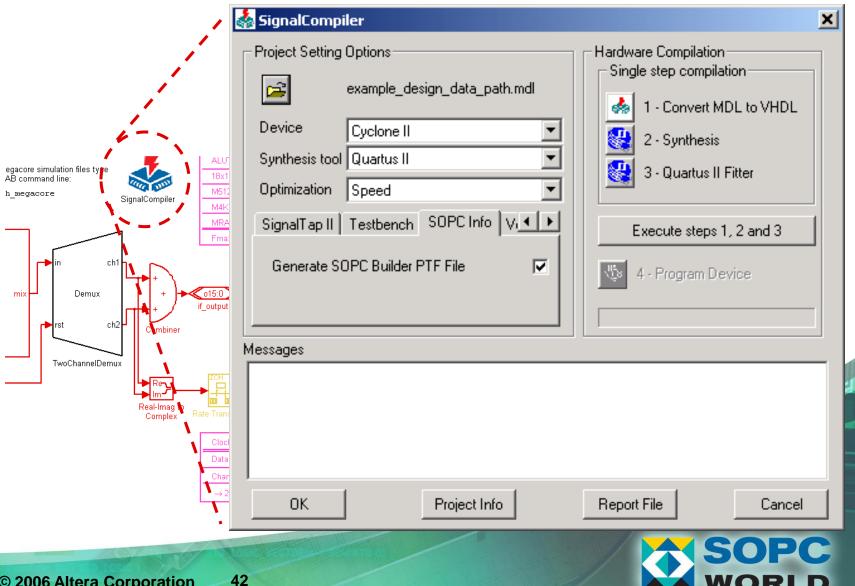

### **Convert to VHDL: SignalCompiler**

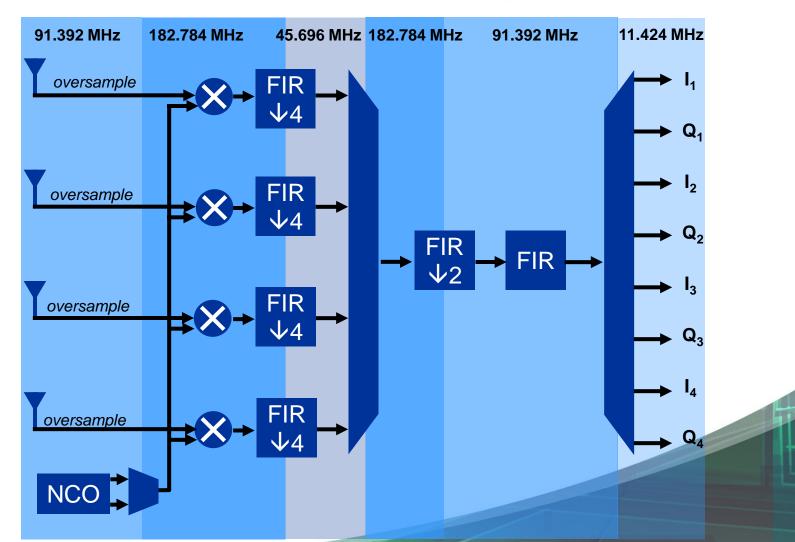

### **DDC With 4 Antennas Design Architecture**

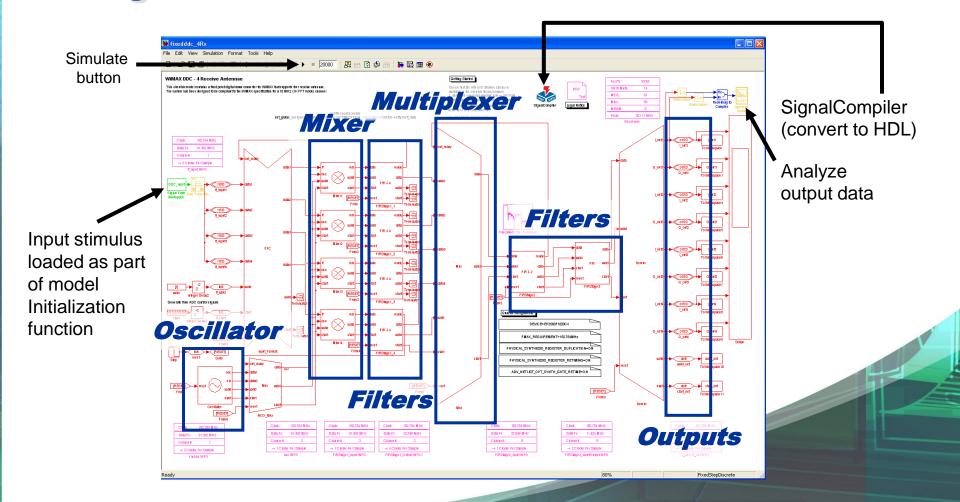

#### DSP Builder Implementation: DDC Example Design With 4 Antennas

44

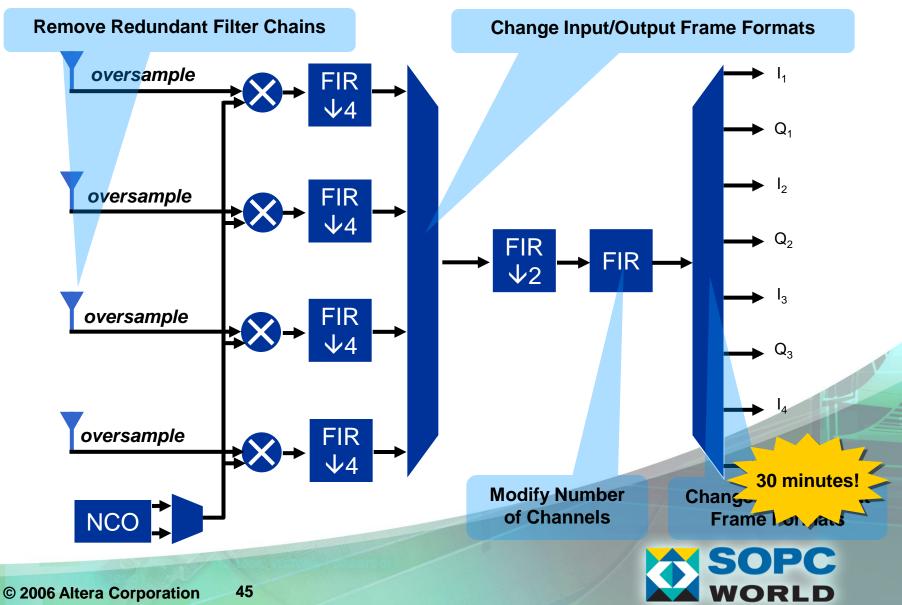

### **2xRx DDC Architecture**

## **DUC and DDC Synthesis Results**

| ALUTs                          | M512 | M4K | MRAM | Multipliers<br>18x18 | f <sub>max</sub><br>MHz |  |

|--------------------------------|------|-----|------|----------------------|-------------------------|--|

| DUC Time Multiplexed IQ Design |      |     |      |                      |                         |  |

| 2,113                          | 21   | 23  | 0    | 30                   | 281                     |  |

| DUC 2 Antenna Design           |      |     |      |                      |                         |  |

| 4,229                          | 21   | 56  | 0    | 55                   | 193                     |  |

| DDC Time Multiplexed IQ Design |      |     |      |                      |                         |  |

| 2,488                          | 19   | 22  | 0    | 25                   | 293                     |  |

| DDC 4 Antenna Design           |      |     |      |                      |                         |  |

| 10,753                         | 67   | 69  | 0    | 74                   | 201                     |  |

Highly Optimized and Cost Efficient Designs! More Information at www.altera.com

## Summary

#### DSP Builder tool improves productivity

- System-level DSP design and FPGA design integrated into one platform: Simulink

- WiMAX DUC and DDC application example

- DSP Builder-based IQ time multiplexed and multiantenna designs

- Use FIR compiler and NCO compiler IP

- Design methodology significantly reduces the development time for different standards

- Highly optimized and cost-efficient designs

## Thank You Q & A