# **COMPANY CONFIDENTIAL**

NOTICE TO ALL PERSONS RECEIVING THIS DOCUMENT CONFIDENTIAL: Reproduction forbidden without the specific written permission of Atari, Inc. Sunnyvale, California. This document is only conditionally issued and neither receipt nor possession thereof confers or transfers any right in, or license to use the subject matter of the document or any design or technical information shown thereon, nor any right to reproduct this document or any part thereof, except for manufacture under the corporation's written license.

| CO20577      |                |            |                     | Mike Stevens         | 7/22/83 |                                            | ATARI, INCORPO |          |

|--------------|----------------|------------|---------------------|----------------------|---------|--------------------------------------------|----------------|----------|

| REVISIONS    |                |            | SYSTEMS ENGINEERING |                      | ATACI   | 275 GIBRALTAR DRIVE<br>SUNNYVALE, CA 94086 |                |          |

| DOC.<br>REV. | DEVICE<br>REV. | COMMENTS   | DATE                | LOGICENGINEERING     | 8/11/63 | ATARI*<br>Semiconductor G                  | roup           | •        |

| A            | N/C            | See Page 2 |                     | CAD ENGINEERING      | 8/11/83 | CCIA                                       | INTSO          | <u> </u> |

|              |                |            |                     | Scagnote             | 8/11/83 |                                            |                |          |

|              |                |            | 1 6                 | ORIGINATING DIVISION |         | DOCUMENT NUMB                              | D020577        |          |

|              |                |            |                     | DIVISION APPROVAL    |         | PAGE 1                                     | of 90          | PAGES    |

### **REVISIONS**

# Description

This document was revised to REV A in order to reflect a change to the device pin-out from the preliminary CGIA specification. The device revision was not changed because the CGIA had not been released to ATARI vendors.

|                                        | COMPANY      | CO20577         | CGIA (NTSC)  |  |

|----------------------------------------|--------------|-----------------|--------------|--|

| ATA DI                                 | CONFIDENTIAL | DOCUMENT NUMBER |              |  |

| ATARI <sup>®</sup> Semiconductor Group |              | D020577         | PAGE 2 OF 90 |  |

# Table of Contents

| Section Description                              | Page      | Number   |

|--------------------------------------------------|-----------|----------|

|                                                  |           | •        |

| General Description                              |           | . 7      |

| Features                                         |           |          |

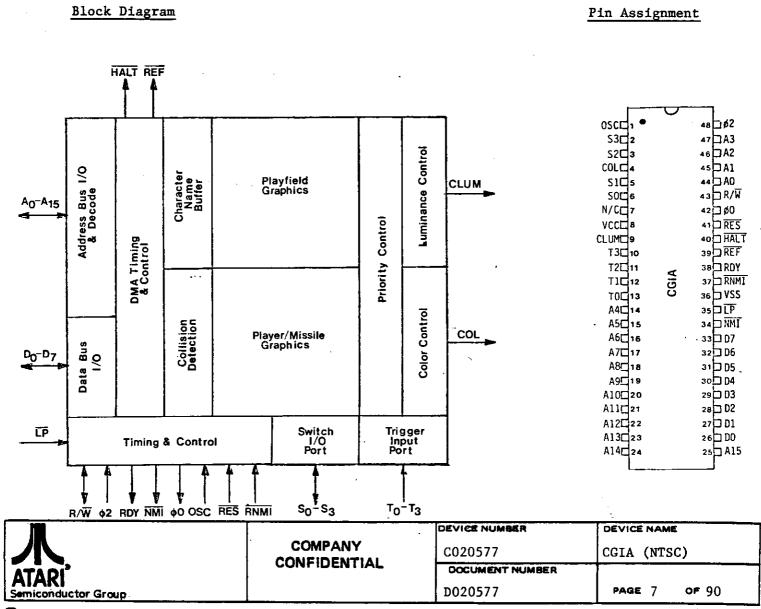

| CGIA Block Diagram                               |           | .7       |

| Pin Assignment                                   |           | 7        |

| Pin Description                                  | • • • • • | 8        |

| Introduction                                     |           | 11       |

| CGIA Functional Overview                         |           |          |

| Playfield Graphics (an overview)                 |           |          |

| Player/Missile Graphics (an overview)            |           |          |

| Graphics Mixing                                  |           |          |

| Object Collisions                                |           |          |

| Input/Output Functions                           | • • • • 1 | 12       |

| CGIA FUNCTIONAL DESCRIPTION                      |           | •        |

|                                                  |           |          |

| 1.0) Television Frame Timing                     | 1         | 13       |

| 2.0) THE DISPLAY LIST                            | 1         | 16       |

| 2.1) Display Instruction Format                  | 1         | 16       |

| 2.1) Display instruction Format                  |           | LO<br>LO |

|                                                  |           |          |

| ·                                                |           |          |

| 2.4) Simple Display List Example                 | • • • • 4 | 2.2      |

| 3.0) GRAPHICS MODES                              | 2         | 23       |

| 3.1) Character Map Graphics Modes                | 2         | 23       |

| 3.2) Graphics Modes 2 and 3                      |           |          |

| 3.3) Graphics Modes 4 and 5                      |           |          |

| 3.4) Graphics Modes 6 and 7                      |           |          |

| 3.4) Graphics Modes o and /                      | • • • • 4 | . 9      |

| 3.5) Bit Map Graphics Modes                      | 3         | 33       |

| 3.6) Graphics Modes 8,A,D and E                  | 3         | 33       |

| 3.7) Graphics Modes 9,B and C                    | 3         | 35       |

| 3.8) Graphics Mode F                             | 3         | 36       |

| 3.9) Special FunctionsMode F (GTIA Modes)        |           |          |

| 3.10) Player/Missile Graphics                    | 3         | 38       |

| 3.11) Creating Players and Missiles by Using DMA | 3         | 39       |

|                                                  |           |          |

|                     |                         | DEVICE NUMBER   | DEVICE NAME  |  |

|---------------------|-------------------------|-----------------|--------------|--|

| 八                   | COMPANY<br>CONFIDENTIAL | C020577         | CGIA (NTSC)  |  |

| ATARI*              | OOM IDENTIAL            | DOCUMENT NUMBER |              |  |

| Semiconductor Group |                         | D020577         | PAGE 3 OF 90 |  |

|                     |                         |                 | <del></del>  |  |

# Table of Contents

| Section                 | n Des        | cription    |                                         | Page Number       |                                         |                 |

|-------------------------|--------------|-------------|-----------------------------------------|-------------------|-----------------------------------------|-----------------|

| пубиля                  | ।<br>ਜਿਸ     | NCTIONS     |                                         |                   |                                         |                 |

| IIAKOWA                 | IKE PO       | HOTTONS     |                                         |                   |                                         |                 |

| 4.0)                    | CGIA         | Direct Men  | ory Access                              | • • • • • • • • • | • • • • • • • • • • • • • • • • • • • • | 42              |

|                         | 4.1)         | Display In  | struction DMA                           |                   |                                         | 42              |

|                         | 4.2)         |             | DMA                                     |                   |                                         |                 |

|                         | 4.3)         |             | sile DMA                                |                   |                                         |                 |

|                         | 4.4)         |             | Counting                                |                   |                                         |                 |

| 5.0)                    | RAM          | Refresh     | • • • • • • • • • • • • • • • • • • • • | •••••             | • • • • • • • • • • • • • • • • • • • • | 46              |

| 6.0)                    | Vide         | o Generatio | <u>n</u>                                |                   | • • • • • • • • • • • • • • • • • • • • | 48              |

|                         | 6.1)         | Monochrome  | Signal                                  |                   |                                         | 48              |

|                         | 00-,         |             | ontal Blank and Hor                     |                   |                                         |                 |

|                         |              |             | cal Blank and Verti                     |                   |                                         |                 |

|                         | 6.2)         |             | e Signal                                |                   |                                         |                 |

|                         |              |             | _                                       |                   |                                         |                 |

| 7.0)                    | Gene         | ral Purpose | I/O Functions                           | • • • • • • • •   | • • • • • • • • • • • • • • •           | 52              |

|                         | 7.1)         | Trigger In  | put Port (TT_)                          |                   |                                         | 52              |

|                         | 7.2)         | Switch I/O  | put Port $(T_0-T_3)$ Port $(S_0-S_3)$   |                   |                                         | 52              |

| SPECIA                  | L FUN        | CTIONS      | 0 3                                     |                   |                                         |                 |

|                         |              |             |                                         |                   |                                         |                 |

|                         | 8.1)         |             | ority Control                           |                   |                                         |                 |

| 8.2) Object Collision I |              |             |                                         |                   |                                         |                 |

|                         | 8.3)<br>8.4) |             | g Vertical Position                     |                   |                                         |                 |

|                         | 8.5)         |             | g The CGIA Video Storizontal Sync       |                   |                                         |                 |

|                         | 8.6)         |             | le Interrupts                           |                   |                                         |                 |

|                         | 8.7)         |             | xternal Light Pen                       |                   |                                         |                 |

|                         | 8.8)         |             | st Functions                            |                   |                                         |                 |

| REGIST                  | ER DE        | SCRIPTION   | •                                       |                   |                                         |                 |

| 9.0)                    | Writ         | e-Only Regi | sters                                   |                   | • • • • • • • • • • • • • • • • •       | 57              |

|                         | 0.11         | 0           | MA 0 2                                  |                   |                                         | ~ •             |

|                         | 9.1)         |             | MA Control                              |                   |                                         |                 |

|                         | 9.2)<br>9.3) |             | Display Control                         |                   |                                         |                 |

|                         | 9.3)         |             | st Pointer Scrolling                    |                   |                                         |                 |

|                         | 9.4)         |             | crolling                                |                   |                                         |                 |

|                         | 9.6)         |             | sile Base Address                       |                   |                                         |                 |

|                         | 9.7)         |             | Base Address                            |                   |                                         |                 |

|                         | 9.8)         |             | orizontal Blank Syn                     |                   |                                         |                 |

|                         |              |             |                                         | DEVIC             | 2 NUMBER                                | DEVICE NAME     |

|                         |              |             | COMPANY                                 | 000               | 0577                                    | 00T1 (********) |

|                         |              |             | CONFIDENTIAL                            |                   | 0577<br>UMENT NUMBER                    | CGIA (NTSC)     |

| RĪ                      |              |             |                                         | 000               | omeni nombek                            | 1               |

| ductor Grou             | D.           |             |                                         | D02               | 0577                                    | PAGE 4 OF       |

# Table of Contents

| Section Description                                | Page Number |

|----------------------------------------------------|-------------|

| 9.9) Enable Non-Maskable Interrupts                | 61          |

| 9.10) Reset Non-Maskable Interrupts                | 62          |

| 9.11) Player/Missile Horizontal Position           | 62          |

| 9.12) Player/Missile Size                          |             |

| 9.13) Player/Missile Graphics                      |             |

| 9.14) Color/Luminance Control                      | 65          |

| 9.15) Priority Control                             |             |

| 9.16) Fifth Player Enable                          |             |

| 9.17) Multiple Color Player Enable                 | 68          |

| 9.18) Playfield Mode Control                       | 68          |

| 9.19) Player/Missile Vertical Delay                |             |

| 9.20) Graphics Control                             |             |

| 9.21) Collision Register Clear                     | 69          |

| 10.0) Read-Only Registers                          | 70          |

| 10.0) Read-Only Registers                          | /0          |

| 10.1) Vertical Line Counter                        | 70          |

| 10.2) Horizontal and Vertical Light Pen Registers  |             |

| 10.3) Non-Maskable Interrupt Status                | 71          |

| 10.4) Missile to Playfield Collisions              |             |

| 10.5) Player to Playfield Collisions               |             |

| 10.6) Missile to Player Collisions                 |             |

| 10.7) Player to Player Collisions                  |             |

| 10.8) Collisions (Special Conditions)              |             |

| 10.9) Trigger Input Latches                        | 73          |

| 10.10) Television Standards Register               |             |

| 10.11) Enable Test Functions                       | 73          |

| 11.0) Read/Write Registers                         | 74          |

| 11.1) CONSOL (Switch I/O Port) Read/Write Register | 74          |

| 12.0) CGIA Memory Map                              | 75          |

| ABSOLUTE MAXIMUM RATINGS                           | 76          |

| D.C. OPERATING CHARACTERISTICS                     | 76          |

| DYNAMIC OPERATING CHARACTERISTICS                  | 82          |

| TIMING DIAGRAMS                                    | 85          |

| CGIA Address Table                                 | 89          |

| 0040 4334                  |                            |              |

|----------------------------|----------------------------|--------------|

| ATARI COMPANY CONFIDENTIAL | C020577<br>DOCUMENT NUMBER | CGIA (NTSC)  |

| Semiconductor Group        | D020577                    | PAGE 5 OF 90 |

# Table of Illustrations

| Section Des | scription Page Number 1                             | ber |

|-------------|-----------------------------------------------------|-----|

| Figure 1)   | Television Screen Format                            |     |

| Figure 2)   | Display List Instruction Opcodes18                  |     |

| Figure 3)   | Vertical Scrolling Example                          |     |

| Figure 4)   | Character Map Display Mode Characteristics25        |     |

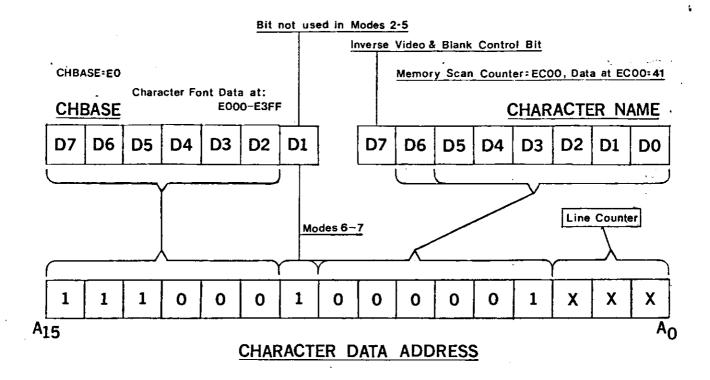

| Figure 5)   | Character Data Addressing Example26                 |     |

| Figure 6)   | Graphics Mode 3 Display Example27                   |     |

| Figure 7)   | Character Data and Name Byte Organization31,32      |     |

| Figure 8)   | Bit Map Display Mode Characteristics34              |     |

| Figure 9)   | Player/Missile Graphics Data Addressing41           |     |

| Figure 10)  | Graphics DMA Sources44                              |     |

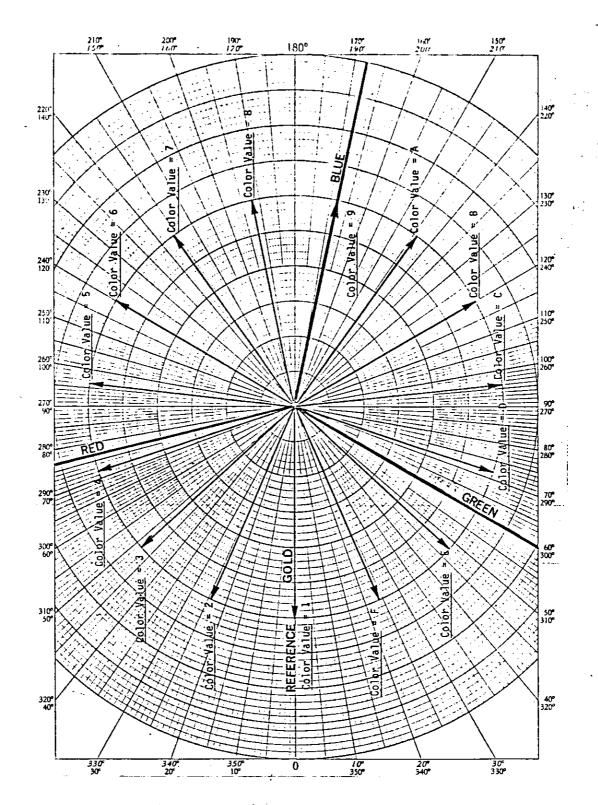

| Figure 11)  | Phase Angle Plot of Color Output Values51           |     |

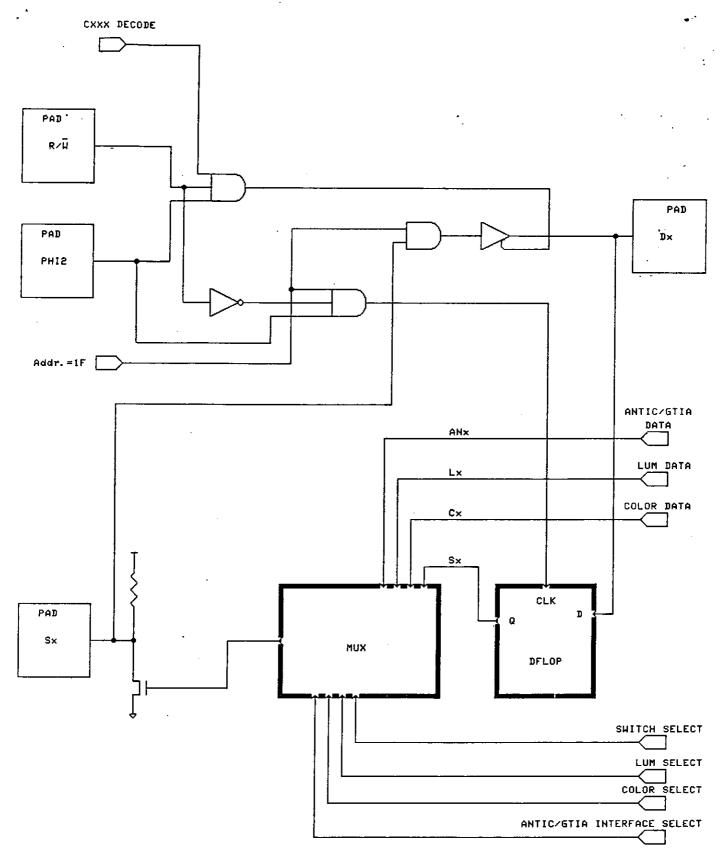

| Figure 12)  | Schematical Representation of the Switch I/O Port53 |     |

|             |                                                     |     |

|                           |                         | DEVICE NUMBER                   | DEVICE NAME |

|---------------------------|-------------------------|---------------------------------|-------------|

| ATARI Semiconductor Group | COMPANY<br>CONFIDENTIAL | C020577 DOCUMENT NUMBER D020577 | CGIA (NTSC) |

|                           | <u></u>                 | 1 0020377                       | 090         |

| <b>A</b>                  |                         |                                 |             |

### General Description

The CGIA is an NMOS custom circuit designed to generate sophisticated playfield and player/missile graphics for display on an NTSC television system. The CGIA converts graphics data stored in system memory into composite video and chrominance information required by a television R.F. modulator. The CGIA also provides four-bits of input from the joystick controllers and four-bits of general purpose I/O.

#### **Features**

- Single-Chip Version of the ANTIC and GTIA Chips

- Software Compatible with ANTIC and GTIA

- All Address Decode for ANTIC and GTIA On-Chip

- Composite Video Output

- Enhanced Color Frequency Generator

- All Graphics Functions On a Single Chip

- Increased System Reliability

# PIN DESCRIPTION

| Pin Name                                                                                            | Туре            | Pin No.                    | Function                                                                                                                                                                                                                                                                                                                                                                |

|-----------------------------------------------------------------------------------------------------|-----------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| osc                                                                                                 | I               | 1.                         | Master clock inputTypically 3.579 MHz.                                                                                                                                                                                                                                                                                                                                  |

| s <sub>0</sub> -s <sub>3</sub>                                                                      | I               | 2-3,5-6                    | Switch I/O lines which are used for general purpose I/O functions.                                                                                                                                                                                                                                                                                                      |

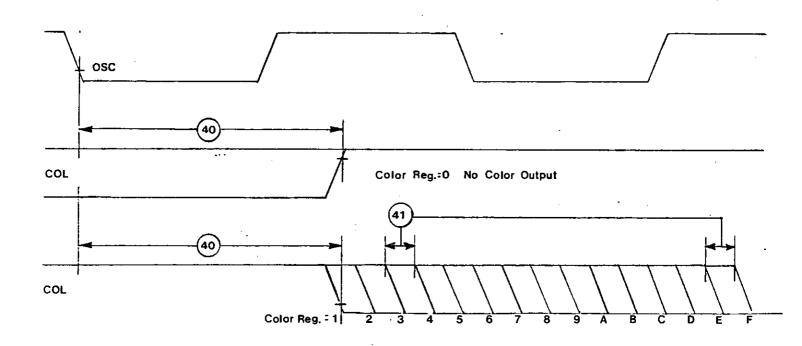

| COL                                                                                                 | 0               | 4                          | Color frequency output signal—This output contains all of the video chroma information. In order to display different colors, the output frequency is shifted in time (phase angle) with respect to the "color burst" reference frequency.                                                                                                                              |

| N/C                                                                                                 | *               | 7                          | Pin not internally connected.                                                                                                                                                                                                                                                                                                                                           |

| v <sub>CC</sub>                                                                                     | I               | 8                          | Positive voltage power supply— Typically +5.0 volts.                                                                                                                                                                                                                                                                                                                    |

| CLUM                                                                                                | <b>o</b> .      | 9                          | Analog video output signal—This output contains all of the video luminance and sync information (composite monochrome signal).                                                                                                                                                                                                                                          |

| T <sub>0</sub> -T <sub>3</sub>                                                                      | I               | 10-13                      | Data input lines which are used to input data from the joystick controllers.  These inputs can be latched by setting a bit in the GRACTL register.                                                                                                                                                                                                                      |

| A <sub>0</sub> -A <sub>4</sub><br>A <sub>5</sub> -A <sub>7</sub><br>A <sub>8</sub> -A <sub>15</sub> | I/0<br>0<br>I/0 | 14,44-47<br>15-17<br>18-25 | Address bus lines which are used to interface to the microprocessor and to system memory. As inputs, the address lines are used to select one of the internal registers of the CGIA. As outputs, the address lines are used to address graphics data stored in system memory and to output RAM refresh addresses.                                                       |

| <sup>D</sup> 0 <sup>-D</sup> 7                                                                      | 1/0             | 26-33                      | Data I/O lines which are used to transfer data to and from the CGIA.                                                                                                                                                                                                                                                                                                    |

| NMI                                                                                                 | 0               | 34                         | Active low output signal which is used to generate a microprocessor non-maskable interrupt. A true condition is generated when there is a display list interrupt, vertical blank occurs, or the RNMI input goes low. Display list interrupts and vertical blank interrupts can be masked by clearing bits in the NMIEN register. The RNMI interrupt cannot be disabled. |

|                     |                         | DEVICE NUMBER   | DEVICE NAME  |  |

|---------------------|-------------------------|-----------------|--------------|--|

|                     | COMPANY<br>CONFIDENTIAL | C020577         | CGIA (NTSC)  |  |

| ATARI'              | CONFIDENTIAL            | DOCUMENT NUMBER |              |  |

| Semiconductor Group |                         | D020577         | PAGE 8 OF 90 |  |

# PIN DESCRIPTION (cont'd)

|                 |             |         | •                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------------|-------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name        | <u>Type</u> | Pin No. | Function                                                                                                                                                                                                                                                                                                                                                                                                  |

| <u>LP</u>       | I           | 35      | Active low input which is used to interface the CGIA with an external light pen. When the LP input makes a high to low transition, the current VCOUNT value is stored in the PENV register. The horizontal position value is stored in the PENH register.                                                                                                                                                 |

| v <sub>ss</sub> | I           | 36      | Power supply ground.                                                                                                                                                                                                                                                                                                                                                                                      |

| RNMI            | I           | 37      | Active low input which is used to generate a non-maskable interrupt (NMI output goes low). The RNMI interrupt cannot be disabled.                                                                                                                                                                                                                                                                         |

| RDY             | 0           | 38      | Output signal which is used to enable and disable the microprocessor. When the RDY line is low, the processor is put into an idle state. When the RDY line is high, the processor is active and enabled to execute                                                                                                                                                                                        |

|                 | ,           |         | program instructions. The RDY line is set<br>low by writing to the WSYNC address, and<br>will continue to stay low until horizontal<br>blank occurs.                                                                                                                                                                                                                                                      |

| REF             | 0           | 39      | Active low output which is used to indicate that the address currently being output on the address lines is to be used for RAM refresh.                                                                                                                                                                                                                                                                   |

| HALT            | 0           | 40      | Active low output control signal which is used to halt the microprocessor during graphics data DMA or RAM refresh.                                                                                                                                                                                                                                                                                        |

| RES             | I           | 41      | Active low input which is used to reset the CGIA. When the RES line is low, bits D and D of the NMIEN register and bits D2-D5 of the DMACTL register are cleared. The CLUM output will be forced into the blank level for as long as the RES line is low. When the RES line makes the transition from low to high, the CLUM and COL lines will output background color until the display list is enabled. |

|                     |              | DEVICE NUMBER   | DEVICE NAME  |

|---------------------|--------------|-----------------|--------------|

|                     | COMPANY      | C020577         | CGIA (NTSC)  |

| ATARI*              | CONFIDENTIAL | DOCUMENT NUMBER |              |

| Semiconductor Group |              | D020577         | PAGE 9 OF 90 |

# PIN DESCRIPTION (cont'd)

| Pin Name   | Type | Pin No. | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------|------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>∮0</b>  | 0    | 42      | Phase zero clock output for the 6502 microprocessor. Phase zero is generated from the OSC clock input and is equal to OSC/2 (typically 1.79 MHz).                                                                                                                                                                                                                                                                                                                                                              |

| R/W        | 1/0  | 43      | Input/output control signal which controls the direction of data transfers between the CGIA, microprocessor, and system memory. As an input, the $R/\overline{W}$ line controls data transfers between the CGIA and the microprocessor. When high, data is transferred from the CGIA to the microprocessor. When low, data is transferred from the microprocessor to CGIA. As an output, the $R/\overline{W}$ line is used to transfer data from system memory to the CGIA $(R/\overline{W})$ is always high). |

| <b>ø</b> 2 | I    | 48      | Phase two microprocessor clock from the 6502 MPU. Phase two is used to synchronize data transfers between the CGIA and microprocessor.                                                                                                                                                                                                                                                                                                                                                                         |

# Key to Pin Types:

I=Input

O=Output

I/O=Input/Output

\*=Undefined Pin Type (pin not used)

|                     |              | DEVICE NUMBER   | DEVICE NAME   |

|---------------------|--------------|-----------------|---------------|

|                     | COMPANY      | C020577         | CGIA (NTSC)   |

| ATARI"              | CONFIDENTIAL | DOCUMENT NUMBER |               |

| Semiconductor Group |              | D020577         | PAGE 10 OF 90 |

#### INTRODUCTION

The CGIA is a custom NMOS LSI device that is capable of accessing graphics data stored in system memory and generating composite video and chroma signals necessary for interfacing to an NTSC video standard television. The CGIA is a single-chip version of the ANTIC (Graphics Processor) and GTIA (Television Interface Adapter) chips. The CGIA is completely software compatible with the ANTIC and GTIA chips. The CGIA requires fewer external components since the address decode for the GTIA has been added on-chip as well as the video D/A for generating composite video (luminance and sync signals). The color frequency generator with external color adjustment has been replaced with an enhanced self-correcting color frequency generator, thereby eliminating the need for external color adjustment.

#### CGIA FUNCTIONAL OVERVIEW

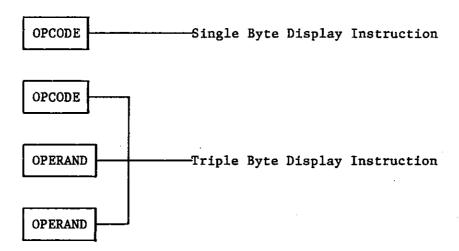

The CGIA is a simple microprocessor. It has a basic instruction set which it uses to generate the graphics on the television screen. Instructions are grouped together in a "display list," similar to a microprocessor program. The display list tells the CGIA how the screen is formatted and how to fetch the graphics data from memory. The CGIA has a program counter register (Display List Pointer) which is used to fetch program instructions. Display list instructions are either single or triple byte instructions.

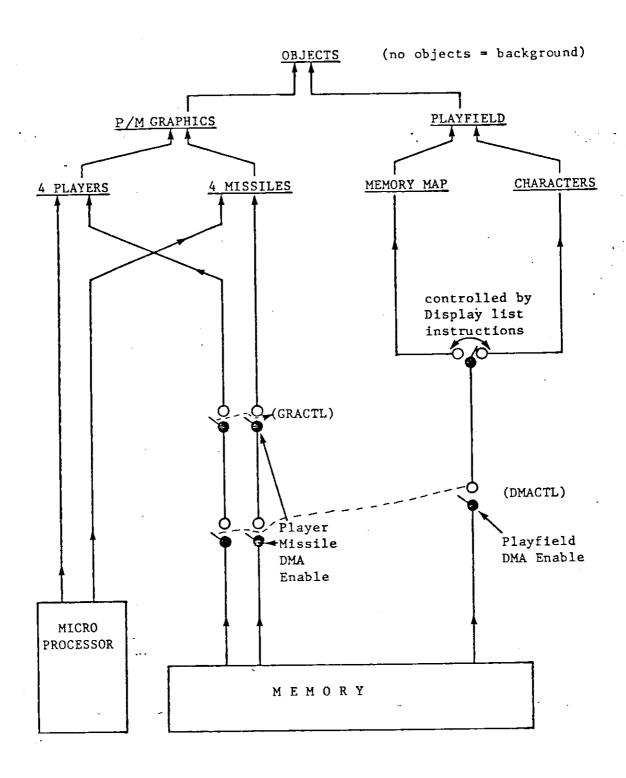

Graphics are divided into two basic categories: playfield graphics and player/missile graphics. The display list has direct control over all playfield graphics. The playfield is generally used for inanimate objects, however, playfield animation is possible. Player/missile graphics are generally used to provide animation for objects that move on the screen.

<u>Playfield Graphics (an overview)</u>—Playfield graphics modes are divided into character—map graphics and bit—map graphics. There are six character—map modes and eight bit—map modes.

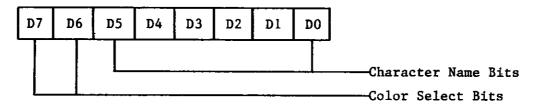

Character-map graphics use a group of pre-defined memory bits to create individual picture elements (pixels) which form a character pattern or "stamp." The character can be recreated or "stamped" on the screen many times without having to reproduce the graphics data in memory every time the character is used. The obvious advantage of character graphics is that it requires less memory to fill a screen. The disadvantage is that the number of characters are limited, therefore the number of different bit patterns are also limited.

Bit-map graphics use bits in memory to define individual pixels on the screen. The advantages and disadvantages of bit-map graphics are exactly the opposite of those for character-map graphics. The advantage is that there is total control of all the pixels on the screen. The disadvantage is that memory bits must be used to define every pixel on the screen therefore, more memory is required for bit-map graphics.

|                     |                         | DEVICE NUMBER   | DEVICE NAME   |

|---------------------|-------------------------|-----------------|---------------|

| 人                   | COMPANY<br>CONFIDENTIAL | C020577         | CGIA (NTSC)   |

| ATARI"              | CONFIDENTIAL            | DOCUMENT NUMBER | ·             |

| Semiconductor Group |                         | D020577         | PAGE 11 OF 90 |

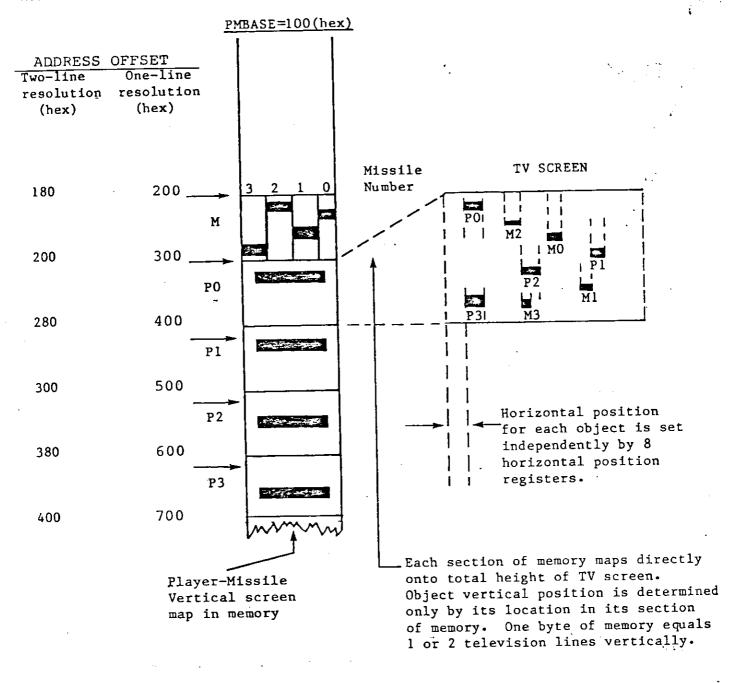

Player/Missile Graphics (an overview)——Player/missile graphics are not controlled by the display list. Players and missiles are defined by individual graphics registers. The graphics information for players and missiles will be the same for every television scan line unless the graphics registers are altered. Player/missile graphics data can be stored in memory and fetch every scan line if player/missile DMA (Direct Memory Access) is enabled. Each player has its own missile and both derive their color and luminance from the same color/lum register. Each player and missile has its own horizontal position register and can be moved in the horizontal direction by simply changing its horizontal position register. This allows players and missiles to be moved horizontally on the screen very easily. Vertical positioning is more difficult because the graphics data (if using DMA) must be moved in memory.

Graphics Mixing—In order to display both the playfield graphics and player/missile graphics on the same screen, both sets of graphics information must be combined. This is accomplished by establishing priority among the different graphics objects. Player/missile graphics are added to the playfield graphics when the horizontal position register for a player or missile equals the count value of the horizontal counter. If the player/missile object has priority over the playfield object, then the overlapping player/missile pixels will be displayed. If the playfield object has priority over the player/missile object, then the overlapping playfield pixels will be displayed. Priority between objects is determined by setting bits in the priority control register (PRIOR).

Object Collisions—When objects overlap, the CGIA records this occurrence in the form of collision detection bits. There are collision detection bits for detecting player to playfield collisions, missile to playfield collisions, player to missile collisions, and player to player collisions. There are however, no collision detection bits for playfield to playfield collisions since this condition cannot exist. The CGIA has no provision for missile to missile collisions.

Input/Output Functions—The CGIA has a four-bit input port for inputting data from the joystick controller trigger buttons and a four-bit general purpose I/O port. Data inputs on the trigger port can be latched by setting a bit in the graphics control register. The trigger inputs will remain latched until the latch enable bit in the graphics control register is reset. The switch I/O port is capable of data input and output. Switch lines are programmed to be either inputs or outputs by writing to the switch I/O output register.

|                     |              | DEVICE NUMBER   | · DEVICE NAME |

|---------------------|--------------|-----------------|---------------|

|                     | COMPANY      | C020577         | CGIA (NTSC)   |

| ATARI"              | CONFIDENTIAL | DOCUMENT NUMBER |               |

| Semiconductor Group |              | D020577         | PAGE 12 OF 90 |

#### CGIA FUNCTIONAL DESCRIPTION

#### 1.0) Television Frame Timing

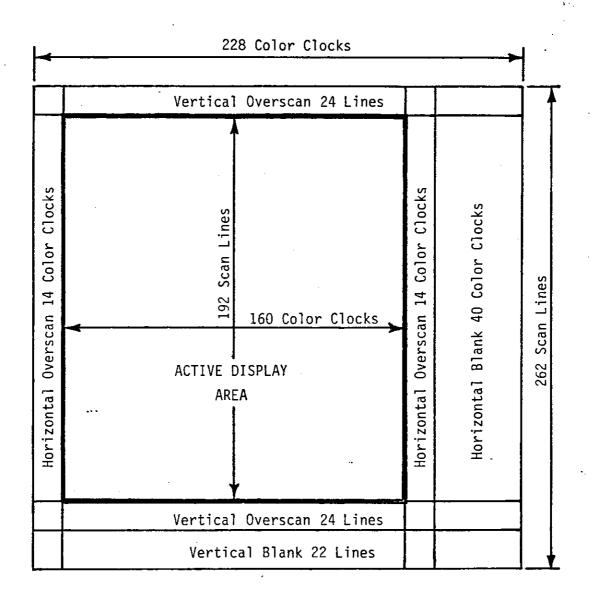

In order to understand how the CGIA works, it is necessary to understand how a television works. An electron beam is generated at the rear of the television tube and shoots toward the television screen in the front. Along the way, it passes through a set of horizontal and vertical coils which, if energized, can deflect the beam. In this way the beam can be made to strike any point on the television screen. The electronics in the television set cause the beam to sweep across the television screen in a regular fashion. The beam's intensity can also be controlled. If the beam is intense, the spot on the screen will glow brightly. If the beam is less intense, the spot will glow dimly or not at all.

The beam starts at the top-left corner of the screen and traces horizontally across the screen. As it sweeps across the screen, its intensity paints an image on the screen. When it reaches the right edge of the screen, it is turned off and brought back to the left side of the screen and down just a little. The beam is turned on again and starts back across the screen. In NTSC systems, this process is repeated for 262 sweeps across the screen. These 262 lines fill the screen from top to bottom to make a complete field. At the bottom of the screen (after the 262nd line), the beam is turned off and returned to the top-left corner of the screen. This process happens 60 times every second. Since the picture is drawn so fast, the eye does not notice that the television picture is being drawn one line at a time. All televisions use a technique called "interlacing." This technique increases the vertical resolution by drawing half of the television picture in the first 262 lines and the second half of the picture in the second 262 lines. The second half of the picture is moved down by one half of a scan line so the two picture halves are not displayed on top of each other. The CGIA does not do interlacing so the picture is the same for every field.

Terminology—A single trace of the beam across the screen is referred to as a "horizontal scan line." A horizontal scan line is the fundamental unit of measurement of vertical distance on the screen. The height of an image is stated by specifying the number of horizontal scan lines it spans. The period during which the beam returns from the right edge of the screen to the left side is referred to as "horizontal blank." The period during which the beam returns from the bottom-right edge of the screen to the top-left is referred to as "vertical blank." The entire process of drawing a screen takes 16,666 microseconds. The vertical blank period is about 1,400 microseconds. The horizontal blank period is about 11.16 microseconds. A single horizontal scan line takes approximately 64 microseconds (this includes the horizontal blank time).

|                     |                         | DEVICE NUMBER   | DEVICE NAME   |

|---------------------|-------------------------|-----------------|---------------|

|                     | COMPANY<br>CONFIDENTIAL | C020577         | CGIA (NTSC)   |

| ATARI'              | CONFIDENTIAL            | DOCUMENT NUMBER |               |

| Semiconductor Group |                         | D020577         | PAGE 13 OF 90 |

# 1.0) Television Frame Timing (cont'd)

Most television sets are designed with "overscan." This means that the television picture is spread out so the picture edges are off the edge of the television tube. This guarantees that there will not be any unsightly borders in the television picture. For this reason the picture must be somewhat smaller than the television can theoretically display. This overscan can vary from television to television. A good limit of vertical resolution to use is 192 horizontal scan lines.

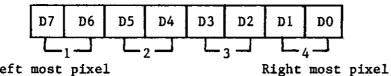

The standard unit of horizontal distance is the "color clock." The width of an image is specified by stating how many color clocks wide it is. There are a total of 228 color clocks in a single horizontal scan line. Only 160 of these are actually visible due to horizontal blank and horizontal overscan. It is possible with the CGIA to go even finer and control individual half clocks. This gives double the horizontal resolution or 320 visible picture elements. A picture element, either vertical or horizontal, is referred to as a "pixel." The maximum visible resolution of a television picture using the CGIA is 320 pixels horizontally by 192 pixels vertically. Figure 1 illustrates the screen format as generated by the CGIA.

|                     |                         | DEVICE NUMBER   | DEVICE NAME   |

|---------------------|-------------------------|-----------------|---------------|

|                     | COMPANY<br>CONFIDENTIAL | C020577         | CGIA (NTSC)   |

| ATARI'              | CONFIDENTIAL            | DOCUMENT NUMBER |               |

| Semiconductor Group |                         | D020577         | PAGE 14 OF 90 |

Figure 1) Television Screen Format

|                     |              | DEVICE NUMBER   | DEVICE NAME   |

|---------------------|--------------|-----------------|---------------|

|                     | COMPANY      | C020577         | CGIA (NTSC)   |

| ATARI'              | CONFIDENTIAL | DOCUMENT NUMBER |               |

| Semiconductor Group |              | D020577         | PAGE 15 OF 90 |

#### 2.0) THE DISPLAY LIST

The display list is a sequence of display instructions stored in memory. These instructions are either one byte or three bytes long. The display list can be considered a display program and the display list pointer that fetches these instructions can be thought of as a display program counter. (6 bit base register plus 10 bit counter).

The display list counter can be initialized by writing to DLISTH and DLISTL. Once initialized, this counter value is used to address the display list, fetch the instruction, display one to sixteen lines of data on the TV screen, increment the display list pointer, fetch the next display instruction, and so on automatically without microprocessor control. DLISTL and DLISTH should be altered only during vertical blank or when DMA is disabled (see DMACTL).

Each instruction defines the type (character map or bit map) and the resolution (size of bits on the screen) and the location of data in memory to be displayed for a group (1 to 16) lines. Each group of lines is called a display block or mode line.

Note: The top 6 bits of the display list pointer are latches only and have no count capability, therefore the display list cannot cross a 1K byte memory boundary unless a jump instruction is used.

## 2.1) Display Instruction Format

Each instruction consists of either an opcode only, or of an opcode followed by two bytes of operand.

The opcode is always fetched first and placed in the <u>Display Instruction</u> Register. This opcode defines the type of instruction (1 or 3 bytes) and will cause two more bytes to be fetched if needed. If fetched, these next two bytes will be placed in the memory scan counter, or in the display list counter.

|                     | •            | DEVICE NUMBER   | DEVICE NAME   |

|---------------------|--------------|-----------------|---------------|

|                     | COMPANY      | C020577         | CGIA (NTSC)   |

| ATARI               | CONFIDENTIAL | DOCUMENT NUMBER |               |

| Semiconductor Group |              | D020577         | PAGE 16 OF 90 |

# 2.1) Display Instruction Format (cont'd):

Display Instruction Register (IR)— This register is loaded with the opcode of the current display list instruction. It cannot be accessed directly by the programmer. There are three basic types of display list instructions: blank, jump, and display.

Blank (1-byte)

| 06 D5 D4 | 0 | 0 | 0 | 0 |

|----------|---|---|---|---|

|----------|---|---|---|---|

This instruction is used to create 1 to 8 blank lines on the display (background color used).

D6-D4 0-7 = 1-8 blank lines D3-D0 0 = Blank

Jump (3-bytes)

| D6 | х | х | 0 | 0 | 0 | 1 |

|----|---|---|---|---|---|---|

This instruction is used to reload the Display List Counter. The next two bytes specify the address to be loaded (LSB first).

D6 0 = Jump (creates one blank line on display)

1 = Jump and wait until end of next vertical blank

D3-D0 1 = Jump

Display (1 or 3 bytes)

| D7 D6 D5 D4 D3 D2 I | D1 D0 |

|---------------------|-------|

|---------------------|-------|

This instruction specifies the type of display for the next display block.

D6 0 = 1 byte instruction

1 = 3 byte instruction (reload Memory Scan Counter

using address in next two bytes, LSB first)

D5 1 = Vertical scroll enable

D4 1 = Horizontal scroll enable

D3-D0 2-F = Graphics mode select (bit map or character map)

Bit D7 of a display list instruction can be set to create a display list interrupt, if bit D7 of the NMIEN register is set. Display list interrupts can be used to change the color registers or graphics during the middle of the TV display. The type of interrupt is determined by checking the NMIST register. The NMIRES register clears the NMIST register.

Bits D5 and D4 of a display list instruction are used to enable vertical and horizontal scrolling. The amount of scrolling depends on the values in the VSCROL and HSCROL registers. Figure 2 lists the CGIA display list opcodes.

|                     |                         | DEVICE NUMBER   | DEVICE NAME   |

|---------------------|-------------------------|-----------------|---------------|

|                     | COMPANY<br>CONFIDENTIAL | C020577         | CGIA (NTSC)   |

| ATARI*              | CONFIDENTIAL            | OCCUMENT NUMBER |               |

| Semiconductor Group |                         | D020577         | PAGE 17 OF 90 |

| Horizontal Scroll<br>Vertical Scroll<br>Load MSC (3 Byte)<br>Display List Interrupt | Blank 1 Scan Line<br>Blank 2 Scan Lines<br>Blank 3-7 Scan Lines<br>Blank 8 Scan Lines | Jump (3 Byte) Jump and Wait for Vert. Blank (3 Byte) Character Map Display Instructions            | Bit Map Display<br>Instructions                                                                | ** = 20,30,40,50,60<br>Respectively<br>## = A0,B0,C0,D0,E0<br>Respectively                          |

|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

|                                                                                     |                                                                                       | F2<br>F3<br>F5<br>F7                                                                               | F8<br>FB<br>FB<br>FC<br>FC<br>FE                                                               |                                                                                                     |

| ×××                                                                                 |                                                                                       | E2<br>E3<br>E4<br>E5<br>E6                                                                         | 88 E E E E E E E E E E E E E E E E E E                                                         |                                                                                                     |

|                                                                                     |                                                                                       | D2<br>D3<br>D4<br>D5<br>D6                                                                         | 000 000 000 000 000 000 000 000 000 00                                                         | Line                                                                                                |

| ××                                                                                  |                                                                                       | C2<br>C3<br>C4<br>C5<br>C5<br>C7                                                                   | 86988888                                                                                       | ayfield Types)<br>Standard Mode Line                                                                |

| XX X                                                                                |                                                                                       | B2<br>B3<br>B4<br>B5<br>B6                                                                         | BB<br>BB<br>BB<br>BB<br>BB<br>BB                                                               | Scan Lines Per Pixel<br>ors (Background and Playfield Types)<br>racters or Pixels Per Standard Mode |

| ××                                                                                  |                                                                                       | A2<br>A3<br>A4<br>A5<br>A7                                                                         | AB<br>AB<br>AB<br>AB<br>AB<br>AB                                                               | fiel                                                                                                |

| × ×                                                                                 |                                                                                       | 92<br>93<br>94<br>95<br>96                                                                         | 98<br>99<br>90<br>90<br>90<br>90                                                               | Play<br>r St                                                                                        |

| XX                                                                                  | 80<br>90<br>##<br>F0                                                                  | 81<br>C1<br>82<br>83<br>84<br>85<br>86                                                             | 88<br>89<br>88<br>88<br>88<br>88<br>88<br>88<br>88<br>88                                       | ixel<br>and<br>s Pe                                                                                 |

| # # # # # # # # # # # # # # # # # # #                                               |                                                                                       | 72<br>73<br>74<br>75                                                                               | 78<br>79<br>78<br>78<br>70<br>70<br>7E                                                         | Scan Lines Per Pixel<br>ors (Background and Pl<br>racters or Pixels Per                             |

| XXX                                                                                 |                                                                                       | 62<br>63<br>64<br>65<br>66                                                                         | 68<br>69<br>68<br>60<br>60<br>60<br>60<br>60                                                   | es P<br>kgro<br>or P                                                                                |

| X X                                                                                 |                                                                                       | 52<br>53<br>54<br>55<br>56                                                                         | 58<br>54<br>55<br>56<br>57<br>57<br>58                                                         | Lin<br>(Bac)                                                                                        |

| ××                                                                                  |                                                                                       | 44<br>44<br>45<br>46                                                                               | 48<br>49<br>40<br>40<br>40<br>4E                                                               | Scan Lir<br>ors (Bac<br>racters                                                                     |

| ××                                                                                  |                                                                                       | 32<br>33<br>34<br>35<br>36                                                                         | 38<br>34<br>35<br>35<br>35<br>35<br>35<br>35                                                   | TV<br>Colo                                                                                          |

| ×                                                                                   | :                                                                                     | 22<br>23<br>24<br>25<br>26                                                                         | 28<br>29<br>20<br>20<br>20<br>21<br>21<br>21                                                   | Jo L                                                                                                |

| ×                                                                                   |                                                                                       | 12<br>13<br>14<br>15<br>16                                                                         | 18<br>19<br>10<br>10<br>11<br>11<br>11                                                         | Number<br>Number<br>Number                                                                          |

|                                                                                     | 00<br>10<br>70                                                                        | 01<br>41<br>02<br>03<br>04<br>05<br>06                                                             | 05 00 00 00 00 00 00 00 00 00 00 00 00 0                                                       | ĪĀĀĀ                                                                                                |

| HSCROL<br>VSCROL<br>LD MEM SCAN<br>INST INTERRUPT                                   | BLK 1 2 3-7 8                                                                         | JMP<br>JVB<br>CHR (40,2,8)<br>" (40,2,10)<br>" (40,4,8)<br>" (40,4,16)<br>" (20,5,8)<br>" (20,5,8) | BIT (40,4,8) " (80,2,4) " (80,4,4) " (160,2,2) " (160,2,1) " (160,4,2) " (160,4,1) " (320,2,1) |                                                                                                     |

Figure 2) Display List Instruction Opcodes

|                     | ·            |                 |               |

|---------------------|--------------|-----------------|---------------|

|                     |              | DEVICE NUMBER   | DEVICE NAME   |

|                     | COMPANY      | C020577         | CGIA (NTSC)   |

| ATARI"              | CONFIDENTIAL | DOCUMENT NUMBER |               |

| Semiconductor Group |              | D020577         | PAGE 18 OF 90 |

#### 2.2) Memory Scan Counter

The memory scan counter is not directly accessible by the programmer. It is loaded with the value in the last 2 bytes of a 3 byte (non-jump) display list instruction.

This counter points to the location in memory where the graphics data to be directly displayed (bit map modes) is stored, or to the location of character name strings to be indirectly displayed (character map modes), on the television screen.

A single byte instruction does not reload this counter. This implies a continuation in memory of the data to be displayed from that displayed by the previous instruction. Since this counter consists of 4 bits of register and 12 of actual counter, a continuous memory block of display data can not cross a 4K byte memory boundary unless the counter is repositioned with a 3 byte Load Memory Scan counter display instruction.

### 2.3) Vertical and Horizontal Fine Scrolling

Playfield objects are difficult to move smoothly. Memory map playfield can be moved by rewriting sections of memory. This is extremely time consuming if large sections of the screen must be moved smoothly. Character playfield objects can be moved easily in a rough fashion by changing the memory scan counter. This results in a large position jump from one character position to another. For this reason, the CGIA provides two registers (VSCROL and HSCROL) which allow smooth horizontal or vertical motion of up to one character width horizontally and up to one character height vertically. After this much smooth motion has been done, memory is rewritten or the memory scan counter is modified and smooth motion is resumed for another character distance.

Horizontal Scrolling-Only playfield and not players and missiles are scrolled when scrolling is enabled. Horizontal scrolling is enabled by setting display instruction bit D4 to a one. When horizontal scrolling is enabled, the display is shifted to the right by the number of color clocks specified by the contents of HSCROL. More bytes of data are needed for horizontal scrolling than normal. For a narrow playfield, there should be the same number of bytes per line as for standard playfield and no scrolling. Similarly, for standard playfield, the same number of bytes are required as for the wide playfield. For wide playfield, there is no change in the number of bytes and background color is shifted into the vacant locations.

Vertical Scrolling--A zone of playfield on the screen can be scrolled upward by using VSCROL and bit D5 of the display list instruction. The display blocks at the upper and lower boundaries of the zone must have variable vertical size. In particular, the first display block within that zone must be shortened for the top, and the last display block must be shortened from the bottom (i.e. not all of the top and bottom blocks will be displayed).

|                     |              | DEVICE NUMBER   | DEVICE NAME   |

|---------------------|--------------|-----------------|---------------|

|                     | COMPANY      | C020577         | CGIA (NTSC)   |

| ATARI"              | CONFIDENTIAL | DOCUMENT NUMBER |               |

| Semiconductor Group |              | D020577         | PAGE 19 OF 90 |

# 2.3) Vertical and Horizontal Fine Scrolling (cont'd)

The vertical dimension of each display block is controlled by a 4-bit counter within the CGIA called the "Delta Counter" (DCTR). Without vertical scrolling, it starts at zero on the first line and counts up to a standard value which is determined by the current display instruction. (Ex: For upper and lower case text display, the end value is 9. For 5 color character displays, it is 7 or 15.)

If bit D5 of the instruction remains unchanged between consecutive display blocks, the second block is displayed in the normal fashion. If bit D5 of the instruction goes from 1 to 0 between two consecutive display blocks, the second block will start with DCTR = 0, as usual, but will count up until DCTR = VSCROL, instead of the standard value. This shortens that display block from the bottom.

To define a vertically scrolled zone, the most direct method is to set bit D5 to a one in the first display instruction for that zone and in all consecutive blocks but the last one. If the VSCROL register is not rewritten on the fly, this results in a total scrolled zone that has a constant number of lines (provided that the VSCROL value does not exceed the standard individual block size). If N is the standard block size, the top block will be N - VSCROL lines (N is greater than VSCROL), and the last block will be VSCROL + 1 lines: (N - VSCROL) + (VSCROL + 1) = N + 1. Figure 3 is an example of a scrolled zone, top block, for 8 VSCROL values for N=8.

| The contract of the contract o |              | DEVICE NUMBER   | DEVICE NAME |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----------------|-------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | COMPANY      | C020577         | CGIA (NTSC) |

| ATARI'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | CONFIDENTIAL | DOCUMENT NUMBER |             |

| Semiconductor Group                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |              | D020577         | PAGE 20     |

| oit 5 =Ø                                    | VSCROL=Ø                          | VSCROL=1        | VSCROL=2                   | VSCROL=3              | VSCROL=4                                  | vscrol=5                             | vscrot=6                             | VSCROL≂7         |

|---------------------------------------------|-----------------------------------|-----------------|----------------------------|-----------------------|-------------------------------------------|--------------------------------------|--------------------------------------|------------------|

| 2x8+1=17 == = = = = = = = = = = = = = = = = | 0 1<br>2<br>3<br>4<br>5<br>6<br>7 | 2 3 4 5 6 7 O I | 2<br>3<br>4<br>5<br>6<br>7 | 7                     | 4<br>5<br>6<br>7<br>0<br>1<br>2<br>3<br>4 | 5<br>6<br>7<br>0<br>2<br>3<br>4<br>5 | 6<br>7<br>0<br>1<br>2<br>3<br>4<br>5 | 7                |

| 2×6 = 1 = 1 = 0                             | 2<br>3<br>3<br>4<br>5<br>6        | 2 3 4 5 6 7 0   | 5<br>5<br>6<br>7<br>0      | 5<br>4<br>5<br>6<br>7 | 5<br>7<br>0<br>1<br>2<br>3                | 6<br>7<br>0<br>1<br>2<br>3<br>4<br>5 | 7 0 1 2 3 4 5 6                      | 22 33 44 55 66 7 |

Figure 3) Vertical Scrolling Example

|                     |              | DEVICE NUMBER   | DEVICE NAME   |

|---------------------|--------------|-----------------|---------------|

|                     | COMPANY      | C020577         | CGIA (NTSC)   |

| ATARI"              | CONFIDENTIAL | DOCUMENT NUMBER |               |

| Semiconductor Group |              | ·D020577        | PAGE 21 OF 90 |

# 2.4) Simple Display List Example

The following display list example attempts to show how to create a display list for a character graphics mode 2 display screen. The DMACTL register is configured for a standard width playfield and display list instruction DMA enabled. This will allow a total of 40 characters per mode line with 24 mode lines per screen. The display list starts at address 1000 (HEX). DLISTH and DLISTL must already be set to 1000. Character names for the display are stored at address 1100 (HEX).

Graphics Mode 2 Display List Example (40 characters by 24 lines)

| Address | Data     | Comments                                                                                            |

|---------|----------|-----------------------------------------------------------------------------------------------------|

| 1000    | 70       | ·                                                                                                   |

| 1001    | 70       | Display 24 blank lines (output background color).                                                   |

| 1002    | 70       |                                                                                                     |

| 1003    | 42 00 11 | Reload MSC with 1100 (starting address of character name data) and display one Mode 2 display line. |

| 1006    | 02       |                                                                                                     |

| 1007    | 02       |                                                                                                     |

| 1008    | 02       |                                                                                                     |

| 1009    | 02       |                                                                                                     |

| 100A    | 02       |                                                                                                     |

| 100B    | 02       |                                                                                                     |

| 100C    | 02       |                                                                                                     |

| 100D    | 02       |                                                                                                     |

| 100E    | 02       | ·                                                                                                   |

| 100F    | 02       |                                                                                                     |

| 1010    | 02       |                                                                                                     |

| 1011    | 02       |                                                                                                     |

| 1012    | 02       | Display 23 more Mode 2 display lines.                                                               |

| 1013    | 02       |                                                                                                     |

| 1014    | 02       |                                                                                                     |

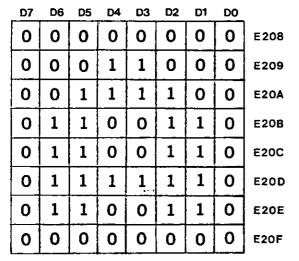

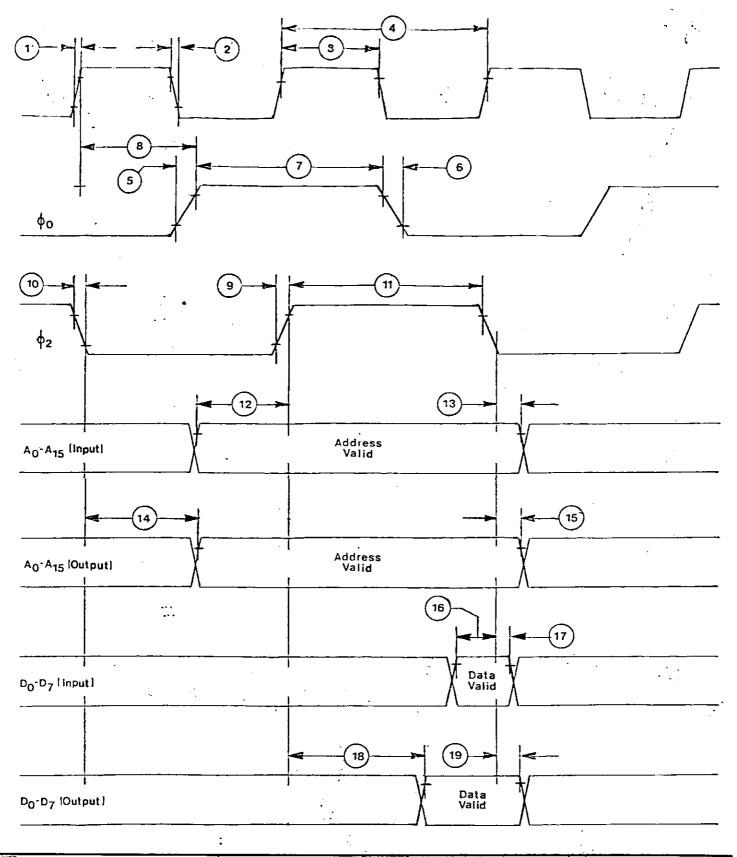

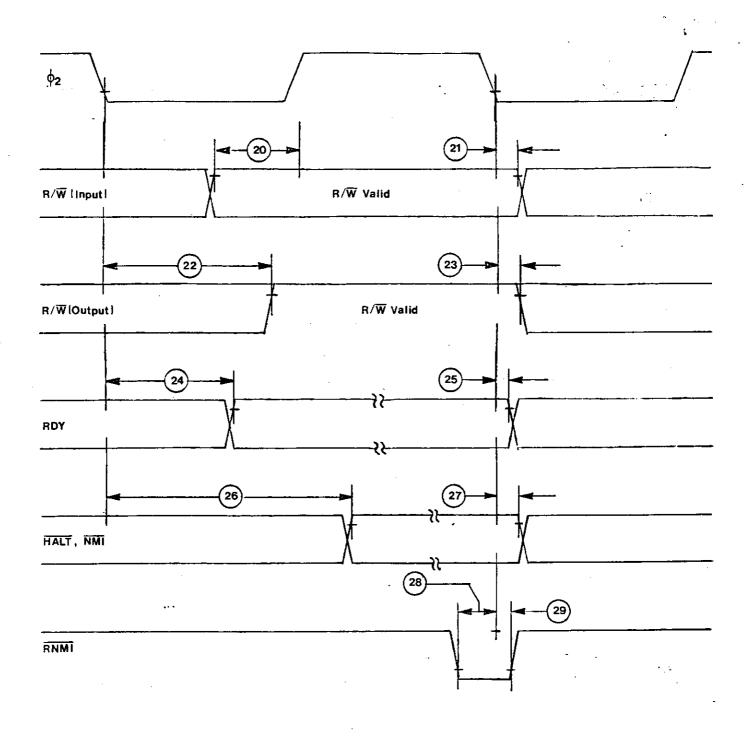

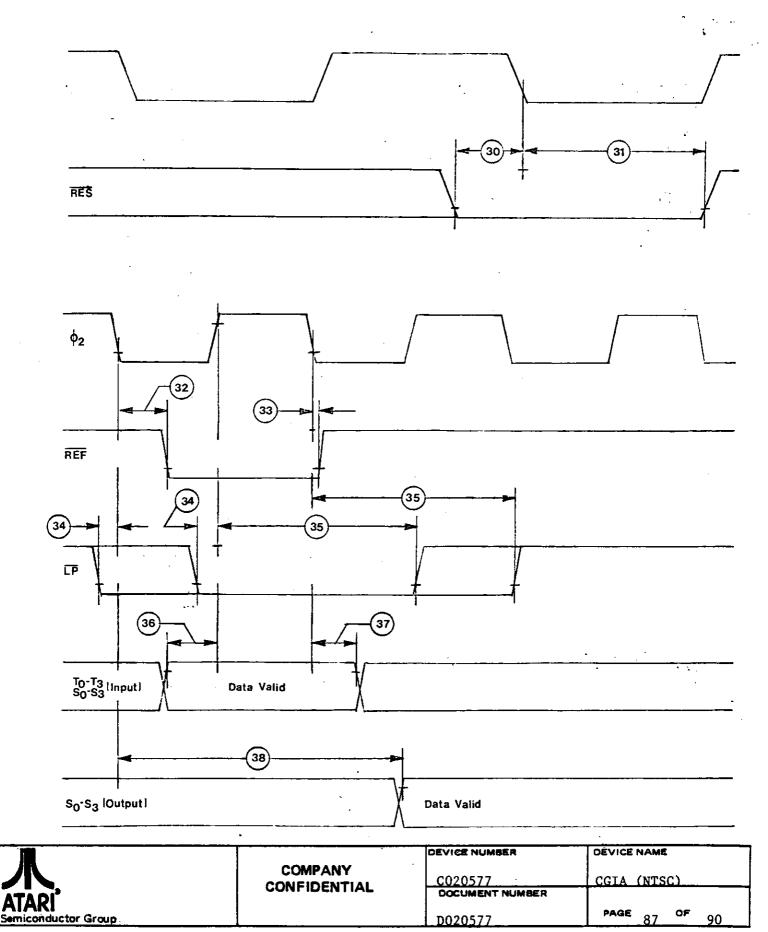

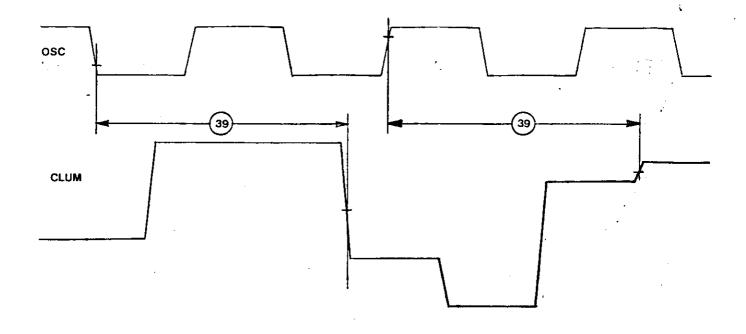

| 1015    | 02       |                                                                                                     |